Fターム[2H092JA33]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545) | 厚さ規定 (269)

Fターム[2H092JA33]に分類される特許

161 - 180 / 269

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

半導体装置及び電子機器

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイン電極に接触しない。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3原子%〜1.2原子%、Co:0.05原子%〜2.0原子%、Laおよび/またはNd:0.1原子%〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的とする。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法

【課題】単純化された工程を通じて表示能力が優れた薄膜トランジスタ基板を製造する方法に関する。

【解決手段】画面表示部と周辺部とを含む基板の上にゲート配線をITOまたはIZOとの接触特性が良好な下部金属膜と低抵抗上部金属膜との二重膜構造で形成し、ゲート絶縁膜、半導体層、接触層を連続蒸着する。次いで、二重膜構造のデータ配線及びその下部の接触層パターンを形成する。保護膜を蒸着した後、その上に感光膜を塗布し、その次、画面表示部の透過率と周辺部の透過率とが異なる一つ以上のマスクを用いて感光膜を露光・現像して部分に応じて厚さが異なる感光膜パターンを形成する。このような感光膜パターンを通じて保護膜及びその下部の膜をエッチングして半導体パターン及び接触窓を形成し、その上にITOまたはIZOで画素電極と補助ゲートパッド及び補助データパッドを形成する。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層、ソース領域及びドレイン領域を酸化物半導体層とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のための加熱処理)を行う。かつ、加熱処理を行った酸化物半導体層を酸素雰囲気下で徐冷する。

(もっと読む)

TFT−LCDアレイ基板及びその製造方法

【課題】基板に形成された複数のゲートライン及び複数のデータラインを含み、ゲートラインとデータラインにより複数の画素領域が画定され、画素領域ごとに画素電極及びスイッチング素子としての薄膜トランジスタが形成されるTFT−LCDアレイ基板を提供する。

【解決手段】本発明は、TFT−LCDアレイ基板及びその製造方法に関する。アレイ基板には、基板に形成された複数のゲートライン及び複数のデータラインが含まれる。前記ゲートラインとデータラインにより複数の画素領域が画定され、画素領域ごとに画素電極及びスイッチング素子としての薄膜トランジスタが形成されている。前記薄膜トランジスタのゲート電極は連結電極を介して対応したゲートラインに電気的に接続され、前記ゲート電極と前記ゲートラインは異なる材料層により形成される。

(もっと読む)

電気光学装置

【課題】コンタクトホールと、反射電極のための凹凸とが同時に形成された電気光学装置を提供する。

【解決手段】同一フォトマスクを用いたことにより、コンタクトホールと、反射電極のための凹凸とは同時に形成される。凹凸を形成するためのフォトマスクが有する遮光部又は透光部を上面から見ると、複数の円、複数の楕円、複数の正方形、複数の長方形が備えられており、これらは大きさが異なり、且つ互いの距離が異なる。

(もっと読む)

半導体装置及びその製造方法、並びに液晶表示装置

【課題】光センサーと遮光膜を有する半導体装置において、段切れや膜剥がれに起因にする歩留まりの低下を防止することができるとともに、暗電流の増大を防止して光センサーの性能の低下を防止することができる半導体装置及びその製造方法、並びに液晶表示装置を提供することを目的とする。

【解決手段】フォトダイオード15を構成するポリシリコン膜を形成する部分Bの非晶質シリコン膜30の厚みW1が、遮光膜28の周縁に対応した部分Aの非晶質シリコン膜30の厚みW2より薄くなるように、非晶質シリコン膜30を薄膜化する。そして、非晶質シリコン膜30にレーザー光を走査して、非晶質シリコン膜30を多結晶化させてポリシリコン膜を形成する。

(もっと読む)

表示装置及びその製造方法

【課題】 移動度特性及び特性安定性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 基板上に、ゲート電極と、ゲート絶縁膜と、半導体膜と、ソース電極及びドレイン電極として機能する一対の電極とを具備し、少なくとも前記ソース電極及びドレイン電極の一部が前記半導体膜を挟んで前記ゲート絶縁膜の反対側に位置する薄膜トランジスタを有する表示装置であって、前記半導体膜は、1−8nmの厚さの微結晶Si膜と、前記微結晶Si膜の前記ゲート絶縁膜側とは反対側に位置する非晶質Si膜とを含む積層からなる。

(もっと読む)

表示駆動用基板、表示装置、及び表示駆動用基板の製造方法

【課題】歩留まりを改善した表示駆動用基板を提供する。

【解決手段】表示領域12にマトリクス状に設けられた複数の画素回路11と、表示領域12の各行に設けられ、対応行の各画素回路11に共通に接続されたゲート線と、各ゲート線に接続されたゲートドライバ13と、前記各ゲート線の延長部に設けられたゲートドライバ接続端子15とを備える表示駆動用基板10が、集合基板1上に複数形成されている。表示駆動用基板10は、さらに、電気的に接続された状態から電気的に切断された状態へ変更できる切断部14を備えてもよい。

(もっと読む)

基板、表示パネル、表示パネルの修正方法

【課題】参照配線や参照幹線に不良があった場合であっても、表示欠陥を防止できる基板、この基板を備える表示パネル、表示パネルの修正方法を提供すること。

【解決手段】参照配線113aに不良の有無を検出する工程と、不良が検出された場合には不良参照配線113sを特定して不良箇所Sを特定する工程とを有するとともに、不良が断線である場合には、不良参照配線113sと予備配線124とを短絡する工程と、不良参照配線113sが伝送する信号と同じ信号を伝送する所定の参照配線113mと予備配線124とを短絡する工程とを有し、不良が他の導体との短絡である場合には、不良参照配線113vの不良箇所Uの前後両側の箇所を切断する工程と、不良参照配線113vと予備配線124とを短絡する工程と、不良参照配線113vが伝送する信号と同じ信号を伝送する所定の参照配線113wと予備配線124とを短絡する工程とを有する。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

半透過性膜、表示デバイス、及びパターン基板の製造方法

【課題】生産性が向上し、かつ特性が良好な半透過性膜、表示デバイス、及びパターン基板の製造方法を提供することを目的とする。

【解決手段】本発明にかかる半透過性膜は、光学特性として光の透過特性と反射特性とを有する半透過性膜である。半透過性膜は、アルミニウム又はアルミニウムを主成分とする合金のいずれかに少なくとも40mol%以上50mol%未満の窒素を含む窒素含有膜である。また、半透過性膜は、上記の窒素含有膜と金属膜との積層膜とすることも可能である。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層の高導電率化工程やソース電極及びドレイン電極のエッチング工程において、半導体層にダメージを与えないような薄膜トランジスタ及びこれを用いた液晶表示装置を提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の向こう側にソース電極又はドレイン電極が形成されてなるトップゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、紫外線の表面照射によって照射された半導体層部分を高導電率化するため、半導体層へのダメージが生じない。従って、高導電率化工程及びエッチング工程のいずれにおいても半導体層はダメージを受けることがないため信頼性が向上する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

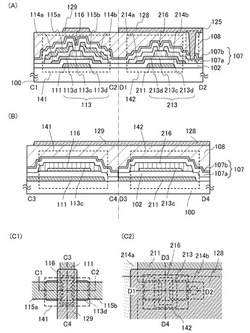

半導体装置及びその作製方法

【課題】薄膜トランジスタのチャネルが形成される領域を含む半導体層と、ソース電極層及びドレイン電極層のコンタクト抵抗(接触抵抗)が小さい薄膜トランジスタを提供することを課題の一とする。また、配線の電気抵抗が小さい薄膜トランジスタを提供することを課題の一とする。また、ソース電極層及びドレイン電極層の端部に生じる段差の少なくとも一部を覆う半導体層をキャリアが滞りなく移動できる構造を有する薄膜トランジスタを提供することを課題の一とする。

【解決手段】薄膜トランジスタを形成するにあたって、第1電極層上に第1配線層を設け、第2電極層上に第2配線層を設け、第1電極層が第1配線層の端部から延在し、第2電極層が第2配線層の端部から延在し、第1電極層の側面及び上面と第2電極層の側面及び上面に半導体層が電気的に接続するように設ける。

(もっと読む)

電気光学装置及び電気光学装置の製造方法

【課題】電極における線状電極部を精度良く残すとともに、開口部における残渣の発生を抑制することが可能な電気光学装置を提供すること。

【解決手段】共通電極における開口部46(間隙部分)には、共通電極を形成する際に、絶縁層76よりもITO膜の結晶化を抑制させる物質からなる下地層46が形成されている。つまり、下地層46が形成された間隙となる部分におけるITO膜の結晶粒子は、絶縁層76上におけるITO膜の結晶粒子よりも小さくなっている。よって、透明電極材料としてのITO膜をエッチングする際に、間隙となる部分におけるエッチングレートは、絶縁層76上におけるエッチングレートより高くなるため、下地層46上のITO膜を選択的に除去することができる。従って、電極における線状電極部を精度良く残すとともに、開口部における残渣の発生を抑制することができる。

(もっと読む)

161 - 180 / 269

[ Back to top ]