Fターム[2H092JA33]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 半導体層 (1,729) | 大きさ (545) | 厚さ規定 (269)

Fターム[2H092JA33]に分類される特許

121 - 140 / 269

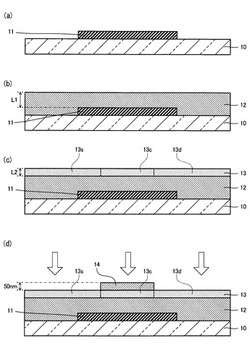

薄膜トランジスタとその製造方法と電気光学装置と電子機器

【課題】 非晶質シリコンTFTの特性を大幅に向上させつつ、その製造プロセスにおける膜飛びを抑制する。

【解決手段】まず、基板10上にゲート電極11を形成する。次に、基板10上に、ゲート電極11を平面視で覆うゲート絶縁膜12を形成し、その上に、チャネル領域13cとソース領域13sとドレイン領域13dとを有する非晶質の半導体膜13を形成し、その上に、チャネル領域13cを平面視で覆うチャネル保護層14を形成する。次に、半導体膜13とチャネル保護層14とにレーザーを照射することにより、チャネル領域13cを微結晶化する。次に、半導体膜13上に、チャネル保護層14を平面視で覆い、ソース領域13sとドレイン領域13dとに平面視で重なる導電膜を形成する。次に、導電膜をエッチングしてソース電極16sとドレイン電極16dとを形成する。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法

【課題】誤整列を少なくすることができると共に開口率を確保することができる液晶表示装置用薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】液晶表示装置用薄膜トランジスタ基板は、絶縁基板の上に形成されているデータ配線と、画素に形成されている赤、緑、青のカラーフィルターと、データ配線及びカラーフィルターを覆う絶縁膜と、データ線と交差して画素を定義するゲート線及びゲート線に連結されたゲート電極を含むゲート配線と、ゲート配線を覆っており絶縁膜と共にデータ線の一部を露出させる第1接触孔を有するゲート絶縁膜と、ゲート電極のゲート絶縁膜の上部に形成されている半導体層パターンと、第1接触孔を通じてデータ線と連結されているソース用電極とゲート電極を中心にしてソース用電極と分離されて対向するドレーン用電極とドレーン用電極と連結されており画素に形成されている画素電極とを含む画素配線を含む。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

液晶表示装置

【課題】正確な表示を行う表示装置を提供することを課題とする。

【解決手段】オフ電流の低い酸化物半導体を有するトランジスタを用いて、回路を構成する。回路として、画素回路の他に、プリチャージ回路または検査回路を形成する。酸化物半導体を用いているため、オフ電流が低く、そのため、プリチャージ回路や検査回路において、信号や電圧が漏れて、表示に不具合を起こすという可能性が低い。その結果、正確な表示を行う表示装置を提供することが出来る。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに表示装置

【課題】 ソース・ドレイン電極と半導体膜との接触抵抗を低減し、移動度特性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 板上に形成されたゲート電極と、前記ゲート電極を覆うようにして前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体膜と、少なくとも各々の一部が前記半導体膜上に形成され、ソース電極及びドレイン電極として機能する一対の電極と、を具備する薄膜トランジスタであって、前記半導体膜は、GeあるいはSi及びGeを含有し、前記一対の電極の各々は、ボロンあるいはV族元素を含有する金属膜で形成され、前記一対の電極の各々と前記半導体膜との間に、ジャーマノシリサイドあるいは金属−Ge間化合物が形成されている。

(もっと読む)

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

電気光学装置の作製方法

【課題】電気光学装置の作製工程においてマスク枚数を追加することなく、反射電極の散乱構造を作製する。

【解決手段】層間膜に感光性樹脂膜を用いる。フォトマスク100の第1の透光部101を通して露光してパターニングしてコンタクトホール103〜106を得る。フォトマスク100の第2の透光部102を通して露光すると、感光性樹脂膜が解像不能となり、感光性樹脂膜の表面に凹凸ができる。これにより一枚のフォトマスクでコンタクトホール形成と層間膜表面に凹凸を有する散乱構造とができる。

(もっと読む)

非晶質半導体膜の結晶化方法、薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法

【課題】特性の優れた半導体膜を簡便に得ることができる微結晶半導体膜の結晶化方法と、これを応用した薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、基板1上に形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3を介してゲート電極2の対面に形成され、ソース領域となる第1非晶質領域41、ドレイン領域となる第2非晶質領域42、及び第1非晶質領域41と第2非晶質領域42との間に配置されたチャネル領域となる結晶性領域43を有する半導体膜4と、半導体膜4上に結晶性領域43と直接接触することなく形成され、ソース領域及びドレイン領域とそれぞれ電気的に接続されたソース電極81及びドレイン電極82と、を備えるものである。

(もっと読む)

薄膜トランジスタ、表示装置及び薄膜トランジスタの作製方法

【課題】チャネル形成領域に結晶化率の高い領域を配し、ソースとドレインの間に高抵抗な領域を配し、電界効果移動度が高くオン電流が大きい薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタの下地層に「結晶核の生成を抑制する不純物」を含ませ、または下地層の表面に「結晶核の生成を抑制する不純物」を存在させ、下地層上に設けられた第1の配線層と、第1の配線層に少なくとも一部が接する不純物半導体層と、少なくとも一部が不純物半導体層を介して第1の配線層と電気的に接続される半導体層と、半導体層上に設けられた第1の絶縁層と、少なくとも半導体層と第1の絶縁層を覆って設けられた第2の絶縁層と、第2の絶縁層上であって、不純物半導体層の少なくとも一部、及び不純物半導体層によって形成されるソース領域とドレイン領域の間に重畳して設けられた第2の配線層と、を有する薄膜トランジスタとする。

(もっと読む)

表示装置及び電子機器

【課題】表示装置に置いて、多階調表示を実現することを目的とする。

【解決手段】トランジスタ及び表示素子を有する画素がマトリクス状に配置された画素部と、前記トランジスタのゲートに電気的に接続されたゲートドライバと、前記トランジスタのソース又はドレインに電気的に接続されたソースドライバと、前記ソースドライバに信号を出力するデータ処理回路とを有し、前記トランジスタは、酸化物半導体を用いており、前記データ処理回路は、入力されるmビットのデジタルデータのうち、nビットのデジタルデータ(m、nは共に正の整数、かつm>n)を電圧階調に用い、(m−n)ビットのデジタルデータを時間階調に用いる表示装置である。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

表示装置

【課題】画素の電圧変動を低減することにより、多階調表示を実現できる表示装置を提供する。

【解決手段】表示装置において、並設された複数本のソース信号線10,20と、ソース信号線と交差するように並設された複数本のゲート信号線30と、ソース信号線とゲート信号線との交差部近傍に設けられた酸化物半導体を用いたトランジスタ40を介して、ソース信号線の信号電圧が印加される画素電極70と、を備え、隣接する一対のソース信号線間に設けられる画素電極の側縁部を、ソース信号線の側縁部に重畳させ、かつ、一方のソース信号線との重畳面積を、他方のソース信号線との重畳面積と等しくする。

(もっと読む)

薄膜トランジスタ、その製造方法及びそれを用いた表示装置

【課題】スパッタ法などで保護層を形成する際の半導体層が受けるダメージの不均一性によるTFT間の特性ばらつきを改善し、このTFTを用いるアクティブマトリクス型表示装置の画像の均一性を向上させる。

【解決手段】薄膜トランジスタは、ゲート電極と、ゲート絶縁層と、アモルファス酸化物からなる半導体層と、ソース電極と、ドレイン電極と、保護層とを含む。保護層は、半導体層の上に半導体層と接して設けられる。半導体層は、少なくともチャネル層として機能する第1の層と、第1の層よりも高抵抗な第2の層とを含む。第2の層は、半導体層において保護層側に設けられる。

(もっと読む)

半導体装置およびその作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことにより、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置及びその作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

積層酸化物材料、半導体装置、および半導体装置の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向かって結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の同軸(アキシャル)成長をさせていることである。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】駆動回路及び画素部を有し、駆動回路は、デュアルゲート型の薄膜トランジスタを用いて構成され、画素部はシングルゲート型の薄膜トランジスタを用いて構成される表示装置である。該表示装置おけるデュアルゲート型の薄膜トランジスタは、半導体層が微結晶半導体領域及び一対の非晶質半導体領域で形成され、ゲート絶縁層及び絶縁層が半導体層の微結晶半導体領域に接する。

(もっと読む)

絶縁ゲート型トランジスタ

【課題】酸化物半導体を用いた絶縁ゲート型トランジスタに関し、短チャネル効果を極力抑えることのできる構成を提供する。

【解決手段】絶縁ゲート型トランジスタのチャネル領域を形成する酸化物半導体層に、脱水または脱水素化の工程及び酸素を添加する工程を施してキャリア濃度が1×1012/cm3未満となる真性又は実質的に真性な半導体を使用し、酸化物半導体層に形成されるチャネルの長さが0.2μm以上3.0μm以下であって、酸化物半導体層の厚さが15nm以上30nm以下で、かつゲート絶縁層の厚さが20nm以上50nm以下もしくは、酸化物半導体層の厚さが15nm以上100nm以下で、かつゲート絶縁層の厚さが10nm以上20nm以下とすることで短チャネル効果を抑え、上記チャネル長の範囲でしきい値の変動量を0.5V未満とすることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】不対結合手に代表される欠陥を多く含む絶縁層を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を間に介して、酸化物半導体層上に形成し、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、酸素過剰な混合領域、又は酸素過剰な酸化物絶縁層を通過させて欠陥を含む絶縁層に拡散させ、上記酸化物半導体層中の不純物濃度を低減する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】特性の異なるトランジスタ、具体的には動特性(オン特性や周波数特性(f特性と呼ばれる))に優れたトランジスタと、オフ電流が抑制されたトランジスタとを同一基板上に有する半導体装置を提供することを課題の一とする。また、当該半導体装置を簡便な方法で作製する方法を提供することを課題の一とする。

【解決手段】真性又は実質的に真性であって、表面に結晶領域を含む酸化物半導体層をトランジスタに用いる。真性又は実質的に真性な半導体は、酸化物半導体中で電子供与体(ドナー)となる不純物を除去し、シリコン半導体よりもエネルギーギャップが大きいものを用いる。該酸化物半導体層の上下に絶縁膜を介して配置した一対の導電膜の電位を制御して、該酸化物半導体層に形成するチャネルの位置を変えることにより、トランジスタの電気特性を制御すればよい。

(もっと読む)

121 - 140 / 269

[ Back to top ]