Fターム[2H092JA47]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 素子と画素電極との接続 (3,242) | オーミックコンタクト (422)

Fターム[2H092JA47]に分類される特許

1 - 20 / 422

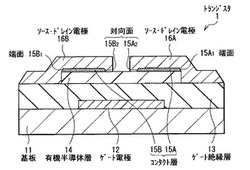

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

液晶表示装置及び配向膜、並びにこれらの製造方法

【課題】液晶表示装置及び配向膜、並びにこれらの製造方法を提供する。

【解決手段】配向膜は、基板上のポリシロキサンに結合した第1プレチルト官能基、第2プレチルト官能基及び第1垂直配向性官能基を含む。環状化合物を含む前記第1垂直配向性官能基33は、前記基板191に対して実質的に垂直方向に配列する。前記第2プレチルト官能基と架橋した前記第1プレチルト官能基35aは、前記基板に対して傾くように配列する。

(もっと読む)

半導体装置

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の提供。

【解決手段】本発明の実施形態に係る液晶表示装置の場合、共通電極の真上または直下に共通電圧線を形成して、直接的に接触させることにより、共通電圧線の信号遅延を低減するとともに、液晶表示装置の開口率の低下を防ぐことができる。

(もっと読む)

配線膜およびそれを用いたアクティブマトリクス基板、並びに配線膜の製造方法

【課題】テーパー形状のAl配線膜を容易かつ安定的に得る。

【解決手段】Al配線膜101は、AlもしくはAl合金から成る第1のAl合金層101aと、その上に配設され、Ni、PdおよびPtのいずれか1以上の元素を含み第1のAl合金層101aとは異なる組成のAl合金から成る第2のAl合金層101bとから成る二層構造を有する。フォトレジスト102の現像処理に用いるアルカリ性薬液により、第2のAl合金層101bはエッチングされ、その端部はフォトレジスト102の端部よりも後退する。その後、フォトレジスト102をマスクとするウェットエッチングを行うことにより、Al配線膜101の断面はテーパー形状となる。

(もっと読む)

液晶表示装置および液晶表示装置の製造方法

【課題】表示品位の劣化を抑制することが可能な液晶表示装置を提供する。

【解決手段】第1方向に沿った長さが第1方向に交差する第2方向に沿った長さよりも短い画素に配置されるとともに、第2方向に沿って延出した主画素電極及び第1方向に沿って延出し主画素電極と電気的に接続された副画素電極を有する画素電極を備えた第1基板10と、主画素電極を挟んだ両側で主画素電極と略平行に延出した主共通電極及び副画素電極を挟んだ両側で副画素電極と略平行に延出し主共通電極と電気的に接続された副共通電極を有する共通電極を備えた第2基板と、第1基板10と第2基板との間に保持された液晶分子を含む液晶層と、を備え、主画素電極と主共通電極との第1方向に沿った水平電極間距離は、主画素電極と主共通電極との第1方向及び第2方向に直交する第3方向に沿った垂直電極間距離よりも大きいことを特徴とする液晶表示装置。

(もっと読む)

電気光学装置、投射型表示装置、電子機器、および電気光学装置の製造方法

【課題】プラグ用の特殊な金属を用いなくても、電気光学装置に他の目的で形成されている膜を利用して、画素電極の導通部分を、大きな面積を占有せず、かつ、画素電極の表面に大きな凹凸を発生させずに形成することのできる電気光学装置、投射型表示装置および電子機器を提供すること。

【解決手段】電気光学装置100では、画素電極9aの下層側に設けられた絶縁膜44(第1絶縁膜)には柱状凸部440が形成されており、かかる柱状凸部440の先端面には、第2電極層7a(導電層)の導通部7tが重なっている。第2電極層7aと画素電極9aとの間には層間絶縁膜45(第2絶縁膜)が設けられているが、かかる層間絶縁膜45の表面450では導通部7tが露出している。このため、層間絶縁膜45に画素電極9aを積層すると、画素電極9aは導通部7tと導通する。

(もっと読む)

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

液晶装置および投射型表示装置

【課題】データ線と電界効果型トランジスターとを電気的に接続するコンタクトホール内の構成を改良して、コンタクトホールでの迷光の反射、およびデータ線の抵抗ばらつきを防止することができる液晶装置、および投射型表示装置を提供すること。

【解決手段】液晶装置100において、コンタクトホール42aの内部には、コンタクトホール42aの内壁42a1に沿って導電性の多結晶シリコン膜60aが形成され、多結晶シリコン膜60aに対して内壁42a1とは反対側にはチタン、ジルコニウムまたはハフニウムからなる遷移金属膜66aが積層されており、データ線6aは、導電性の多結晶シリコン膜60aと、金属材料層65(遷移金属膜66a、アルミニウム膜67aおよびチタン窒化膜68a)との積層構造を有している。多結晶シリコン膜60aと遷移金属膜66aとの間にはシリサイド層61が介在している。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層の幅を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制する。

【解決手段】ボトムゲート電極12aと第1のブラックマトリックス層17aで第1の半導体層14を挟むシングルゲート型の薄膜トランジスタを有する半導体装置であって、前記第1の半導体層と前記第1のブラックマトリックス層は重畳している半導体装置である。

(もっと読む)

液晶表示装置およびマザー基板

【課題】TFT基板に有機パッシベーション膜が形成されておらず、かつ、TFT基板と対向基板との間隔を柱状スペーサによって規定する液晶表示装置において、TFT基板と対向基板との間隔を一定とする。

【解決手段】液晶表示パネルの表示領域では、TFT基板100と対向基板200との間隔は柱状スペーサ150によって規定している。液晶表示パネル内において、画素も走査線も映像信号線も形成されていない部分においても、柱状スペーサ150によって間隔を規定する。この場合、柱状スペーサ150の台座140が必要となるが、台座140の層構造は、表示領域において間隔を規定する柱状スペーサ150が接触するTFT基板側の層構造と同一にする。これによって、製造コストの上昇をともなうことなく、液晶表示パネルの液晶層300の間隔を一定にでき、輝度むら、あるいは色むらを防止することが出来る。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

表示基板の製造方法

【課題】過剰なエッチングによる不良を減少させるための表示基板の製造方法を提供する。

【解決手段】互いに交差する信号ラインによって定義された複数の単位画素Pを有する表示領域DAと表示領域DAを取り囲む周辺領域PAを含む基板110上にフォトレジスト膜を塗布する段階と、フォトレジスト膜をパターニングして、表示領域DAで信号ラインとオーバーラップされる第1パターン部P1と、周辺領域PAで信号ラインと重畳されない領域に形成された複数のダミー開口部DOを含む第2パターン部P2とを形成する段階と、第1パターン部P1及び第2パターン部P2が形成された基板110上に透明電極層117a、117bを形成する段階と、ストリップ溶液で第1パターン部P1、第2パターン部P2、及び第1及び第2パターン部上に形成された透明電極層117a、117bを除去して、単位画素Pに対応する画素電極PE及びダミー開口部DOに対応するダミー電極DMを形成する段階と、を含む。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置及び表示装置の製造方法を提供すること。

【解決手段】表示装置は下部基板、有機膜パターン、第1画素電極、誘電膜、及び第2画素電極を含む。下部基板はスイッチング素子を具備する。有機膜パターンは、前記下部基板上に配置され、画素領域に段差部を含む。第1画素電極は画素領域の有機膜パターン上に配置される。誘電膜は第1画素電極上に配置される。第2画素電極は誘電膜上で第1画素電極と部分的に重畳される。第1画素電極のモルフォロジーによって不均一な垂直電界発生が抑制されて表示装置、特に画素電極と共通電極との間に発生されたフリンジフィールドを使用するPLSモード方式の液晶表示装置の輝度分布を改善することができる。

(もっと読む)

液晶表示装置

【課題】垂直配向モード液晶表示装置のコントラスト比を向上させた液晶表示装置を提供する。

【解決手段】

液晶表示装置を提供する。本発明の一実施形態による液晶表示装置は、第1基板と、前記第1基板上に位置するカラーフィルタと、前記第1基板と対応する第2基板と、前記第1基板と前記第2基板の間に介される液晶層と、前記第1基板上に付着した第1補償フィルムと、前記第1補償フィルムの外側面に位置する第1偏光板と、前記第2基板上に位置する第2補償フィルムと、前記第2補償フィルムの外側面に位置する第2偏光板とを含み、前記第1補償フィルムは、−10nm以上10nm以下の範囲の面内の位相差値(Ro)と、−10nm以上10nm以下の範囲の厚さ方向の位相差値(Rth)を含み、前記第2補償フィルムは二軸性フィルムである。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

非晶質酸化物薄膜トランジスタ及びその製造方法、その薄膜トランジスタを含むディスプレイパネル

【課題】本発明の実施例は非晶質酸化物薄膜トランジスタ及びその製造方法、ディスプレイパネルを開示する。

【解決手段】前記非晶質酸化物薄膜トランジスタは、ゲート電極、ゲート絶縁層、半導体活性層、ソース電極及びドレイン電極を含む。前記半導体活性層はチャネル層とオーミック接触層を含み、前記チャネル層は前記オーミック接触層に比べ酸素含有量が高い。また、前記チャネル層は前記ゲート絶縁層と接し、前記オーミック接触層は二つの独立したオーミック接触領域に分けられ、かつ前記二つの独立したオーミック接触領域はそれぞれ前記ソース電極、ドレイン電極と接する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

1 - 20 / 422

[ Back to top ]