Fターム[2H092KA07]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子、光導電体層の材料 (8,799) | 素子材料 (4,927) | 物質 (1,730) | 無機材料 (1,105)

Fターム[2H092KA07]の下位に属するFターム

化合物 (540)

Fターム[2H092KA07]に分類される特許

341 - 360 / 565

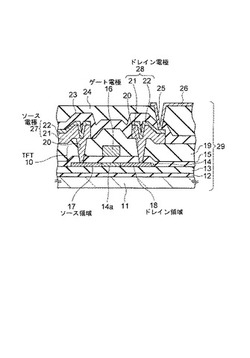

駆動回路、アクティブマトリクス基板及び液晶表示装置

【課題】単一導電型のTFTからなる駆動回路に要求されるTFTのオフリーク電流を、簡単な製造工程で実現する。

【解決手段】TFT10のソース領域17及びドレイン領域18の不純物濃度を2×1018[cm−3]以上かつ2×1019[cm−3]以下とすることにより、シングルゲート構造でもTFT10のオフリーク電流を十分に低減できる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置

【課題】歩留まり向上が可能で、かつ品質向上につながる薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置を提供すること。

【解決手段】本発明に係る薄膜トランジスタの製造方法は、基板1上にゲート電極2を形成する工程と、ゲート電極2上にゲート絶縁膜3を形成する工程と、ゲート絶縁膜3上に、ゲート電極2の少なくとも一部と対向配置する半導体層10のパターン形成する工程と、半導体層10上にソース電極5、及びドレイン電極6を形成する工程と、ソース電極5、及びドレイン電極6をマスクとして、チャネル領域10Cに相当する半導体層10を所望の膜厚までエッチングする工程と、露出した半導体層10にレーザ光を照射する工程とを備える。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】サイズの大型化を抑制しつつ必要な電流を得ることの可能な薄膜トランジスタおよびこれを用いた表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板10上にゲート電極11およびゲート絶縁膜12を介してシリコン膜13を有している。シリコン膜13のゲート電極11に対応する領域には絶縁保護膜14が形成され、絶縁保護膜14の上面両端からシリコン膜13上にかけて、非晶質シリコン膜(ソース領域)15Aおよび非晶質シリコン膜(ドレイン領域)15Bが形成され、それぞれソース電極16Aおよびドレイン電極16Bにより覆われている。シリコン膜13はチャネル領域13Cを有し、このチャネル領域13Cにおいて長さ方向に沿って結晶化領域13Bおよび非結晶領域13Aが形成されている。結晶化領域13Bの幅d1が調整されることにより、必要電流が得られる。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】TFTに代表される半導体素子の動作特性が改善されるように、微結晶シリコン膜若しくは結晶粒を含む膜の膜質を制御する。また、微結晶シリコン膜若しくは結晶粒を含む膜の堆積過程を制御して、TFTに代表される半導体素子の特性向上を図る。また、薄膜トランジスタのオン電流を向上させ、オフ電流を低減する。

【解決手段】非晶質構造の中に複数の結晶領域を含む半導体層において、該結晶領域が生成する起点となる結晶核の生成位置と生成密度を制御することで、該半導体層の膜質を制御する。また、半導体層の結晶領域が生成する起点となる結晶核を生成した後、ドナーとなる不純物元素を半導体層に添加して、半導体層の結晶性を高めると共に、半導体層の抵抗率を低減する。

(もっと読む)

パターン形成方法、半導体装置の製造方法、および表示装置の製造方法

【課題】塗布印刷法の適応のみによって形状精度良好に目的パターンを形成することが可能なパターン形成方法を提供する。

【解決手段】基板1上に樹脂パターン9を印刷形成する。樹脂パターン9上からフッ素系材料を供給することにより、樹脂パターン9の開口9a底部をフッ素系材料で覆った撥水性パターン11を形成する。樹脂パターン9を除去することにより、撥水性パターン11に開口窓11aを形成する。撥水性パターン11の開口窓11a内に半導体材料(パターン形成材料)を供給することにより、目的パターンとして半導体層13を形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】電気的ストレスによる閾値電圧変化の小さいコプラナー構造の薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板の上に、ゲート電極と、ゲート絶縁層と、ソース電極とドレイン電極とチャネル領域とからなる酸化物半導体層と、チャネル保護層と、層間絶縁層と、を少なくとも有する薄膜トランジスタであって、前記チャネル保護層は1層以上で形成され、そのうち前記酸化物半導体層と接する層は酸素を含む絶縁体からなり、該チャネル保護層の端部の膜厚が該チャネル保護層の中央部の膜厚と比べ薄く、かつ、前記層間絶縁層は水素を含有しており、該層間絶縁層と直接接している該酸化物半導体層の領域がソース及びドレイン電極をなしていることを特徴とする。

(もっと読む)

液晶装置及び電子機器

【課題】画素電極と共通電極とが絶縁層を介して積層された液晶装置について良好な表示品位を得ることである。

【解決手段】液晶装置は、液晶層52を挟持する一対の基板と、領域毎に液晶層52の配向状態を制御する複数の画素と、一対の基板のうち一方の基板の液晶層52側に設けられ、複数の画素の領域にそれぞれ設けられた第1電極12と、第1電極12上に設けられた絶縁層60を介して積層され、第1電極12が設けられた領域において非形成部分26を有して第1電極12との間に電界を生じさせる第2電極30と、第2電極30より下層で、第1電極12が設けられていない領域と重畳する領域の少なくとも一部に設けられ、第2電極30と電気的に接続された第3電極32と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】高温(600℃以上)の加熱処理回数を低減し、さらなる低温プロセ

ス(600℃以下)を実現するとともに、工程簡略化及びスループットの向上を

実現することを課題とする。

【解決手段】本発明は結晶構造を有する半導体膜へマスク106bを用いて希ガ

ス元素(希ガスとも呼ばれる)を添加した不純物領域108を形成し、加熱処理

により前記不純物領域108に半導体膜に含まれる金属元素を偏析させるゲッタ

リングを行った後、前記マスクを用いてパターニングを行い、結晶構造を有する

半導体膜からなる半導体層109を形成する。

(もっと読む)

画像表示システムとその製造方法

【課題】 画像表示システムとその製造方法を提供する。

【解決手段】 薄膜トランジスタアレイ基板を含む画像表示システムであって、薄膜トランジスタアレイを有する基板、及び前記基板上に形成されたアモルファスシリコン層を含む、少なくとも1つの前記基板に平行の方向に流れる電流を有する受光素子を含む画像表示システム。

(もっと読む)

液晶セルおよび液晶ディスプレイ装置

【課題】柔軟性に富み、かつ、損傷し難く、耐久性に富み、そして動作不良が起き難い高品質な液晶セルを提供することである。

【解決手段】導電層と導電層との間に液晶層が設けられてなる液晶セルであって、前記導電層の中の少なくとも一方の導電層が絡み合った単層カーボンナノチューブで構成されてなる。

(もっと読む)

画像表示装置

【課題】静電容量結合により信号を送受信する通信方式を採用する画像表示装置において多チャンネル化に伴う額縁の増大を最小限に抑える。

【解決手段】第1基板は、第1電圧レベルの電圧が供給される平板状の第1電源配線と、前記第1電圧レベルとは電圧レベルが異なる第2電圧レベルの電圧が供給される平板状の第2電源配線と、前記第1電源配線および前記第2電源配線に接続される半導体素子と、静電誘導によって信号を送受信するため平板状の第1電極群とを有し、第2基板は、静電誘導によって信号を送受信するための平板状の第2電極群と、前記信号の基準電圧が供給される平板状の共通電極とを有し、前記第1基板と前記第2基板とを重ね合わせた状態において、前記第2電極群には、前記第1電極群が重なり、前記共通電極には、前記第1電源配線あるいは前記第2電源配線が重なる。

(もっと読む)

半導体記憶装置、表示装置及び機器

【課題】絶縁基板上に形成される不揮発性メモリ素子において、外部の光が電荷保持部に当ることにより、保持した電荷が、活性化し逃げることを防止することを課題とする。

【解決手段】絶縁基板上に不揮発性メモリ素子を備え、前記不揮発性メモリ素子が、電荷保持膜と、チャネル領域と、前記チャネル領域の両側にソースとドレインとを備える半導体層を備え、前記電荷保持膜が、少なくともその一部の上側と下側とに設けられた、上側遮光体及び下側遮光体の間に位置していることを特徴とする半導体記憶装置により上記課題を解決する。

(もっと読む)

液晶セルおよび液晶ディスプレイ装置

【課題】柔軟性に富み、かつ、損傷し難く、耐久性に富み、そして動作不良が起き難い高品質な液晶セルを提供することである。

【解決手段】導電層と導電層との間に液晶層が設けられてなる液晶セルであって、

前記導電層の中の少なくとも一方の導電層が金属ナノワイヤで構成されてなる。

(もっと読む)

SOI基板の作製方法

【課題】大面積基板に厚さのばらつきの小さい結晶性半導体層を形成することを課題とする。

【解決手段】複数の半導体基板に表面からの深さが異なる位置に脆化層を形成し、ベース基板面内の化学機械研磨の研磨量が大きい領域には表面から脆化層までの深さが大きい半導体基板を配置し、ベース基板面内の化学機械研磨の研磨量が小さい領域には表面から脆化層までの深さが小さい半導体基板を配置し、ベース基板と前記半導体基板を接合し、脆化層を起点としてベース基板と半導体基板を分離することで第1の半導体層を形成し、第1の半導体層をCMPにより研磨して第2の半導体層を形成する。CMPに代えてエッチング処理を用いても良く、この場合にはエッチングレートが大きい領域に、表面から脆化層までの深さが大きい半導体基板を配置する。

(もっと読む)

薄膜トランジスタの作製方法及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】導電膜を形成し、前記導電膜上にパターンを有する薄膜積層体を形成し、前記導電膜に達するように前記薄膜積層体に開口部を形成し、サイドエッチングを用いて前記導電膜を加工してゲート電極層を形成し、前記ゲート電極層上に絶縁層、半導体層、ソース電極及びドレイン電極層を形成することで薄膜トランジスタを作製する。開口部を設けることでエッチングの制御性が向上する。

(もっと読む)

薄膜トランジスタパネルおよびその製造方法

【課題】薄膜トランジスタパネルの製造工程数を少なくする。

【解決手段】走査ライン5と静電保護リング12とは、電極41、42を有する静電保護素子13および接続配線43を介して接続されている。そして、静電保護素子13を含むゲート絶縁膜22の上面に層間絶縁膜29を形成した後に、フォトリソグラフィ法により、コンタクトホール44、45、46を形成する。次に、特に、層間絶縁膜29の上面に接続配線43をコンタクトホール44、45を介して走査ライン5および一方の電極41に接続させて形成する。この場合、層間絶縁膜29およびゲート絶縁膜22に連続してコンタクトホール44を形成することにより、コンタクトホール形成工程を1回減らすことができる。

(もっと読む)

半導体装置

【課題】SOI技術で形成された単結晶シリコン薄膜から応力に起因する準位や欠陥を除去するための方法を提供する。

【解決手段】まずSmart−CutやELTRANといった代表的な貼り合わせSOI技術を用いて単結晶シリコン薄膜106を形成する。次に単結晶シリコン薄膜106をパターニングして島状シリコン層108とした後、ハロゲン元素を含む酸化性雰囲気中で熱酸化処理を行うことで、トラップ準位や欠陥の除去された島状シリコン層109を得る。

(もっと読む)

薄膜トランジスタ及びその作製方法、並びに表示装置及びその作製方法

【課題】マスク数の少ない薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】第1の絶縁膜と、第1の導電膜と、第2の絶縁膜と、半導体膜と、不純物半導体膜と、第2の導電膜とを積層し、この上にレジストマスクを形成し、第1のエッチングにより第1の絶縁膜の上部までエッチングして薄膜積層体を形成し、該薄膜積層体に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、その後第2のレジストマスクによりソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。

(もっと読む)

半導体装置、電気光学装置および電子機器

【課題】樹脂層などのフレキシブルな層上に形成された場合であっても信頼性に優れる半導体装置の構成を提供する。

【解決手段】本発明に係る樹脂層(S)上に形成された半導体装置は、複数の下ゲート型薄膜トランジスタを含み、該半導体装置は該下ゲート型薄膜トランジスタを構成する半導体層(17)と、第一の配線(GL1、GL2)と、第二の配線(SL)と、第一絶縁層(15)と、ゲート絶縁膜(19)とを少なくとも有し、該半導体層と該第一の配線と第二の配線の下部には該第一絶縁層と該ゲート絶縁膜が存在し、該半導体層と該第一の配線と第二の配線とが形成されていない箇所では、該第一絶縁層と該ゲート絶縁膜の一部が取り除かれている。該第一絶縁層と該ゲート絶縁膜の一部を取り除いたので、半導体装置に、機械的、または熱的な応力が加えられた場合であっても、当該応力が緩和され、第一絶縁層等におけるクラックの発生を低減できる。

(もっと読む)

半導体装置、電気光学装置および電子機器

【課題】特性の向上を図ることのできる半導体装置(アレイ基板)の構成を提供する。

【解決手段】本発明に係るフレキシブル基板上に形成された半導体装置は、配線の一部を構成する第一配線層(GL1)と第二配線層(GL2)と、第一絶縁層(15)と第二絶縁層(23)とを少なくとも有し、該第一配線層は該第一絶縁膜上に形成されており、該第二配線層は該第二絶縁膜上に形成されており、該第二絶縁層は該第一配線層と該第二配線層との間に位置し、該第二配線層においては他の配線(SL1、SL2)との交差部を有さず、該第二配線層は、該第二絶縁層の一部を取り除いて該第一配線層と接続されている。かかる構成によれば、配線の一部を第一配線層と第二配線層とに分割したので、第一配線層下に第一絶縁層を分割して配置することができる。よって、機械的、または熱的な応力が加えられた場合であっても、下地絶縁膜におけるクラックの発生を低減できる。

(もっと読む)

341 - 360 / 565

[ Back to top ]