Fターム[2H092MA06]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 成膜方法 (5,204) | PVD (2,371) | イオンプレーティング法 (114)

Fターム[2H092MA06]に分類される特許

21 - 40 / 114

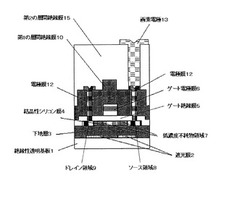

薄膜トランジスタ、その製造方法、及び表示装置並びに電子機器

【課題】製造コストが少なく、光リーク電流が抑制された薄膜トランジスタを提供する。

【解決手段】透明基板上に作製される薄膜トランジスタであって、透明基板上に、少なくともチャネル領域と重畳しないように配置された遮光膜、下地層、結晶性シリコン膜、ゲート絶縁膜、ゲート電極膜を順次形成してなるトップゲート型結晶性シリコン薄膜トランジスタの構造を具え;結晶性シリコン膜には、チャネル長Lのチャネル領域、それを挟むLDD長dのLDD領域、ソース領域、ドレイン領域が形成されており;遮光膜はチャネル領域を挟んで分割されており;分割された遮光膜の間隔xは、チャネル長L以上、チャネル長LとLDD長dの2倍の和(L+2d)以下に選択されていることを特徴とする。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

電気光学装置の製造方法

【課題】液晶装置等の電気光学装置において、高品質な表示を行う。

【解決手段】電気光学装置の製造方法は、基板(10)に、トランジスタの半導体層(1a)を形成する半導体層形成工程と、半導体層のチャネル部(1a’)に不純物を導入する不純物導入工程と、基板を平面的に見て、チャネル部に重なるようにゲート電極(3b)を形成するゲート電極形成工程とを備える。不純物導入工程においては、不純物は、チャネル幅方向においてチャネル部の端部に位置する第1領域、及びチャネル長方向において第1領域よりも幅が狭いチャネル部の第2領域にそれぞれ導入される。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】製造コストを低減することができ、かつ、歩留まりの高い薄膜トランジスタを提供することにある。

【解決手段】本発明の実施の形態1に係る薄膜トランジスタの製造方法は、絶縁基板10の上に少なくともゲート電極11、ゲート絶縁層12、半導体層13、ソース電極14、ドレイン電極15及び保護層16を具備する薄膜トランジスタの製造方法であって、保護層16が真空紫外光CVD法により形成されるものであり、ゲート絶縁層12の上の全面に保護層16となる膜を成膜する工程と、保護層と16なる膜をパターニングなしにエッチングしソース電極14とドレイン電極15の表面を露出させ保護層16のパターンを形成する工程と、を具備する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に第1の薄膜トランジスタを有する駆動回路及び第2の薄膜トランジスタを有する画素を有し、前記第1の薄膜トランジスタは、第1のゲート電極層と、ゲート絶縁層と、第1の酸化物半導体層と、第1の酸化物導電層及び第2の酸化物導電層と、前記第1の酸化物半導体層の一部に接し、且つ前記第1の酸化物導電層及び前記第2の酸化物導電層の周縁及び側面に接する酸化物絶縁層と、第1のソース電極層と、第1のドレイン電極層と、を有し、前記第2の薄膜トランジスタは、第2のゲート電極層と、第2の酸化物半導体層と、透光性を有する材料により構成された第2のソース電極層及び第2のドレイン電極層と、を有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に画素部と駆動回路が設けられ、画素部の第1の薄膜トランジスタは、基板上にゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、ゲート絶縁層、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸化物半導体層の一部と接する保護絶縁層と、保護絶縁層上に画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、保護絶縁層、及び画素電極層は透光性を有し、駆動回路の第2の薄膜トランジスタのソース電極層及びドレイン電極層は、第1の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第1の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗の導電材料である。

(もっと読む)

半導体装置およびその作製方法

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

表示装置及びその製造方法

【課題】LDD層を有する薄膜トランジスタにおけるオフ電流を低減させることと光リーク電流を低減させることが可能な表示装置及びその製造方法を提供する。

【解決手段】薄膜トランジスタTFTの半導体層PSは第1、第2、第3の層とを有し、前記第1の層の一部は前記薄膜トランジスタのチャネル領域であり、前記第2の層は不純物層であり、前記第3の層は不純物濃度が低い低濃度不純物層LDDであり、前記第2の層は前記電極との接続箇所を有し、前記第3の層は前記第2の層を環状に囲んで形成され、平面的に見て、前記第3の層の端部のうち、前記チャネル領域側の端部は前記第1の層と接しており、前記チャネル領域側以外の端部は前記層間絶縁膜INと接しており、前記第2の層の夫々は、前記ゲート電極GTと平面的に重畳する第1の領域と、前記ゲート電極GTと平面的に重畳しない第2の領域とを有し、前記接続箇所は前記第2の領域に形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】高い開口率を有し、安定した電気的特性を有する薄膜トランジスタを有する、信頼性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体膜とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体膜の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のための加熱処理)を行う。また、ゲート電極層、ソース電極層、及びドレイン電極層を透光性の導電膜を用いて作製し、開口率を向上させる。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体層とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層に接する酸化物絶縁膜を形成する。酸化物半導体層を減圧されたチャンバー内に導入後、窒素雰囲気下で加熱処理工程、プラズマ(少なくとも酸素プラズマを含む)の導入工程を行い、成膜ガスを導入して酸化物絶縁膜を形成する。

(もっと読む)

液晶表示装置

【課題】液晶表示装置において、ディスクリネーションを低減する。

【解決手段】第1及び第2の走査線と第1及び第2の信号線とによって囲まれた領域に設けられた第1の画素電極と、第2及び第3の走査線と第1及び第2の信号線とによって囲まれた領域に設けられた第2の画素電極と、第1及び第2の画素電極の上方に設けられた対向電極を有し、第1の画素電極は、中央で最大の面積を占める平坦面と、第1乃至第4の端部を有し、第1の端部は第1の走査線に沿って設けられ、第2の端部は第1の信号線に沿って設けられ、第3の端部は第2の走査線に沿って設けられ、第4の端部は第2の信号線に沿って設けられ、第2及び第4の端部は前記平坦面と同じ高さに設けられ、第1及び第3の端部は平坦面より0.5μm以上高く設けられた液晶表示装置を提供する。

(もっと読む)

薄膜トランジスタ及びその製造方法、電気光学装置、並びにセンサー

【課題】オン電流が高く、特性シフトが低減された薄膜トランジスタを提供する。

【解決手段】基板上に、活性層としてのIn、Ga、及びZnを含む酸化物半導体膜と、ゲート電極と、ゲート絶縁膜と、ソース電極と、ドレイン電極と、を有し、

前記酸化物半導体膜のモル比〔In:Ga:Zn〕を2.0−x:x:y(但し、0.0<x<2.0、0.0<y)で表したとき、前記酸化物半導体膜の膜厚方向についての前記yの分布において、前記基板に近い側の膜面、及び、前記基板から離れた側の膜面よりも、前記yが大きい領域が存在する。

(もっと読む)

電界効果型トランジスタ及びその製造方法並びに画像表示装置

【課題】プラスチックフィルム基板と電界効果型トランジスタとの密着性を下地層を形成することで化学的に高め、フォトリソグラフィ工程で用いる強酸や強アルカリへの浸漬によっても電界効果型トランジスタがプラスチックフィルム基板から剥離することなく再現性良く製造する電界効果型トランジスタ及びその製造方法並びに画像表示装置を提供する。

【解決手段】基板、ゲート電極、ゲート絶縁層、ソース電極、ドレイン電極及び半導体を有して形成された電界効果型トランジスタであって、基板上に高分子化合物と金属化合物との混合物を含有する下地層を備えることを特徴とする電界効果型トランジスタ。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法

【課題】電界効果型トランジスタの製造工程の簡略化が図れる電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法を提供する。

【解決手段】本実施の形態のトップコンタクト型の電界効果型トランジスタ10の製造方法によれば、半導体層形成工程で形成した活性層18上に、防護層22を形成した後に、該防護層22上にフォトレジスト膜を形成して露光工程においてパターン状に露光する。そして、次の現像工程において、アルカリ性現像液を用いて、上記露光工程を経たフォトレジスト膜30を現像してレジストパターン30B’を形成すると共に、防護層22における該レジストパターン30B’から露出している領域22Aを除去して防護層22のエッチングを行なう。

(もっと読む)

表示媒体、書込装置、及び表示装置

【課題】本発明の構成を有さない場合に比べ、耐光性に優れた表示媒体、書込装置、及び表示装置を提供する。

【解決手段】表示媒体12においては、第2の光吸収層34が、第2の電極22の光導電層20とは反対側に設けられている。すなわち、第2の光吸収層34は、表示媒体12の光導電層20より書込光の照射方向上流側に設けられている。この第2の光吸収層34は、書込光を透過し、且つ300nm以上550nm以下の全波長領域について吸光度1以上の遮光性能を示す。このため、蛍光灯の光のように、書込に利用されない波長の光が非表示面側から光導電層20へ到ることが抑制され、光導電層20の外光による光劣化が抑制される。従って、耐光性に優れた表示媒体12が提供される。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置および電子機器

【課題】ボトムゲート構造およびトップゲート構造の双方の特長を兼ね備えた半導体装置の製造方法、半導体装置、電気光学装置、および電子機器を提供すること。

【解決手段】素子基板10上の薄膜トランジスター30は、ボトムゲート構造を備え、かつ、ポリシリコン膜からなる島状半導体膜1aにチャネル領域1g、低濃度ソース領域1b、低濃度ドレイン領域1c、高濃度ソース領域1d、高濃度ドレイン領域1eを備えたGOLD構造を備えている。素子基板10を製造する際、諧調露光により形成したレジストマスクと、かかるレジストマスクに対するエッチバックを利用して、高濃度不純物の導入、半導体膜のパターニングと、ゲート絶縁膜2aと同層の層間絶縁膜のコンタクトホールを形成すべき領域からの半導体膜の除去、および低濃度不純物の導入とを行なう。

(もっと読む)

薄膜トランジスタ及びその作製方法、並びに半導体装置

【課題】薄膜トランジスタのオフ電流の増加、又はしきい値電圧のマイナスシフトを予防すること。

【解決手段】薄膜トランジスタ150は、ソース電極層107a及びドレイン電極層107bと酸化物半導体層103の間にバッファ層106が設けられている。バッファ層106は、酸化物半導体層103の中央部上に、絶縁体若しくは半導体である金属酸化物層105を有する。金属酸化物層105は、酸化物半導体層103への不純物の侵入を抑制する保護層として機能する。そのため、薄膜トランジスタ150のオフ電流の増加、又はしきい値電圧のマイナスシフトを予防することができる。

(もっと読む)

薄膜装置、およびその製造方法、並びに電気光学装置

【課題】転写技術を利用した薄膜装置の製造工程、およびその製造後に、誘導によって生じる帯電を防止することが可能な薄膜装置、およびその製造方法を提供すること。

【解決手段】本発明に係る薄膜装置の製造方法は、導電性を有する第二転写基板120上に薄膜素子(被転写層110)を転写した後、その薄膜素子などによって形成された薄膜素子回路に基準電位を与える電極端子130を、導電性を有する第二転写基板120と接続する。

(もっと読む)

薄膜トランジスタ基板ならびに液晶表示素子およびその製造方法

【課題】配線や電極等による段差に起因する配向処理むらを抑制し、配向不良の発生を低減でき、充電時間を短くできるTFT基板の提供。

【解決手段】基材2と、基材上に形成されたゲート線と、ゲート絶縁層4と、オーバーコート層6と、ソース線と、画素電極8と、基材2上に形成されゲート線に接続されたゲート電極13、TFT用ゲート絶縁層14、TFT用ゲート絶縁層上に形成された半導体層15、TFT用ゲート絶縁層および半導体層の上に上記オーバーコート層と連続して形成されたTFT用オーバーコート層16、TFT用オーバーコート層上に形成され、ソース線に接続され、半導体層にソース電極用コンタクトホールh1を介して接続されたソース電極17、および、TFT用オーバーコート層上に形成され、画素電極に接続され、半導体層に透明電極用コンタクトホールh2を介して接続された透明電極18を有するTFT10とを有する。

(もっと読む)

21 - 40 / 114

[ Back to top ]