Fターム[2H092MA41]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | セルフアラインメント (170)

Fターム[2H092MA41]の下位に属するFターム

裏面露光 (28)

Fターム[2H092MA41]に分類される特許

21 - 40 / 142

半導体装置

【課題】 本発明は、大画面化しても低消費電力を実現した半導体装置の構造を提供する。

【解決手段】 絶縁表面上に形成されたゲート電極と、前記絶縁表面上に形成された第1の配線と、前記ゲート電極上に形成された絶縁膜と、前記絶縁膜上に形成された半導体膜と、第1の配線上に形成された第2の配線と、を有し、前記第1の配線は、前記ゲート電極と同じ材料からなり、表面に前記ゲート電極よりも低抵抗な材料を有し、前記第2の配線を介して前記半導体層と電気的に接続し、前記第1の配線の低抵抗化を図る。

(もっと読む)

半導体装置およびその製造方法

【課題】高解像度のイメージングセンサにおいても、十分な光電流を得ることができる半導体装置を提供する。

【解決手段】薄膜ダイオード200Aは、第1および第2半導体領域233、234を有する第1半導体層230と、第1半導体層230上に形成された第2および第3半導体層236、238と、第1および第2コンタクトホール241、242とを有する。第1半導体領域233は、第1導電型不純物を含有し、第2半導体領域236および第3半導体層238は、第2導電型不純物を含有し、第2半導体層236は、第2導電型不純物とは異なる第3導電型不純物を含有し、第2および第3半導体層236、238は、選択成長により形成され、第2半導体領域234は第2コンタクトホール242に整合している。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明は、エッチングレジストを形成するためのフォトリソグラフィの工程を減らすことを目的とする。

【解決手段】ゲート電極30、ドレイン電極52及びソース電極54を含む薄膜トランジスタを形成する。薄膜トランジスタを覆う第1絶縁膜44を形成する。第1絶縁膜44上に第2絶縁膜46を形成する。第2絶縁膜46上に透明導電膜170を形成する。透明導電膜170上にフォトリソグラフィによってパターニングされたエッチングレジスト50を形成する。エッチングレジスト50を介して、透明導電膜170を第1エッチングによってパターニングして第1透明電極70を形成する。エッチングレジスト50を介して、第2絶縁膜46の第1透明電極70から露出する表面に対して行う第2エッチングによって第2絶縁膜46にドレイン電極52及びソース電極54の一方の上方に位置する貫通穴40を形成する。

(もっと読む)

半導体装置及び半導体装置を用いた表示装置

【課題】電極を精度良く形成できると共に、設計マージンを低減することが可能な構造の半導体装置を提供する。

【解決手段】薄膜トランジスタのゲート電極22と、このゲート電極22を覆って形成されたゲート絶縁膜23と、このゲート絶縁膜23上に形成され、薄膜トランジスタのソース領域、チャネル領域、ドレイン領域を構成する有機半導体層24と、この有機半導体層24上に形成された構造体31と、ゲート絶縁膜23上から構造体31よりも外側の有機半導体層24上にわたって形成された、薄膜トランジスタのソースドレイン電極25,26と、このソースドレイン電極25,26と同じ材料により、構造体31の上に形成された、電極材料層32とを含む半導体装置を構成する。

(もっと読む)

電気光学装置及び電子機器

【課題】画像の表示を明るくするとともに、表示品位の良好な電気光学装置及び電子機器を提供する。

【解決手段】電気光学装置は、一対の基板32,50と、一対の基板32,50間に挟持された電気光学層46と、を有し、一方の基板32に、トランジスター38と、トランジスター38に対応して設けられた反射電極40aと、隣り合う反射電極40a間に、一対の基板32,50間のギャップを規定し、誘電体多層膜からなるスペーサー72と、を備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に画素部と駆動回路が設けられ、画素部の第1の薄膜トランジスタは、基板上にゲート電極層と、ゲート電極層上にゲート絶縁層と、ゲート絶縁層上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、ゲート絶縁層、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸化物半導体層の一部と接する保護絶縁層と、保護絶縁層上に画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、保護絶縁層、及び画素電極層は透光性を有し、駆動回路の第2の薄膜トランジスタのソース電極層及びドレイン電極層は、第1の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第1の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗の導電材料である。

(もっと読む)

液晶表示装置の作製方法

【課題】誘電体多層膜でなる増反射膜を用いた液晶表示装置において、液晶に印可される

電圧が小さくなるといった問題(電圧損失の問題)を解決することを目的とする。

【解決手段】スイッチング素子に電気的に接続された金属膜上の誘電体多層膜の積層数を

2層(第1の誘電体膜105、第2の誘電体膜106)と少なくし、さらに、第1の誘電

体膜の膜厚105を第2の誘電体膜106の膜厚よりも薄くすることによって、電圧損失

の問題を解決する。

(もっと読む)

半導体装置

【課題】消費電力を抑えつつ、走査線へ十分な振幅の信号を供給することができる半導体装置の提供を課題の一とする。また、消費電力を抑えつつ、走査線に供給する信号のなまりを抑制し、立ち上がり時間又は立ち下がり時間を短くすることができる半導体装置の提供を課題の一とする。

【解決手段】表示素子及び少なくとも1つの第1トランジスタをそれぞれ有する複数の画素と、複数の画素を選択するための信号を走査線に供給する走査線駆動回路とを有し、表示素子の画素電極層と、第1トランジスタのゲート電極層、ソース電極層及びドレイン電極層と、走査線とは、透光性を有する導電膜を用いており、走査線駆動回路は、第2トランジスタと、第2トランジスタのゲート電極層とソース電極層の間の電圧を保持する容量素子と、を有しており、第2トランジスタのソース電極層は走査線に接続されている半導体装置。

(もっと読む)

半導体装置及び電子機器

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイン電極に接触しない。

(もっと読む)

液晶装置および液晶装置の製造方法、並びに電子機器

【課題】横方向電界で液晶分子を回転させる方式を用いた場合、液晶は電極に対して基板から離れた方向に配置される。つまり、基板側に生じる電界は液晶分子の回転に寄与しない。そのため、電界の利用率が低下する。また、電気抵抗が低い結晶型ITOを用いた場合、ドライエッチングでは残渣が残り、ウェットエッチングでは寸法精度が出せないという課題がある。

【解決手段】電極間に位置する誘電体をエッチングして逆テーパー状に窪ませることで、電界強度が強い電極間に液晶が入る領域を設けた。窪ませた部分の液晶分子も電界により回転するため電界の利用率を向上させることができる。また、逆テーパー状に誘電体が形成されているため、スパッター法等で結晶型ITO膜を形成した場合、自己整合的にITO膜が分離されるため、ITOをエッチングすることなく所望のパターンを形成することが可能となる。

(もっと読む)

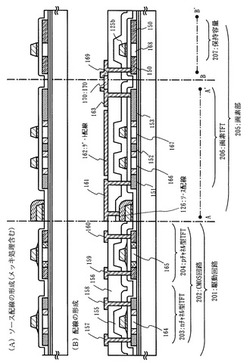

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的とする。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

液晶表示装置

【課題】液晶表示装置において、ディスクリネーションを低減する。

【解決手段】第1及び第2の走査線と第1及び第2の信号線とによって囲まれた領域に設けられた第1の画素電極と、第2及び第3の走査線と第1及び第2の信号線とによって囲まれた領域に設けられた第2の画素電極と、第1及び第2の画素電極の上方に設けられた対向電極を有し、第1の画素電極は、中央で最大の面積を占める平坦面と、第1乃至第4の端部を有し、第1の端部は第1の走査線に沿って設けられ、第2の端部は第1の信号線に沿って設けられ、第3の端部は第2の走査線に沿って設けられ、第4の端部は第2の信号線に沿って設けられ、第2及び第4の端部は前記平坦面と同じ高さに設けられ、第1及び第3の端部は平坦面より0.5μm以上高く設けられた液晶表示装置を提供する。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

電気光学装置の製造方法、電子機器の製造方法、電気光学装置および電子機器

【課題】工程数の低減が可能な電気光学装置の製造方法および電気光学装置を提供する。

【解決手段】本発明に係る電気光学装置の製造方法は、基板の上方に、第1導電性膜を形成する工程と、第1導電性膜上に、第1導電性膜を露出する第1凹部(C2)と、平面視において第1凹部を取り囲むよう配置された第2凹部(G2)と、を有する層間絶縁膜(R1,R2)を形成する工程と、第2凹部の底面をエッチングし、第2凹部より大きい開口部を有する第3凹部(G3)を形成することにより、第2凹部の下方にオーバーハング部(OH)を形成する工程と、第1、第2および第3凹部内を含む前記層間絶縁膜上に第2導電性膜を堆積することにより、第1導電性膜と電気的に接続され、第2導電性膜よりなる画素電極を形成するとともに、第3凹部(G3)によって画素電極(PE)とその外周の第2導電性膜(30b)とを電気的に分離する工程と、を有する。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層の高導電率化工程やソース電極及びドレイン電極のエッチング工程において、半導体層にダメージを与えないような薄膜トランジスタ及びこれを用いた液晶表示装置を提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の向こう側にソース電極又はドレイン電極が形成されてなるトップゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、紫外線の表面照射によって照射された半導体層部分を高導電率化するため、半導体層へのダメージが生じない。従って、高導電率化工程及びエッチング工程のいずれにおいても半導体層はダメージを受けることがないため信頼性が向上する。

(もっと読む)

液晶表示パネル及びその製造方法

【課題】表面がMoで形成された金属配線の表面を被覆する絶縁膜として従来の保護絶縁

膜よりも極めて薄い絶縁膜を使用しながらも、トップゲート型TFTの耐湿性を確保し、

更に、層間樹脂膜の浮きや剥がれを抑制することができる液晶表示パネル及びその製造方

法を提供すること。

【解決手段】本発明の液晶表示パネル1は信号線16の表面がMoで形成されており、信

号線16の表面は厚さが0.005μm以上、0.02μm以下の窒化ケイ素からなる絶

縁膜19で被覆され、更に絶縁膜19の表面は層間樹脂膜20で被覆されている。画素電

極21とTFTのドレイン電極Dは層間樹脂膜20に設けられたコンタクトホール22を

経て電気的に接続されており、この第2開口部19aは画素電極形成前のフッ酸溶液によ

る洗浄工程により洗浄と同時に形成される。

(もっと読む)

半導体装置、表示装置、電子機器、並びに、半導体装置の製造方法

【課題】遮光層上に設けられ、光センサ等の用途に適した半導体素子と、高速駆動が可能な高性能の半導体素子とが同一の基板上に搭載されており、従来よりも部品点数が削減され、薄型化や軽量化が可能であるとともに、遮光層の有無による結晶性への影響が無い半導体装置を提供する。

【解決手段】半導体装置は、絶縁基板1上に形成されたTFT21とTFD22とを備えている。TFD22と絶縁基板1との間には、遮光層2が選択的に形成されている。TFT21およびTFD22における各半導体層5・6は、ラテラル成長結晶からなり、TFD22の半導体層6の表面には、TFT21の表面粗さよりも大きな凹凸が設けられている。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

配線基板の接続方法

【課題】端子間の短絡を防ぎ、信頼性の高い接続を実現する配線基板の接続方法を提供する。

【解決手段】基板の面上に複数並ぶ接続端子102を有する素子基板10と、基板の面上に複数並ぶ配線端子202を有するFPC基板200とを互いに対向させ、接続端子102と配線端子202とをACF210を介して接続する配線基板の接続方法であって、素子基板10は、導電性を有する基板本体を形成材料とすると共に、接続端子102の周縁に基板本体が露出する端部10eを有し、ACF210は、絶縁性の硬化性樹脂と該硬化性樹脂中に分散する導電性粒子とを有し、素子基板10とFPC基板200とが平面的に重なる領域であって、ACF210と端部10eとの間に、導電性を有さない接着剤220を配置し、素子基板10とFPC基板200とを加熱圧着する。

(もっと読む)

電気光学装置および電子機器

【課題】素子基板の基板本体として半導体基板を用いた場合でも、複雑なウエル構造や大掛かりな遮光構造を必要とせず、かつ、基板本体としてガラス基板などを用いた場合に比較して画素トランジスターの特性を大幅に向上することのできる電気光学装置、および当該電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置100の素子基板10では、基板本体として、単結晶シリコン基板からなる半導体基板11を用い、半導体基板11の表面に不純物を導入することによって、バックゲート構造を備えた画素トランジスター30の第1ゲート電極11a、および保持容量60の第1保持容量電極11bを同時形成する。また、第1ゲート絶縁層70の一部を保持容量用誘電体層70cとして利用する。

(もっと読む)

21 - 40 / 142

[ Back to top ]