Fターム[2H092MA41]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | セルフアラインメント (170)

Fターム[2H092MA41]の下位に属するFターム

裏面露光 (28)

Fターム[2H092MA41]に分類される特許

101 - 120 / 142

絶緑ゲイト型半導体装置

【課題】薄膜トランジスタにおいて、薄膜トランジスタ上に形成される配線の段切れを防止する。

【解決手段】絶縁表面上に設けられ、ソース領域と、ドレイン領域と、チャネル領域と、ソース領域とチャネル領域との間及びドレイン領域とチャネル領域との間に形成された低濃度不純物領域と、を含む半導体層と、半導体層上に設けられたゲイト絶縁膜と、ゲイト絶縁膜上に設けられたゲイト電極と、ゲイト電極の表面に設けられたゲイト電極の酸化物と、ゲイト電極の酸化物を介してゲイト電極の側面に設けられ、且つゲイト電極の側面から低濃度不純物領域と重なる領域まで延在するように設けられた窒化珪素膜と、窒化珪素膜及びゲイト電極の酸化物を介してゲイト電極の側面に設けられ、且つ窒化珪素膜を介して低濃度不純物領域と重なるように設けられたサイドウォールと、を有する薄膜トランジスタを含む。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに液晶表示装置

【課題】 リーク電流を低減する構造を持ち簡易なプロセスで製造できるTFTを提供する。

【解決手段】 絶縁基板上に下地絶縁膜11を堆積する。次に、シリコン薄膜を堆積し、レーザアニール法によりポリシリコン薄膜12を形成する。ポリシリコン薄膜12をアイランド化してゲート絶縁膜13を堆積する。次に下層ゲート電極としてマイクロクリスタルシリコン薄膜14を堆積した後、上層ゲート電極として金属膜15を続けて堆積する。これらをパターニングして多層ゲート電極を形成するとき、下層ゲート電極を上層ゲート電極よりも大きく形成する。その後、イオン注入法等によりゲート絶縁膜13を介してポリシリコン薄膜12に選択的に不純物を導入するとLDD領域19とソース・ドレイン領域18が同時に形成される。その後、上層ゲート電極をマスクとして、下層ゲート電極が露出した部位をエッチングすることにより、目的のTFT10を得る。

(もっと読む)

電気光学装置及びその製造方法、並びに導電層の接続構造

【課題】画素の開口率を高める。

【解決手段】液晶装置1は、TFTアレイ基板10上の互いに異なる層に夫々形成されており、第2層間絶縁膜42を介して互いに電気的に絶縁された上部容量電極300及び下部容量電極71、サイドウォール91、接続用導電膜93、誘電体膜75及びコンタクトホール85を備えている。接続用導電膜93によれば、コンタクトホールを形成する際のマージンを確保するために広げざるを得なかった下部容量電極71及び上部容量電極300の面積を低減でき、画素毎の開口領域の間隙に位置する非開口領域を低減することが可能である。これにより、画素における非開口領域の幅W1をサイドウォール91の幅W2に応じて低減でき、非開口領域を狭めることによって画素における開口率を高めることが可能である。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】有機薄膜を均一に形成することによって薄膜トランジスタの特性を改善する。

【解決手段】

本発明は、基板、前記基板上に形成され、互いに交差する第1及び第2信号線と、前記第1信号線と連結されているソース電極と、前記ソース電極と対向するドレイン電極と、前記ドレイン電極と連結されている画素電極と、前記ソース電極及び前記ドレイン電極上に形成され、下部が上部より広い開口部を有する隔壁と、前記開口部に位置し、前記ソース電極及び前記ドレイン電極と少なくとも一部重畳する有機半導体と、前記第2信号線と連結され、前記有機半導体と一部重畳するゲート電極とを含む薄膜トランジスタ表示板及びその製造方法に関する。

(もっと読む)

ピクセル構造を作製するための方法

【課題】ピクセル構造を作製する方法を提供する。

【解決手段】基板上に第1の導電層を形成し、第1のマスクを用いてパターニングしてゲートを形成する。基板の上方に誘電層を形成し、ゲートを覆う。誘電層の上方に半導体材料層および第2の導電層を順次形成する。第2のマスクを用いて第2の導電層をパターニングし、ピクセル電極を形成する。第1のマスクを再度用いてパターニングされたフォトレジスト層を形成することにより、ゲートの上側の半導体材料層を保護する。ピクセル電極およびパターニングされたフォトレジスト層をエッチングマスクとして用いて半導体材料層をパターニングして半導体層を形成する。パターニングされたフォトレジスト層を除去する。第3のマスクを用いて第3の導電層を形成し、パターニングしてソース/ドレインを形成する。ドレインはピクセル電極と電気的に接続される。

(もっと読む)

液晶装置

【課題】本発明の目的は、液晶表示装置の開口率の向上と透過率・反射率の向上、高視野

角の実現にある。

【解決手段】データ線110とタイミング(ゲート)線102が格子状に配置され、前記

データ線110とタイミング(ゲート)線102の交点に駆動手段112が配置された基

板101を一方の基板とした液晶装置100であって、1つ以上のストライプ構造の画素

電極108と、凸部を有する共通電極106が相対向するように載置される。

(もっと読む)

表示装置

【課題】正確な情報の入力を行うようにする為の、高精細な表示装置を提供する。

【解決手段】薄膜トランジスタを有する画素を複数有し、薄膜トランジスタの上方に設けられたソース電極及びドレイン電極と、ソース電極及びドレイン電極の上方に設けられた有機樹脂からなる絶縁膜と、絶縁膜の上方に設けられた画素電極と、画素電極に対向して設けられた対向電極と、を有する表示装置であって、アレイ状に配列されたLEDをバックライトとして用いる。

(もっと読む)

薄膜積層基板、及びその製造方法、並びに表示装置

【課題】絶縁層の段差部、及び当該段差部近傍の上層を被覆する導電層が、電気的に段切れしてショートすることを抑制することができる薄膜積層基板等を提供すること。

【解決手段】本発明の一態様に係る薄膜積層基板は、基板上に、段差構造部を有する絶縁層と、前記絶縁層の上に形成されて少なくとも前記段差構造部を被覆する導電層と、を備える薄膜積層基板であって、前記段差構造部は、前記基板から離れるに従って段差部の底辺の幅が狭くなるように形成された順テーパー形状をなしており、少なくとも前記絶縁層の前記段差構造部に、少なくとも1種類の不純物がドーピングされている。

(もっと読む)

TFT基板及びTFT基板の製造方法

【課題】製造工程の工程数を削減することによって、製造コストを大幅に低減でき、かつ、製造歩留りを向上させることが可能なTFT基板及びTFT基板の製造方法の提案を目的とする。

【解決手段】ガラス基板10と、ゲート電極23及びゲート配線24と、ゲート絶縁膜30と、n型酸化物半導体層40と、酸化物導電体層60を具備し、チャンネル部41を保護するチャンネル部用エッチストッパー53と、酸化物導電体層60を有する、ソース配線65,ドレイン配線66,ソース電極63,ドレイン電極64及び画素電極67とを備えている。

(もっと読む)

スタンプ及びスタンプ製造方法、ナノパターン形成方法、並びにそれを利用した薄膜トランジスタの製造方法及び液晶表示装置の製造方法

【課題】スタンプ製造方法、それを利用した薄膜トランジスタ及び液晶表示装置の製造方法を提供する。

【解決手段】本発明は、基板との接触性が向上したスタンプ(Stamp)の製造方法を提供し、前記スタンプを利用して、基板上に帯電された領域を作った後に、前記帯電領域の電荷と反対電荷に帯電されたナノ物質を塗布又はメッキさせて、セルフアセンブリ(self−assembled)を介して自己組織化単分子膜(SAM;self−assembled monolayer)を形成することによって、精密なナノパターンを有する薄膜トランジスタ及び液晶表示装置の製造方法を提供し、これによって素子の性能を向上させることができる。

(もっと読む)

フォトレジスト組成物及びそれを用いた薄膜トランジスタ基板の製造方法

【課題】 本発明はフォトレジスト組成物及び前記フォトレジスト組成物を用いた薄膜トランジスタ基板の製造方法を提供する。

【解決手段】フォトレジスト組成物はノボラック樹脂及びアクリル樹脂を含む混合樹脂100重量部及びナフトキノンジアゾスルホン酸エステル10〜50重量部を含む。前記ノボラック樹脂の重量平均分子量は30000以上であり前記アクリル樹脂の重量平均分子量は20000以上である。前記アクリル樹脂の含量は全体混合樹脂の1〜15重量%である。前記フォトレジスト組成物は薄膜トランジスタ基板の製造工程のパターン形成の際、リフローによるプロファイルの角度変化を最小化し、パターンの構造の安定性及び残膜厚さ均一性を向上させることで配線のショート及びオープン不良を減少させることができる。

(もっと読む)

半導体装置、半導体装置の製造方法、並びに電気光学装置

【課題】LDD又はGOLD構造を有し、微細化に対応できるとともに歩留まりを向上させることができ、工程を簡略化できる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体膜上の全面にレジストを形成し、第1遮光部91aと、第1透光部91bと、第1遮光部91aと第1透光部91bとの間に配置された半遮光部91cとを備えたハーフトーンレクチル91と、露光時に少なくとも第1遮光部91aおよび半遮光部91cの一部が配置されるべき位置に位置合わせされる第2遮光部92aと第2遮光部92aに隣接して配置された第2透光部92bとを備えたバイナリレクチル92とを用いてレジストを露光することによってソース側高濃度領域及びドレイン側高濃度領域に対応するレジストの膜厚を、ソース側低濃度領域、ドレイン側低濃度領域及びチャネル領域に対応するレジストの膜厚より薄く形成するレジスト形成工程を有する。

(もっと読む)

液晶表示装置およびその製造方法

【課題】表示装置の遮光性及び配向性を同時に改善する。

【解決手段】基板11上に透明な画素電極31を駆動するための薄膜トランジスタが設けられ、この薄膜トランジスタの上層でかつ画素電極11の下層の位置に導電性の遮光層が設けられている液晶表示装置において、第一の平坦化膜25が薄膜トランジスタの凹凸を埋める様に形成されており、その平坦化された第一の平坦化膜25の上に遮光層が配され、第二の平坦化膜29が遮光層の段差を埋める様に形成されており、その平坦化された第二の平坦化膜29の上に画素電極31が配されており、導電性の遮光層は、第一の遮光層27と第二の遮光層28とに分離しており、第一の遮光層27は画素電極31に接続しており、第二の遮光層28は共通電位にある。

(もっと読む)

表示装置

【課題】 アクティブマトリクス型の表示装置の作製工程又は完成品における静電気による不良の発生を抑制する。

【解決手段】 本発明に係る表示装置は、アクティブマトリクス回路の角の部分に隣接して、前記アクティブマトリクス回路に接続されていない格子状の放電パターンが形成されていることを特徴とする。また、本発明に係る表示装置は、アクティブマトリクス回路の周辺に、前記アクティブマトリクス回路を構成するゲイト線又はソース線と交わる放電パターンが形成され、前記放電パターンの長さは、前記アクティブマトリクス回路の画素ピッチよりも長いことを特徴とする。これらにより、各種静電破壊によるアクティブマトリクス型表示装置の不良の発生を抑制することができる。

(もっと読む)

電気光学装置及びその製造方法、電子機器並びにコンデンサー

【課題】 電気光学装置において、保持容量を大きくし、高品位の画像表示を行う。

【解決手段】 電気光学装置は、基板上に、相互に交差する複数の走査線及び複数のデータ線と、複数の走査線と複数のデータ線との交差に対応して設けられた複数の画素電極と、一対の電極及び誘電体膜が積層されてなる蓄積容量とを備える。更に、一対の電極の一方及び誘電体膜を貫通して開口された開口部の内側壁上に設けられた第1の絶縁膜からなるサイドウォールと、一対の電極の他方から見て、前記一方に対して反対側に配置され、サイドウォールと同時に自己整合的に形成されサイドウォールに囲まれたセルフアラインコンタクトホールを介して他方と電気的に接続された第1の導電膜とを備える。

(もっと読む)

液晶表示装置

【課題】階調表示を実現させるための全く新しい方法を提案する。

【解決手段】複数の画素を含む画素領域と、複数の画素と電気的に接続された保護回路とを有し、前記複数の画素は、第1の電極と第2の電極、第1の電極と第2の電極の間に印加される電圧によって配向状態が制御される液晶とを有し、1画像を表示する期間において、第1の電極に信号電圧を複数回入力してアナログの階調を表示し、前記第2の電極にはオフセット電圧を入力する。

(もっと読む)

平面電子表示装置及びその製造方法

【課題】Cuに添加する添加元素が、Cu部材と接触するガス雰囲気又は固体に含まれる酸素と優先的に反応してCuの酸化を抑止する酸化被膜を形成することができる高導電率の配線、電極等を備える平面電子表示装置を提供する。

【解決手段】基板上にマトリックス状に交叉する電極線17、18と、その交点に配置された液晶画素20と、外部の駆動回路に接続された端子電極とを有するアクティブマトリックス方式の液晶表示装置において、電極線17、18、電極、配線層、端子電極のうちの少なくとも一つを銅を主成分とし、基板との界面に銅に添加した添加元素の酸化物層を形成する銅合金で形成する。この添加元素は、酸化物形成自由エネルギーがCuより小さく、Cu中における拡散係数がCuの自己拡散係数より大きく、Cu中における1at.%当たりの電気抵抗上昇率が5μΩ・cm以下であり、Cu中における活量係数γが、活量係数γ>1の関係を満足する。

(もっと読む)

表示装置

【課題】遮光性能を向上させ、光リーク電流による画質低下を抑えることができる表示装

置を提供する。

【解決手段】石英ガラス基板11上に画素電極31の駆動用の多結晶SiTFTが設けら

れた表示装置において、第1の金属層27、28を多結晶SiTFTの上層でかつ画素電

極31の下層の平坦化された層間絶縁膜25上に設け、第2の金属層21、22を多結晶

SiTFTの上層でかつ第1の金属層27、28の下層の位置に設ける。第1の金属層2

7、28は、画素部において第2の金属層21、22と接続された部分を有しかつその端

部が平坦化された層間絶縁膜25上に設けられる。第1の金属層27、28と第2の金属

層21、22とが重なり合って画素開口領域以外の領域を覆う。

(もっと読む)

液晶表示装置用アレイ基板及びその製造方法

【課題】マスク工程をさらに単純化して製造費用を節約し、製造時間を短縮することによって、工程収率を改善することのできる液晶表示装置用アレイ基板とその製造方法を提供すること。

【解決手段】本発明による液晶表示装置用アレイ基板は、第2マスク工程時、相互に異なるスリットの幅の半透過部を有するマスクを利用して製造される。ここれにより、感光層をアッシングする工程で、配線が位置した部分と、そうではない部分に対するエッチングの比率を合わせることができるために、配線の表面に欠陥が発生する不良を防げる長所がある。また、本発明では、アレイ基板を3マスク工程により製造することを特徴とする。

(もっと読む)

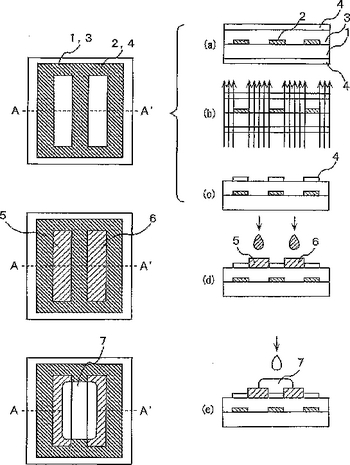

電極基板,薄膜トランジスタ,表示装置、及びその製造方法

本発明は、下部電極をフォトマスクに利用して、絶縁膜上に下部電極と概ね同一パターン形状の撥液領域と概ね反転パターン形状の親液領域を形成して、親液領域内に導電性インクを塗布焼成して、下部電極に対して概ね反転パターン形状の上部電極を自己整合して形成するため、印刷法を用いても位置ずれが発生しない。このため、アクティブマトリクス型薄膜トランジスタ基板などの半導体装置が印刷法を用いて形成できる。  (もっと読む)

(もっと読む)

101 - 120 / 142

[ Back to top ]