Fターム[2H092NA23]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | 素子性能の向上 (1,705) | 寄生容量の低減 (220)

Fターム[2H092NA23]に分類される特許

81 - 100 / 220

半導体装置及び当該半導体装置の作製方法

【課題】半導体層をゲート電極層、ソース電極層及びドレイン電極層上に設ける場合であっても、素子特性を向上させると共に、素子の信頼性を向上させることを目的の一とする。

【解決手段】ゲート電極層と、ゲート電極層上に設けられたゲート絶縁層と、ゲート絶縁層を介してゲート電極層の一部と重なるように設けられたソース電極層及びドレイン電極層と、ゲート絶縁層、ソース電極層及びドレイン電極層上に設けられた半導体層を有する構造において、ソース電極層とドレイン電極層の間の領域に位置するゲート絶縁層の膜厚を、ゲート電極層とソース電極層の間に設けられたゲート絶縁層及びゲート電極層とドレイン電極層の間に設けられたゲート絶縁層の膜厚より小さくなるように設ける。

(もっと読む)

表示装置

【課題】画素電極とソースバスラインとの間に形成される寄生容量に起因する表示不良の発生を抑制することのできる表示装置を提供する。

【解決手段】ソースバスラインの駆動順序に応じて順次に選択状態とされる第1のゲートバスラインと第2のゲートバスラインとが、表示部100に形成された画素マトリクスの各行に対応して設けられる。各画素形成部には、第1のゲートバスラインにゲート端子が接続されたTFT10aと第2のゲートバスラインにゲート端子が接続されたTFT10bとが設けられる。各ゲートバスラインにゲート端子が接続されたTFTのソース端子は、当該各ゲートバスラインが選択状態とされたときに相対的に(ソースバスラインの)駆動順序の遅い側に配設されているソースバスラインに接続される。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを複数個直列に設ける場合、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供することにある。

【解決手段】複数個あるTFTの少なくとも一部について、半導体膜とゲート電極膜が対向する面積のチャネル領域に対する相対的な面積が異なることにより、光リーク電流の発生を抑えつつ、容量増加を抑制する構造の平面ディスプレイを提供する。

(もっと読む)

表示装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少なくとも一部の回路を、酸化物半導体を用い、かつゲート電極層と重なるチャネル形成領域となる酸化物半導体層上にチャネル保護層が設けられた逆スタガ型薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを複数個直列に設ける場合、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供することにある。

【解決手段】直列に設けれた複数個のチャネル領域のチャネル端のうち、映像信号線側及び画素電極側の最も近くに位置するチャネル端の外側に、対向するゲート端が位置し、当該チャネル端以外のチャネル端のうち少なくとも一つにおいて、チャネル端がゲート端のより近くに位置している。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、導電層41と第2酸化物半導体層40が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部と第2酸化物半導体層40の側面部及び上面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークを低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

液晶表示装置

【課題】補助容量配線とは別体の透明な補助容量用下電極を設けることにより、補助容量

を従来例の液晶表示装置よりも増大化させることができ、開口率が大きく、しかも、フリ

ッカやクロストーク等が生じ難い液晶表示装置を提供すること。

【解決手段】補助容量線13と電気的に接続される透明導電性の補助容量用下電極15と

、走査線12、補助容量線13及び補助容量用下電極15を覆う第1絶縁膜16と、TF

Tを覆う第2絶縁膜19と、第2絶縁膜19を貫通するコンタクトホール20によってT

FTと電気的に接続された透明導電性の画素電極21とを備え、補助容量用下電極15と

画素電極21と第1、第2絶縁膜16、19とで補助容量を構成する。

(もっと読む)

回路装置およびその検査方法

【課題】 回路と接続端子を接続する信号線にさらに検査用端子を接続すると、寄生容量が増加して回路動作を行う際の負荷が大きくになる。

【解決手段】 基板(8)に設けられた回路(2)と、

前記基板の前記回路とは離れた位置に設けられ、前記回路の入力または出力信号を中継する接続端子(4)と、

前記回路と前記接続端子とを接続する信号配線(3)と、

前記基板に前記接続端子とは別に設けられた複数の検査用端子(6)と、

前記信号配線から分岐し、前記複数の検査用端子の1つに接続された分岐配線(31)と、

を有する回路装置であって、

前記分岐配線の、前記分岐と前記検査用端子との間にスイッチ(1)が設けられていることを特徴とする回路装置。

(もっと読む)

薄膜トランジスタ、および薄膜トランジスタアレイ

【課題】 薄膜トランジスタの特性を良好にすると同時に、蓄積容量部に形成される金属−絶縁体−半導体構造(MIS構造)を解消しキャパシタの値を安定化させることで、フォトマスク工程数を削減しても高い性能を維持できる薄膜トランジスタ及びそれを用いた表示装置を提供する。

【解決手段】 4回以下のフォトマスク工程数で作製される薄膜トランジスタ部216と、蓄積容量部217とを有する薄膜トランジスタアレイ基板において、チャンネルの形成に寄与しない活性半導体層をシリサイド化する。

(もっと読む)

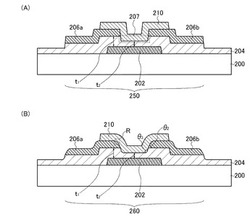

半導体装置及び半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられた順スタガ型(トップゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

薄膜トランジスタ、アクティブマトリックス回路並びに表示装置

【課題】フィードスルー電圧ΔVがTFT基板全面において一定である薄膜トランジスタ、該薄膜トランジスタから構成されるアクティブマトリックス回路を用いることにより画素ごとの表示特性のバラツキに影響を及ぼすことの無い画像表示装置を提供する。

【解決手段】ソース電極1003は、長手をy方向に延設される少なくとも1つの矩形で、ゲート電極1002の上の目標位置に配置される領域S2からなり、ドレイン電極1004は、ゲート電極1002の上をx方向に横断し、該ゲート電極1002両端からのはみ出し部分それぞれの長さが△d以上である矩形の領域D1と、領域D1からy方向に延設され領域S2と長手方向同士を並行に隣接してチャネル部を形成する矩形で、該矩形の長手方向の一端部が最も近いゲート電極1002の端部位置よりも△d以上内側となるゲート電極1002の上の目標位置に配置される領域D2と、からなる。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、画像信号に乗る電磁ノイズを低減して高品位の画像表示を図る。

【解決手段】電気光学装置は、基板上に、走査線と、走査線と交差するデータ線と、画素毎に設けられた画素電極と、(i)走査線に接続されたゲート電極、並びに(ii)データ線に接続されたソース領域、画素電極に接続されたドレイン領域、及びチャネル領域を有する半導体層を有する薄膜トランジスタと、半導体層及び画素電極間に積層され、ドレイン領域及び画素電極間を中継接続する中継配線と、データ線及び中継配線間に積層され、所定電位に保持される第1シールド層と、画素電極及び中継配線間に積層され、所定電位に保持される第2シールド層とを備える。

(もっと読む)

表示装置及びその製造方法

【課題】ボトムゲート構造を有する薄膜トランジスタを含む表示装置において、遮光層とゲート電極との間の寄生容量の発生を軽減しつつ、光リーク電流の発生の抑制を図ることが可能になる表示装置を提供すること。

【解決手段】表示装置は、半導体層への光の入射を抑制するための遮光層(40)と、第1絶縁膜(31)と、薄膜トランジスタのゲート電極(22)と、第2絶縁膜(32)と、半導体層(21)と、が順次積層された基板を含む。遮光層(40)は、ゲート電極(22)の少なくとも一部が遮光層(40)と第1絶縁膜(31)を介して重ならないようにして形成される。

(もっと読む)

アレイ基板、これの製造方法、及びこれを有する液晶表示装置

【課題】液晶表示装置の表示品質を向上することが可能なアレイ基板、このアレイ基板の製造方法、及びこれを有する液晶表示装置を提供する。

【解決手段】アレイ基板は、互いに電気絶縁状態で交差するゲートライン及びデータラインと、ゲートライン及びデータラインに接続されるスイッチング素子とが形成される基板と、データライン及びゲートラインに沿って上側に形成されたアウトライン部と、データライン及びゲートラインと交差する方向に各々延長されてアウトライン部に接続され、アウトライン部によって定義された画素領域を複数のドメインに分割する複数の接続部と、各ドメインにおいて接続部の側面から突出されてアウトライン部に接続される複数のスリット部を含む画素電極と、データライン及びゲートラインの上部において、アウトライン部に沿って形成されてデータライン及びゲートラインを覆うように(shielding)、データラインとアウトライン部との間に形成された遮蔽電極とを含む

(もっと読む)

液晶表示装置

【課題】フリッカを低減することが可能な液晶表示装置を提供することである。

【解決手段】

マトリックス状に複数の画素が配置され、液晶層を介して対向配置される第1及び第2の基板と、前記第1の基板側に、少なくとも各画素内に面状に形成された第1電極と、前記第1電極の上層に第1絶縁層を介して形成され、各画素毎に前記第1電極に重畳して形成される線状の複数の第2電極とを有し、前記第1電極と前記第2電極で生じる電界で前記液晶層を駆動する液晶表示装置であって、前記第1電極と同電位であり、前記第2電極と同層に形成され、前記各第2電極を間にして配置される線状の第3電極を備えた液晶表示装置である。

(もっと読む)

アレイ基板及びこれを有する液晶表示装置

【課題】アレイ基板及びこれを有する液晶表示装置を提供する。

【解決手段】アレイ基板は、ゲート線と、ゲート線と電気的に絶縁状態で交差するように延長されたデータ線とが形成された基板と、ゲート線及びデータ線に接続されたスイッチング素子と、基板上に定義された画素領域に形成され、スイッチング素子の出力電極に接続された画素電極と、画素領域及び画素領域の間に対応して、データ線が形成された基板上に画素電極と絶縁されるように形成され、データ線の上部に対応する位置に1つ以上の第1スリットが形成された共通電極とを備える。

(もっと読む)

表示装置

【課題】ソース電極およびドレイン電極とゲート電極との間の寄生容量の変化に起因するフリッカを抑制するとともに、薄膜トランジスタの動作速度の向上を図ることが可能な表示装置を提供する。

【解決手段】この表示装置100の薄膜トランジスタ1のソース電極6およびドレイン電極7からなるチャネル領域5aは、それぞれ、ゲート電極31および半導体層5と重なり、ソース電極6およびドレイン電極7の少なくとも一部は、平面的に見て、ゲート電極31の延びるY方向に対して所定の角度(45度未満)傾斜した状態で互いに略平行に対向して延びている。

(もっと読む)

液晶表示装置

【課題】寄生容量を発生させることなく、配向膜ストッパを形成することのできる液晶表示装置の提供。

【解決手段】液晶を挟持して対向配置される第1基板と第2基板と、前記第1基板と前記第2基板の固定を兼ねて前記液晶を封入するシール材とを備える液晶表示装置であって、

前記第1基板は、少なくとも、前記シール材で囲まれる領域に形成される複数の画素を駆動させるための信号線と、該信号線をも被って形成される絶縁膜を介して前記シール材との間に間隙を有して配置される配向膜と、前記配向膜と前記シール材との間の間隙に前記配向膜を囲んで形成される線状の導電膜を有し、

前記導電膜は、平面的に観て、前記信号線のうち前記配向膜と前記シール材との間の間隙に配置される信号線と重畳されて形成されているとともに、該信号線と同電位に保持されている。

(もっと読む)

半導体装置、半導体装置の製造方法および表示装置ならびに電子機器

【課題】寄生容量の増加による表示特性の低下、および半導体層下のゲート電極と同一の金属層のレイアウトに依存する半導体層のレーザアニール時の結晶性の勾配発生を抑制し、輝度ムラを解決すること。

【解決手段】本発明は、ガラス基板40上に形成される第1電極41と、第1電極41上に第1絶縁膜51を介して形成される伝熱金属層61と、伝熱金属層61上に形成される第2絶縁膜52を介して形成される半導体層50と、半導体層50上に形成される第2電極42および第3電極43とを有する半導体装置である。

(もっと読む)

薄膜トランジスタおよびそれを用いた装置

【課題】薄膜トランジスタの構成部材の位置ずれを抑制し、さらに寄生容量の低減を図った薄膜トランジスタおよびそれを用いた装置の提供。

【解決手段】絶縁基板上に、ソース電極、ドレイン電極、前記ソース電極と前記ドレイン電極に電気的に接続される半導体層と、少なくとも前記半導体層上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に前記半導体層と重畳して配置されるゲート電極を備えるものであって、

前記ソース電極上に重ねられて第1バンク絶縁膜、前記ドレイン電極上に重ねられて第2バンク絶縁膜が形成され、

前記半導体層、ゲート絶縁膜、およびゲート電極は、前記第1バンク絶縁膜と前記第2バンク絶縁膜の間の領域に形成されている。

(もっと読む)

81 - 100 / 220

[ Back to top ]