Fターム[2H092NA23]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | 素子性能の向上 (1,705) | 寄生容量の低減 (220)

Fターム[2H092NA23]に分類される特許

61 - 80 / 220

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

液晶装置および液晶装置の製造方法、並びに電子機器

【課題】横方向電界で液晶分子を回転させる方式を用いた場合、液晶は電極に対して基板から離れた方向に配置される。つまり、基板側に生じる電界は液晶分子の回転に寄与しない。そのため、電界の利用率が低下する。また、電気抵抗が低い結晶型ITOを用いた場合、ドライエッチングでは残渣が残り、ウェットエッチングでは寸法精度が出せないという課題がある。

【解決手段】電極間に位置する誘電体をエッチングして逆テーパー状に窪ませることで、電界強度が強い電極間に液晶が入る領域を設けた。窪ませた部分の液晶分子も電界により回転するため電界の利用率を向上させることができる。また、逆テーパー状に誘電体が形成されているため、スパッター法等で結晶型ITO膜を形成した場合、自己整合的にITO膜が分離されるため、ITOをエッチングすることなく所望のパターンを形成することが可能となる。

(もっと読む)

TFT−LCDアレイ基板及びその製造方法

【課題】基板に形成された複数のゲートライン及び複数のデータラインを含み、ゲートラインとデータラインにより複数の画素領域が画定され、画素領域ごとに画素電極及びスイッチング素子としての薄膜トランジスタが形成されるTFT−LCDアレイ基板を提供する。

【解決手段】本発明は、TFT−LCDアレイ基板及びその製造方法に関する。アレイ基板には、基板に形成された複数のゲートライン及び複数のデータラインが含まれる。前記ゲートラインとデータラインにより複数の画素領域が画定され、画素領域ごとに画素電極及びスイッチング素子としての薄膜トランジスタが形成されている。前記薄膜トランジスタのゲート電極は連結電極を介して対応したゲートラインに電気的に接続され、前記ゲート電極と前記ゲートラインは異なる材料層により形成される。

(もっと読む)

液晶表示パネル、液晶表示モジュール、および液晶表示装置

【課題】他のパネルと接続されていない単独の状態の液晶表示パネルでも、ソースバスライン容量に依存する消費電流の低減を可能とする。

【解決手段】液晶表示パネルは、アクティブマトリックス型の液晶表示パネルであって、上記液晶表示パネル内における複数の画素領域の少なくとも1つに、当該画素領域内に設けられているソースバスラインS1〜SxのON/OFFを切り換える切換部Tr11〜Trxyが備えられている。

(もっと読む)

半導体装置の作製方法

【課題】大面積な半導体装置を低コストに提供することを目的の一とする。または、nチャネル型トランジスタ及びpチャネル型トランジスタに最適な結晶面をチャネル形成領域とすることにより、性能向上を図ることを目的の一とする。

【解決手段】絶縁表面上に(211)面から±10°以内の面を上面とする島状の単結晶半導体層を形成し、単結晶半導体層の上面及び側面に接して形成し、且つ絶縁表面上に非単結晶半導体層を形成し、非単結晶半導体層にレーザー光を照射して非単結晶半導体層を溶融し、且つ、単結晶半導体層を種結晶として絶縁表面上に形成された非単結晶半導体層を結晶化して結晶性半導体層を形成し、結晶性半導体層を用いて、nチャネル型トランジスタ及びpチャネル型トランジスタを形成する。

(もっと読む)

電気光学装置用基板、電気光学装置及び電子機器

【課題】画素電極における走査線の電位変動の影響を抑制する。

【解決手段】電気光学装置用基板は、基板(301)上に、互いに交差する複数の走査線(40)及び複数のデータ線(50)と、複数の走査線及び複数のデータ線の交差に対応して設けられた複数の画素電極(21)と、複数の画素電極に夫々対応し、対応する画素電極をスイッチング制御する複数の半導体素子(24)とを備える。基板上で平面的に見て、複数の半導体素子のうち少なくとも一の半導体素子は、一の半導体素子に対応する一の画素電極に隣り合う他の画素電極に少なくとも部分的に重なるように配置されている。

(もっと読む)

液晶表示装置及びその製造方法

【課題】FFSモードの液晶表示装置において、保持容量を増加させることなく液晶に印加される電界強度を維持又は増加させ、液晶駆動電圧の低電圧化、及びこれにともなう信号線ドライバー回路の発熱防止、高フレームレート化を実現する。

【解決手段】液晶の誘電率よりも誘電率の小さい絶縁層をコモン電極と複数のスリットが設けられている画素電極との間に設け、画素電極のスリット下の絶縁層の厚さを画素電極の透明導電層下の絶縁層の厚さよりも薄くなるように絶縁層をエッチングする。これにより、スリット下の絶縁層には凹部が形成され、液晶に印加される電界強度が増加し、より低電圧駆動が可能となる。また、絶縁層を一様に薄くするものではないため、保持容量の増加は少ない。

(もっと読む)

電気光学装置及び電子機器

【課題】 クロストークを防止する。

【解決手段】電気光学装置は、基板(7)上に第1電極(131)及び第2電極(132)からなる電気光学素子と、データ電位が供給される第1データ線(6a)及び第1電極間に設けられ、第1期間でオン状態、第2期間でオフ状態となる第1スイッチング素子と、データ電位が供給される第2データ線(6b)及び第2電極間に設けられ、第1期間でオフ状態、第2期間でオン状態となる第2スイッチング素子と、を備える。そして、基板を平面視すると、第2電極は、その少なくとも一部が第1及び第2データ線と重なるように形成され、第1電極は、その両側辺がそれぞれ第1及び第2データ線それぞれの幅の内に収まるように、形成される。

(もっと読む)

液晶表示装置

【課題】表示品位の劣化を防止し、かつ、輝度傾斜の発生を防止する液晶表示装置を提供することができる。

【解決手段】第1基板101は、表示画素PXのそれぞれに配置された第1電極PEと、絶縁層を介して第1電極PEと対向するように配置された第2電極CEと、表示画素PXの配列する行に沿って第1電極PEの周囲の領域に配置された走査線YLと、を有し、第1電極PEは、第2電極CEとの間に電界を生じさせるためのスリットSTを有し、液晶層LQに含まれる液晶分子の初期配向方向は、走査線YLと第1電極PEとの間に生じる電界の方向と略同一であって、スリットSTは液晶分子の初期配向方向に対応して液晶分子の配向方向を制御可能な電界を生じさせるように配置されている液晶表示装置。

(もっと読む)

アクティブ素子基板の製造方法、アクティブ素子基板、アクティブ型表示装置

【課題】工数の増加を伴うことなく、寄生容量を抑制できるとともに、高開口率および高透過率を示すアクティブ素子基板の製造方法を実現する。

【解決手段】画素TFT7および信号配線上に、コンタクトホール9a・10aを有する透明な絶縁層9・10を形成する工程を備え、該工程は、画素TFT7および信号配線を覆うように、感光性を有さない第1の絶縁層9を形成する工程と、第1の絶縁層9を覆うように、感光性を有する第2の絶縁層10を形成する工程と、第2の絶縁層10を露光および現像により、パターニングする工程と、第2の絶縁層10をマスクとして上記第1の絶縁層9をエッチングする工程とを含む。

(もっと読む)

薄膜トランジスタ基板ならびに液晶表示素子およびその製造方法

【課題】配線や電極等による段差に起因する配向処理むらを抑制し、配向不良の発生を低減でき、充電時間を短くできるTFT基板の提供。

【解決手段】基材2と、基材上に形成されたゲート線と、ゲート絶縁層4と、オーバーコート層6と、ソース線と、画素電極8と、基材2上に形成されゲート線に接続されたゲート電極13、TFT用ゲート絶縁層14、TFT用ゲート絶縁層上に形成された半導体層15、TFT用ゲート絶縁層および半導体層の上に上記オーバーコート層と連続して形成されたTFT用オーバーコート層16、TFT用オーバーコート層上に形成され、ソース線に接続され、半導体層にソース電極用コンタクトホールh1を介して接続されたソース電極17、および、TFT用オーバーコート層上に形成され、画素電極に接続され、半導体層に透明電極用コンタクトホールh2を介して接続された透明電極18を有するTFT10とを有する。

(もっと読む)

表示素子用基板装置

【課題】表示の均一化が可能なアレイ基板を提供する。

【解決手段】複数の第1配線部31中の最も外側の位置でのライン/スペース比と、最も外側に位置する第1配線部31a1,31b1と第1配線部31a1,31b1の外側に配置した第2配線部40とのライン/スペース比とを略等しく設定する。第1配線部31全体に亘って寄生容量を均一化し、第1配線部31と接続した各薄膜トランジスタを介して、表示の均一化が可能になる。

(もっと読む)

液晶表示装置

【課題】液晶表示装置に外力が加わっても導電膜と共通電極がショートする現象を防止でき、液晶表示装置の表示特性を向上できる上部基板を有する液晶装置を提供する。

【解決手段】画像を表示する表示部と前記表示部を駆動するために駆動信号を提供する駆動部とを備え、前記駆動部は相互に異なる層に配置される第1導電パターン及び第2導電パターンを電気的に接続するための導電膜を具備している、下部基板、共通電極と前記共通電極上に具備され前記共通電極と前記導電膜を互いに絶縁する絶縁部材とからなる上部基板、及び、前記下部基板と前記上部基板との間に介在する液晶層、を含むことを特徴とする。

(もっと読む)

半導体装置、およびその作製方法

【課題】アクティブマトリクス型表示装置等の半導体装置において、トランジスタの駆動能力を低下させることなく寄生容量の容量値を低減することを課題の一とする。または、寄生容量の容量値を低減した半導体装置を低コストに提供することを課題の一とする。

【解決手段】トランジスタのゲート電極と同一の材料層で形成される配線と、ソース電極またはドレイン電極と同一の材料層で形成される配線との間に、ゲート絶縁層以外の絶縁層を設ける。

(もっと読む)

薄膜トランジスタ、表示装置及びこれらの製造方法

【課題】ボトムゲート型自己整合型のTFTにおいて、ゲート電極の幅を最小加工寸法程度の幅とし、寄生容量が小さいTFTを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層に、ゲート電極をマスクにして紫外線を裏面照射することにより、自己整合型のTFTを形成する。紫外線照射された半導体層は紫外線の回折の影響によりゲート電極より少し内側までソース電極、ドレイン電極として機能する程度に高導電化し、チャネル長はゲート電極の幅よりも少し短い長さとなる。これにより、ゲート電極の幅を最小加工寸法程度に短縮することが可能となり、その結果、TFT寄生容量も低減させることができる。

(もっと読む)

液晶表示装置

【課題】表示部に穴をあけた液晶表示装置において、各配線の寄生容量の均一化を図る。

【解決手段】穴10近辺の遮光層11下において、終端された走査線4および補助容量線5の幅を表示領域2における走査線4および補助容量線5の幅よりも広くする。これにより、遮光層11下において各配線により形成される容量が表示領域2において各配線により形成される容量よりも大きくなるので、各配線の寄生容量の均一化を図ることができ、表示ムラの発生が抑制される。

(もっと読む)

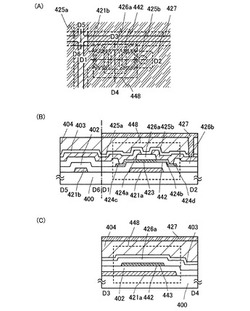

アレイ基板及びその製造方法

【課題】液晶表示装置のアレイ基板及びこれの製造方法を提供する。

【解決手段】第1スイッチング素子は第1データライン171aに接続され、第2スイッチング素子は第1データラインに隣接する第2データライン171bに接続される。第3スイッチング素子は第1データラインと第2データラインとの間に配置されるデータ電源ライン171cに接続される。第4スイッチング素子はゲートライン121と平行であり、データ電源ラインの電圧と異なる極性を有する電圧が印加されるゲート電源ライン125に接続される。これにより、アレイ基板の透過率、開口率、及び表示特性が向上される。第1及び第2画素電極(191a,191b)と、第1及び第2共通電極(191c,191d)とに極性が異なる電圧を印加すると、アレイ基板の表面にほぼ平行な電界が生成される。

(もっと読む)

液晶表示素子および表示装置

【課題】寄生容量を抑制した状態で開口率を向上させることが可能な液晶表示素子および表示装置を提供する。

【解決手段】第1基板10上にマトリクス状に配置された複数の走査線11および複数の信号線12と、走査線11および前記信号線12の交差部に配置されたTFT1と、TFT1を覆う状態で、第1基板10上に設けられた第1絶縁膜13と、第1絶縁膜13上に配置された共通電極14と、共通電極14を覆う状態で、第1絶縁膜13上に配置された第2絶縁膜15と、画素領域1A内の第2絶縁膜15上に配置され、第2絶縁膜15および第1絶縁膜13に設けられたコンタクトホールを介してTFT1と接続された複数のスリット16aを有する画素電極16とを備え、共通電極14は、第1絶縁膜13上のコンタクトホールの形成領域を除く画素領域10Aと、走査線11および信号線12の少なくとも一方とを覆う状態で配置されている。

(もっと読む)

液晶表示装置

【課題】 配線容量の低減を図り、液晶表示装置の高精細化や狭額縁化を図る。

【解決手段】 走査線及び信号線の交点に配列されるスイッチング素子12と、マトリクス状に配置されスイッチング素子によって駆動される画素電極と、画素電極の印加電圧を保持するための保持容量とを有するアレイ基板2と、対向電極を有し、アレイ基板2と所定の間隔を隔てて対向配置される対向基板3とを備え、これらアレイ基板2と対向基板3の間に液晶層が封入されてなる液晶表示パネル1を備えた液晶表示装置である。アレイ基板2の電源配線及び電気信号配線の少なくとも一部(例えば保持容量配線13や額縁領域の引き出し配線41)は、配線上に誘電率の低い絶縁性着色層(青色絶縁性着色層21)が積層された構造を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少なくとも一部の回路を、上下をゲート電極で挟んだ酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部及び駆動回路を設けることによって製造コストを低減する。

(もっと読む)

61 - 80 / 220

[ Back to top ]