Fターム[4G077TK06]の内容

結晶、結晶のための後処理 (61,211) | 基板 (1,853) | 結晶方位 (253)

Fターム[4G077TK06]に分類される特許

161 - 180 / 253

配向層の形成方法、結晶製造方法、基板、半導体素子、およびIII族窒化物半導体の製造方法

【課題】クラックを生じさせることなく良質な結晶を歩留まりよく製造する方法を提供する。

【解決手段】単結晶基板1上に第1の薄膜2を製膜して第1の薄膜2表面を摩擦することにより摩擦配向層3を形成し、さらに摩擦配向層3の上に第2の薄膜を堆積することにより堆積配向層4を形成し、その上に結晶を成長させる。単結晶基板1はSi基板とし、その面方位は(111)とする。また、摩擦配向層3の厚さは1〜20mmとし、その形成工程において、第1の薄膜2をダイアモンド、サファイアまたはSiCで摩擦する。

(もっと読む)

SiCエピタキシャル膜付き単結晶基板の製造方法

【課題】SiCエピタキシャル膜中の結晶欠陥を減少させて結晶品質を改善させたSiCエピタキシャル膜付き単結晶基板の製造方法を提供する。

【解決手段】オフカットされたSiC単結晶基板1上にSiCエピタキシャル膜2を成膜する成膜工程と、SiCエピタキシャル膜2を加熱することでSiCエピタキシャル膜2の表面にステップバンチング3を発生させて結晶欠陥を減少させる加熱工程とからなる。また、デバイスを作製するために、このSiCエピタキシャル膜2の表面に発生させたステップバンチング3をCMP(化学的機械研磨)あるいは水素雰囲気中でのガスエッチング等により除去する平坦化工程を追加しても良い。

(もっと読む)

III族窒化物半導体薄膜、III族窒化物半導体発光素子およびIII族窒化物半導体薄膜の製造方法

【課題】良質のIII族窒化物半導体薄膜およびそれを用いたIII族窒化物半導体発光素子を提供すること。

【解決手段】C3結晶軸に対して−0.1°〜0.9°のオフ角を有する(1−102)面(いわゆるr面)のサファイア基板110上に、サファイア基板110の温度を1100℃〜1400℃の範囲内に制御しつつ、トリメチルガリウムを200〜500μmol/minの流量で導入することにより、サファイア基板110上に(11−20)面(いわゆるa面)のGaN層120をエピタキシャル成長させる。これにより良質のIII族窒化物半導体薄膜(a面GaN層)を得る。また、そのIII族窒化物半導体薄膜を基板としてIII族窒化物半導体発光素子を作成する。

(もっと読む)

III族窒化物結晶の製造方法

【課題】結晶を厚く成長させても、転位密度が低いIII族窒化物結晶の製造方法を提供する。

【解決手段】本III族窒化物結晶の製造方法は、複数の第1種類と複数の第2種類のIII族窒化物結晶基板11,12を接触させて集合基板10を形成する工程を含み、集合基板10の結晶成長表面10sにおいて、第1種類の基板11は(0001)表面11pを有し、第2種類の基板12は(000−1)表面12qを有し、第1種類の基板11と第2種類の基板12の複数の接触面13が互いに平行な線として現われ、結晶成長表面10上において接触面13に繋がる位相境界23を含むIII族窒化物結晶20を成長させる工程をさらに含む。

(もっと読む)

3C−SiC単結晶膜の形成方法

【課題】Si単結晶基板上に、平坦かつ反位相領域の存在しない高品質な3C−SiC単結晶膜を簡便に形成する方法を提供する。

【解決手段】面方位(001)からのオフ角度が0.2°以上1°未満であり、オフ方向が<100>以外の方向であるSi単結晶基板上に、前記Si単結晶基板を100%水素ガス雰囲気中でアニール処理した後、3C−SiC単結晶をエピタキシャル成長させることにより、高品質な3C−SiC単結晶膜を得る。

(もっと読む)

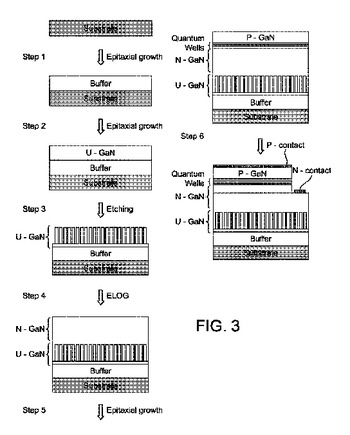

半導体デバイスの製造方法及び半導体デバイス

層状半導体デバイスの製造方法であって、(a)複数の半導体ナノ構造を含む基体を用意する工程と、(b)エピタキシャル成長法によって前記ナノ構造上に半導体材料を成長させる工程と、(c)エピタキシャル成長法によって前記半導体材料上に前記半導体デバイスの層を成長させる工程と、を含む方法。  (もっと読む)

(もっと読む)

高一様性のホウ素ドープト単結晶ダイヤモンド材料

本発明は、第1の表面を有するホウ素ドープト単結晶ダイヤモンドの基体層と、前記第1の表面の上のホウ素ドープト単結晶ダイヤモンドの導電性層とを有するダイヤモンド材料において、前記導電性層中のホウ素の分布が、前記基体層中のホウ素の分布に比べてより一様である、ダイヤモンド材料に関する。  (もっと読む)

(もっと読む)

ダイヤモンド基板およびその製造方法

【課題】半導体リソグラフィープロセスや大型光学部品、半導体材料、放熱基板等に好適な大型ダイヤモンド基板、及びその製造方法を提供する。

【解決手段】シリコン基板上に単結晶ダイヤモンド種基板1が配置されたダイヤモンド基板であって、シリコン基板に凹部が存在し、この凹部上に主面の面方位が(111)である単結晶ダイヤモンド種基板1が配置されており、シリコン基板の凹部以外の表面上に(100)配向もしくは(110)配向の気相合成ダイヤモンド層8が設けられており、単結晶ダイヤモンド種基板1とシリコン基板が(100)配向もしくは(110)配向の気相合成ダイヤモンド層8を介して接合され、ダイヤモンド層8と単結晶ダイヤモンド種基板1とが表面近傍で密着し、両者の表面が実質的に平坦化且つ一体化されているダイヤモンド基板。

(もっと読む)

基板の製造方法

【課題】III族窒化物半導体の結晶層の結晶性を向上できる基板の製造方法を提供する。

【解決手段】基板の製造方法は、下地基板10の上にクロム層20を成膜するクロム層成膜工程と、クロム層20を1000℃以上の温度で窒化してクロム窒化物膜30にする窒化工程とを備え、窒化工程では、下地基板10とクロム窒化物膜30との間に中間層が形成される。さらに、クロム窒化物膜30の上にIII族窒化物半導体の結晶層を成長させる結晶層成長工程を備える。

(もっと読む)

半導体基板及びその製造方法

【課題】GaNを結晶成長させる場合でも、転移密度が低い良質なエピタキシャル結晶成長が可能なβ―Ga2O3系単結晶からなる半導体基板、(100)面の上にGaNが成長して形成されたエピタキシャル層を有するβ―Ga2O3系単結晶からなる半導体基板、及び、これらのβ―Ga2O3系単結晶からなる半導体基板の製造方法を提供する。

【解決手段】所定の面方位である(100)面を有し、この(100)面の表面層の酸素が除去されたことを特徴とするβ―Ga2O3系単結晶からなる半導体基板とする。

(もっと読む)

結晶成長方法、結晶基板、および半導体デバイス

【課題】結晶性を良好に維持するとともに、成長させる結晶の面積を大きくする結晶成長方法、結晶基板、および半導体デバイスを提供する。

【解決手段】複数の種基板10を、種基板10の側部11側にずらして配置する配置工程と、ハイドライド気相成長法により、複数の種基板10の各々の表面12上にAlxInyGa(1-x-y)N(0≦x≦1、0≦y≦1、x+y≦1)結晶を成長させる成長工程とを備えている。そして、成長工程では、複数の種基板10の各々の表面12上に成長した結晶の各々が一体化するように成長させる。

(もっと読む)

有機金属化学気相成長法による、高品質のN面GaN、InNおよびAlNならびにそれらの合金のヘテロエピタキシャル成長の方法

MOCVDによって成長させられるN面GaN膜の平滑な高品質膜のヘテロエピタキシャル成長のための方法を開示する。誤配向基板の使用、およびおそらく基板を窒素化させるステップは、本明細書で開示されるような、平滑なN面GaNおよび他のIII族窒化物膜の成長を可能にする。本発明はまた、N面GaNをデバイス応用に対して容認不可能にする、典型的な大型(μmサイズの)六方晶特徴を回避する。本発明は、N面デバイスの開発を可能にする、平滑な高品質膜の成長を可能にする。  (もっと読む)

(もっと読む)

製造装置、結晶製造方法、基板製造方法、窒化ガリウム結晶及び窒化ガリウム基板

【課題】均質で高品質な塊状のIII族窒化物結晶を安価に製造する。

【解決手段】製造装置1000は、結晶作製装置100と結晶成長装置500を備えている。結晶作製装置100は、金属Naと金属Gaとを含む混合融液に窒素ガスを供給して第1のGaN結晶を作製する。この第1のGaN結晶は、転位密度が小さく(≦105cm−2)高品質である。第1のGaN結晶は、スライス及び研磨され、GaNウエハが作製される。結晶成長装置500は、作製されたGaNウエハを基板として、HVPE法によって基板上に第2のGaN結晶を結晶成長させ、塊状のGaN結晶を製造する。

(もっと読む)

サファイア単結晶基板およびIII族窒化物系化合物半導体

【課題】その面上に積層させて得られるIII族窒化物系化合物半導体の結晶性が向上するサファイア単結晶基板と、この基板を用いて得られるIII族窒化物系化合物半導体を提供すること。

【解決手段】上記サファイア単結晶基板はサファイア結晶の(006)面におけるX線ロッキングカーブの半値幅が20arcsec以下であることを特徴とする。また、AlN、GaN等一般式AlxGayIn1−x−yN(0≦x≦1, 0≦y≦1, 0≦x+y≦1)で表されかつLEDの発光素子等として用いられるIII族窒化物系化合物半導体は、サファイア結晶の(006)面におけるX線ロッキングカーブの半値幅が20arcsec以下であるところの面指数のばらつきや格子面間隔のばらつき等が小さいサファイア単結晶基板上に積層させて得られることを特徴とする。

(もっと読む)

炭化珪素単結晶エピタキシャルウェハ及びその製造方法

【課題】特性の優れた半導体素子を製造するための高品質炭化珪素単結晶エピタキシャルウェハ及びその製造方法を提供する。

【解決手段】炭化珪素単結晶基板上にエピタキシャル薄膜を有する炭化珪素単結晶エピタキシャルウェハであって、エピタキシャル薄膜が炭化珪素単結晶基板上に形成された第1のエピタキシャル薄膜とこの第1のエピタキシャル薄膜内に形成された第2のエピタキシャル薄膜とを有する炭化珪素単結晶エピタキシャルウェハ及びその製造方法。

(もっと読む)

エピタキシャルシリコンウェーハおよびその製造方法

【課題】{110}ウェーハにおいて、100nm以下のLPD測定可能とし、表面ラフネスの劣化を防止し、表面状態を判断可能とし、ウェーハの品質評価を可能とする。

【解決手段】シリコン単結晶の{110}面を傾けた面を主面とするシリコンウェーハにエピタキシャル層を成長させたエピタキシャルシリコンウェーハであって、

エピタキシャル層を成長させるシリコンウェーハは、前記{110}面を傾ける傾角度方位が、該{110}面に対して平行な<100>方位から<110>方向に対して0〜45°の範囲に設定されてなる。

(もっと読む)

半導体基板の製造方法

【課題】III族窒化物半導体の結晶層の結晶性を向上できる半導体基板の製造方法を提供する。

【解決手段】本発明の第1側面に係る半導体基板の製造方法は、下地基板の上にクロム層を50℃以上の温度で成膜するクロム層成膜工程と、前記クロム層を窒化してクロム窒化物膜にする窒化工程とを備えたことを特徴とする。

(もっと読む)

エピタキシャルシリコンウェーハおよびその製造方法

【課題】{110}ウェーハにおいて、100nm以下のLPD測定可能とし、表面ラフネスの劣化を防止し、表面状態を判断可能とし、ウェーハの品質評価を可能とする。

【解決手段】シリコン単結晶の{110}面を傾けた面を主面とするシリコンウェーハにエピタキシャル層を成長させたエピタキシャルシリコンウェーハであって、

エピタキシャル層を成長させるシリコンウェーハは、前記{110}面を傾ける傾角度方位が、該{110}面に対して平行な<100>方位から<110>方向に対して0〜45°の範囲に設定されてなる。

(もっと読む)

III族窒化物半導体の製造装置及び製造方法

【課題】従来のHVPE装置の欠点を解決したIII族窒化物半導体の製造装置及び製造方法を提供する。

【解決手段】成長炉3内に原料となるIII族ガスg3とV族ガスg5を供給し、これらガスg3,g5で基板2上にIII族窒化物半導体結晶Cを成長させるIII族窒化物半導体の製造装置1において、成長炉3は、隔壁4で相互に分離されたIII族ガスg3が供給されるA室5aと、V族ガスg5が供給されるB室5bとの少なくとも2室を備え、A室5aおよびB室5bの両ガス出口7,9を隣接させ、これら両ガス出口7,9近傍に基板2を配置したものである。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

【課題】平坦度の向上と、LPD の検出サイズの縮小化を図ることができるエピタキシャルウェーハの製造方法等を提供する。

【解決手段】エピタキシャルウェーハの製造方法であって、シリコン単結晶ウェーハの主表面上にシリコンをエピタキシャル成長させる工程と、前記エピタキシャル成長工程と、前記ウェーハの主表面を特定の処理液で100℃以下の温度で処理し、前記ウェーハの主表面上に付着したパーティクルを除去しつつ、所定膜厚の酸化膜を形成するウェーハ平坦化前処理工程と、前記主表面を鏡面研磨する表面研磨工程とを具えるエピタキシャルウェーハの製造方法である。

(もっと読む)

161 - 180 / 253

[ Back to top ]