Fターム[4M104AA05]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000) | GaAs (523)

Fターム[4M104AA05]に分類される特許

141 - 160 / 523

電界効果型トランジスタ及びその製造方法

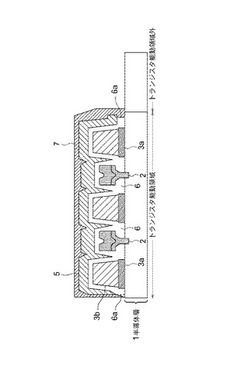

【課題】ゲート容量の増大を抑制しつつ、耐湿性を大幅に向上させることを可能にした電界効果型トランジスタおよびその製造方法を得る。

【解決手段】半導体層1上にT型ゲート電極2が形成された電界効果型トランジスタであって、T型ゲート電極2が形成されている領域をトランジスタ能動領域としたとき、当該トランジスタ能動領域全体において、T型ゲート電極2上に設けられた、耐湿性・耐エッチング性の高い絶縁膜若しくは有機膜を含む第1の高耐湿性保護膜5を備え、T型ゲート電極2の傘下を含むT型ゲート電極2の近傍において、半導体層1と第1の高耐湿性保護膜5との間に空隙6が形成されており、空隙6が外界に接している端面6aを第2の高耐湿性保護膜7により塞いだ構成となっている。

(もっと読む)

半導体装置

【課題】ガードリングを越えて半導体チップ内に水分が浸入した場合でも、半導体チップ上の1つの電極と他の1つの電極との短絡を抑制すること。

【解決手段】半導体チップ10と、半導体チップ10上に配置された電極パッド14、16と半導体チップ10の外周との間に配置された導電性のガードリング18と、ガードリング18の一部領域を排することで、ガードリング18を互いに絶縁された複数の単位領域に分割するための、複数のガードリング絶縁部60と、を有する半導体装置。

(もっと読む)

化合物半導体装置、および化合物半導体装置の製造方法

【課題】ソース電極およびドレイン電極の表面モフォロジーおよび延性を向上させて耐圧を向上させ、オン抵抗の増加を抑制した化合物半導体装置、その製造方法を提供する。

【解決手段】化合物半導体装置1は、ソース領域21およびドレイン領域25が形成される化合物半導体層10(第2化合物半導体層12)と、ソース領域21およびドレイン領域25にそれぞれ対応して形成されたソース電極22およびドレイン電極26とを備える。ソース領域21およびドレイン領域25は、化合物半導体層10に対してオーミック性を有する領域形成用オーミック金属によって形成され、ソース電極22およびドレイン電極26は、領域形成用オーミック金属20r、24rを除去した領域へ新たに形成されソース領域21およびドレイン領域25に対してオーミック性を有する電極形成用オーミック金属22m、26mによって形成されている。

(もっと読む)

半導体装置、およびその作製方法

【課題】アクティブマトリクス型表示装置等の半導体装置において、トランジスタの駆動能力を低下させることなく寄生容量の容量値を低減することを課題の一とする。または、寄生容量の容量値を低減した半導体装置を低コストに提供することを課題の一とする。

【解決手段】トランジスタのゲート電極と同一の材料層で形成される配線と、ソース電極またはドレイン電極と同一の材料層で形成される配線との間に、ゲート絶縁層以外の絶縁層を設ける。

(もっと読む)

導電性薄膜の形成方法

【課題】 簡単かつ短時間に基材面に金属ナノ粒子からなる安定した導電性薄膜を形成できる導電性薄膜の形成方法を提供する。

【解決手段】 金属ナノ粒子含有インクを基板上に塗布して薄膜を形成する工程と、当該薄膜に還元剤を作用させて還元処理を施す工程とを含むことを特徴とする導電性薄膜の形成方法。前記金属ナノ粒子含有インクは、炭素数10〜20の直鎖または分岐したアルキル基を有する保護剤で被覆された金属ナノ粒子を非水分散媒中に分散させたものを含有するのが好ましい。また、前記還元剤は、濃度0.005〜0.5mol/lの水溶液の状態で用い、還元処理は40〜70℃の温度条件下に行なうのが好ましい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

メモリデバイス及びメモリデバイスの形成方法

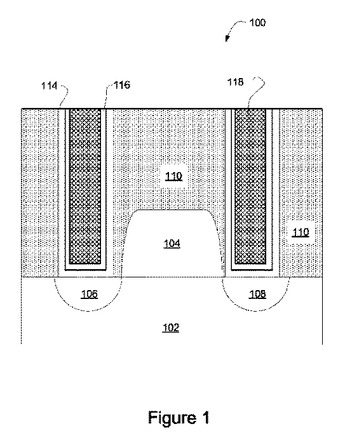

【課題】プログラマブルMOSFET(105)とロジックMOSFET(110)とを含むメモリデバイスを同一チップ上に形成する。

【解決手段】半導体基板を被う層状ゲート積層体の成形から始まり、層状ゲート積層体の高kゲート電極層上で停止するよう金属ゲート電極層にパターンを形成して、半導体基板上に第1、第2ゲート金属ゲート電極(16、21)を形成するメモリデバイスの製法が提供される。次のプロセスで、高kゲート誘電体層の一部を被う少なくとも1つのスペーサ(55)を第1ゲート電極(16)に形成する。高kゲート誘電体層の露出された残存部分をエッチングし、第1金属ゲート電極のサイドウォールを越えて延びる部分を有する第1高kゲート誘電体(17)及び第2金属ゲート電極(21)のサイドウォールに整合されたエッジを有する第2高kゲート誘電体(22)を形成する。

(もっと読む)

ゲート・スタック、ゲート・スペーサ及びコンタクト・ビアを用いる垂直型金属−絶縁体−金属(MIM)キャパシタ

【課題】 向上した製造可能性を有する金属−絶縁体−金属キャパシタ、及びその製造方法を提供する。

【解決手段】 垂直型金属−絶縁体−金属キャパシタを含む半導体構造体、及び垂直型金属−絶縁体−金属キャパシタを含む半導体構造体の製造方法がそれぞれ、半導体基板の上に配置された分離領域の上に配置され形成されたダミー金属酸化物半導体電界効果トランジスタからの構造コンポーネントを用いる。ダミー金属酸化物電界効果トランジスタは、分離領域を含む半導体基板の上に配置された金属酸化物半導体電界効果トランジスタと同時に形成することができる。金属−絶縁体−金属キャパシタは、キャパシタ・プレートとしてゲートを用い、ゲート誘電体として均一な厚さのゲート・スペーサを用い、別のキャパシタ・プレートとしてコンタクト・ビアを用いる。容量の増大のために、均一な厚さのゲート・スペーサは、導体層を含むことができる。容量の増大のために、単一のコンタクト・ビアを用いる鏡像となる金属−絶縁体−金属キャパシタ構造体を用いることもできる。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

電界効果半導体装置の製造方法

【課題】オン抵抗及びゲートリーク電流の小さいノーマリオフ型の電界効果半導体装置及びその製造方法を提供すること。

【解決手段】電流通路を形成するための少なくとも1つの半導体層を有している主半導体領域と、前記主半導体領域の一方の主面上に配置された第1の主電極6と、前記主半導体領域の一方の主面上に前記第1の主電極6から離間して配置された第2の主電極7と、前記主半導体領域の一方の主面上における前記第1の主電極と前記第2の主電極との間に配置されたゲート電極8と、前記主半導体領域と前記ゲート電極8との間に配置された金属酸化物半導体膜10とを備えている電界効果半導体装置の製造方法であって、前記金属酸化物半導体膜10を構成する金属材料を含有する薄膜を、前記主半導体領域上に蒸着させることを特徴とする電界効果半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】 エッチング処理を行わなくても、基底面内転位を有する半導体層から結晶成長された半導体層に基底面内転位が伝播することを防止することができる技術を提供する。

【解決手段】 本発明の方法は、半導体層2の表面2aにおける基底面内転位6の位置8を特定する特定工程と、特定工程で特定された位置8において結晶の再配列を行う結晶再配列工程と、結晶再配列工程の後に表面2aから半導体層を結晶成長させる結晶成長工程とを備えている。本発明によると、結晶成長された半導体層に基底面内転位6が伝播しない。基底面内転位6が結晶成長された半導体層に伝播していないために、リーク電流を抑えることができる。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

電界効果半導体装置及びその製造方法

【課題】ノーマリオフのHEMTを得ることが困難であった。

【解決手段】本発明に従うヘテロ接合型電界効果半導体装置は、電子走行層31と、第1及び第2の電子供給層32,33と、キャップ層34と、ソース電極8と、ドレイン電極9と、ゲート電極10と、シリコン酸化物から成る絶縁膜11と、p型金属酸化物半導体膜12とを有している。第2の電子供給層33に凹部7が形成され、この凹部7に絶縁膜11とp型金属酸化物半導体膜12とゲート電極10との積層体が配置されている。正孔濃度の高いp型金属酸化物半導体膜12はノーマリオフ特性に寄与し且つゲートリーク電流の低減に寄与する。絶縁膜11はゲートリーク電流の低減に寄与する。

(もっと読む)

電界効果型トランジスタを有する半導体装置

【課題】良好な絶縁性を確保しつつ極めて高い誘電率を有するゲート絶縁膜の機能と、空乏層が形成されることのない金属性のゲート電極の機能とを備え、ゲート電圧のチャネル領域への静電的支配力を可及的に大きくすることのできる半導体装置を提供することを可能にする。

【解決手段】第1導電型の第1半導体層12に離間して設けられた第2導電型の第1ソース領域12aおよび第1ドレイン領域12bと、第1ソース領域と第1ドレイン領域との間の第1半導体層に設けられる第1チャネル領域12cと、第1チャネル領域上に設けられたハーフメタル強磁性金属の第1ゲート電極60と、第1ソース領域に接続するように設けられたハーフメタル強磁性金属の第1ソース電極50aと、を備え、第1ゲート電極の磁化64cの向きが、第1ソース電極の磁化64aの向きと略反平行である。

(もっと読む)

電界効果トランジスタ

【課題】低いゲートリーク電流と低オン抵抗との同時に実現する。

【解決手段】InGaAsを主要な材料とするチャネル層と、AlGaAsを主要な材料とするショットキー層と、InGaPを主要な材料とするストッパ層と、ショットキー層の表面を露出するリセスを挟んで配置された第1領域と第2領域とを含むキャップ層と、キャップ層の上に設けられたソース/ドレイン電極と、リセスによって露出されたショットキー層の表面に設けられたゲート電極とを具備する電界効果トランジスタを構成する。ここで、キャップ層は、Si不純物を含む第1SiドープGaAsキャップ層と、第1SiドープGaAsキャップ層よりも低濃度のSi不純物を含む第2SiドープGaAsキャップ層と、第2SiドープGaAsキャップ層とストッパ層との間の層に設けられ、ポテンシャルバリアの上昇を抑制するバリア上昇抑制領域を備えるものとする。

(もっと読む)

半導体装置及びその製造方法

【課題】工数を増加させることなく、一方の導電型のトランジスタのみにキャップ膜の効果を与えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11に形成された第1のトランジスタ15と、第2のトランジスタ16とを備えている。第1のトランジスタ15は、第1のゲート絶縁膜22Aと、第1のゲート絶縁膜22Aの上に形成された第1のゲート電極27とを有している。第2のトランジスタ16は、第2のゲート絶縁膜22と、第2のゲート絶縁膜22の上に形成された第2のゲート電極28とを有し、第1のゲート絶縁膜22Aは、第1の元素が拡散した第1の絶縁材料を含み、第2のゲート絶縁膜22は、第1の絶縁材料を含む。

(もっと読む)

相補型半導体装置とその製造方法

【課題】 マルチゲートMISFETからなる高移動度のnFET及びpFETの双方の移動度を向上させる相補型半導体装置とその製造方法を提供する。

【解決手段】

基板10上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された相補型半導体装置であって、nチャネルMISトランジスタ及びpチャネルMISトランジスタが、基板10の主面に平行な面内に引っ張り歪みを有する第一の半導体層と圧縮歪みを有する第二の半導体層とが交互に積層され、基板10の主面に対して突出した積層構造と、積層構造の対向する両側面を覆うように形成されたゲート絶縁膜80と、ゲート絶縁膜80を介して前記積層構造を覆って形成されたゲート電極30と、ゲート絶縁膜80とゲート電極30をはさんで対向し、積層構造の両端に形成されたソース/ドレイン領域20と、を有することを特徴とする相補型半導体装置。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

成膜方法

【課題】例えば主として粉体の成膜材料を用いることによって成膜材料を選択的に加熱することができ、もって迅速に且つ効率的に成膜処理を行うことが可能な成膜方法を提供する。

【解決手段】被処理体Wの表面に薄膜を形成する成膜方法において、被処理体の表面に成膜材料を付着させて成膜材料層70を形成する付着工程と、成膜材料層の形成された被処理体に電磁波74を照射して成膜材料層を加熱することによって薄膜72Aを形成する照射工程とを有する。これにより、例えば主として粉体の成膜材料を用いることによって成膜材料を選択的に加熱し、迅速に且つ効率的に成膜処理を行う。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

141 - 160 / 523

[ Back to top ]