Fターム[4M104AA05]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000) | GaAs (523)

Fターム[4M104AA05]に分類される特許

101 - 120 / 523

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

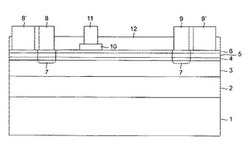

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

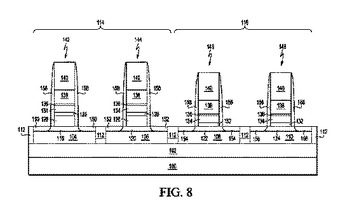

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体基板の製造方法およびレーザアニール装置

【課題】一面側に金属電極が形成された半導体基板のアロイ化を良好に行うことを可能にする製造方法および装置を提供する。

【解決手段】一面側に金属電極が形成され、所望により他面側に金属薄膜や化合物半導体層が形成された半導体基板に対し、パルス発振レーザを出射するパルス発振レーザ光源または連続発振レーザを出射する連続発振レーザ光源から出力された波長500〜550nmかつ半値幅300ns以上としたパルス発振レーザまたは波長500〜550nmで同一箇所に半値幅300ns以上で照射される連続発振レーザを金属電極側から半導体基板に照射しつつ相対的に走査して前記基板に対するアロイ処理を行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

半導体装置

【課題】ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11上にGaN層12およびAlGaN層13がこの順で形成され、AlGaN層13上にドレイン電極14、ソース電極15およびゲート電極16が形成された半導体装置であって、ゲート電極16の下方には、SiC基板11を貫通するように第1の開口23が形成されている。さらに、GaN層12上に形成され、ソース電極15に接続されるソースパッド19の一部が、SiC基板11の裏面側から露出するように、第2の開口24が形成されている。そして、第1の開口23内にソースフィールドプレート電極25−1を形成すると同時に、第2の開口24から露出するソースパッド19に接触するようにSiC基板11の裏面に接地導体25−2を形成する。

(もっと読む)

金属ゲートトランジスタ、集積回路、システム、およびその製造方法

【課題】金属ゲートトランジスタ、集積回路、システム、およびその製造方法を提供する。

【解決手段】半導体デバイスであって、第1MOS構造は、基板上に配置された第1ゲート誘電体、前記第1ゲート誘電体上に配置された第1仕事関数金属層、および前記第1仕事関数金属層上に配置された第1ケイ化物を含み、且つ第2MOS構造は、前記基板上に配置された第2ゲート誘電体、前記第2ゲート誘電体上に配置された第2仕事関数金属層、および前記第2仕事関数金属層上に配置された第2ケイ化物を含む半導体デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ウエハが反るのを防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、互いに対向する第1及び第2の主面を有するGaAs基板と、前記GaAs基板の前記第1の主面上に形成され、Pd、Ta、Moの少なくとも1つから構成された第1の金属層と、前記第1の金属層上に形成され、Ni系合金又はNiから構成された第2の金属層と、を備えることを特徴とする。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

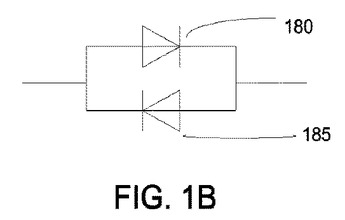

ショットキーダイオードスイッチおよびそれを含むメモリユニット

スイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接触部であり、上記第2の接合部と上記第3の接合部はオーミック接触部である。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】特性の良い半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】基板上に、ゲート電極として機能する第1の導電層を形成する工程と、第1の導電層を覆うように第1の絶縁層を形成する工程と、第1の導電層と一部が重畳するように、第1の絶縁層上に半導体層を形成する工程と、半導体層と電気的に接続されるように第2の導電層を形成する工程と、半導体層および第2の導電層を覆う第2の絶縁層を形成する工程と、第2の導電層と電気的に接続される第3の導電層を形成する工程と、半導体層を形成する工程の後、第2の絶縁層を形成する工程の前の第1の熱処理工程と、第2の絶縁層を形成する工程の後の第2の熱処理工程と、を有する。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体デバイスの製造方法

【課題】薄型化されたウェハにめっき処理をする際にウェハ裏面への金属析出やウェハの反り及び損傷を抑制すると共に、ウェハのめっき処理効率が良好な半導体デバイスの製造方法を提供する。

【解決手段】ウェハを薄型化する工程1、薄型化された前記ウェハの裏面をダイシングテープでリングフレーム内にマウントする工程2、及び、前記リングフレーム内にマウントされた前記ウェハの表面にめっき処理を行う工程3を備えた半導体デバイスの製造方法。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

101 - 120 / 523

[ Back to top ]