Fターム[4M104AA05]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000) | GaAs (523)

Fターム[4M104AA05]に分類される特許

161 - 180 / 523

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

半導体レーザ素子およびその製造方法

【課題】電気的特性が劣化するのを抑制することが可能な半導体レーザ素子を提供する。

【解決手段】この半導体レーザ素子100は、支持基板1と、支持基板1上に形成されたp側オーミック電極15と、p側オーミック電極15上に形成され、活性層12を含む半導体層10aとを備え、p側オーミック電極15は、Agを主成分とし、約0.6質量%のPdと、約0.9質量%のCuとを含有するAg合金材料からなるAg合金層15bを含む。

(もっと読む)

双方向スイッチ

【課題】1つの単位セルに含まれる第1のゲート電極と第2のゲート電極との間の配線抵抗の差が小さく、スイッチングロスを低減した双方向スイッチを実現できるようにする。

【解決手段】双方向スイッチは、第1のオーミック電極15、第1のゲート電極17、第2のゲート電極18及び第2のオーミック電極16を有する複数の単位セル11を備えている。第1のゲート電極15は、第1の引き出し配線31を介して第1のゲート電極パッド43と電気的に接続されている。第2のゲート電極18は、第2の引き出し配線32を介して第2のゲート電極パッド44と電気的に接続されている。第1のゲート電極パッド43との間の配線距離が最も短い第1のゲート電極17を有する単位セル11は、第2のゲート電極パッド44との間の配線距離が最も短い第2のゲート電極18を有する。

(もっと読む)

化合物半導体電界効果トランジスタ及びその製造方法

【課題】化合物半導体電界効果トランジスタの高集積化及び高電力化を図る。

【解決手段】角柱状又は角錐台状の、オン状態のときに軸方向に電流が流れる半導体部43と、半導体部の周囲に、第1絶縁層50、制御電極層60及び第2絶縁層72が、半導体部の軸方向に沿って順に積層された周辺部とを備える。半導体部が、角柱状又は角錐台状の電子走行部44と、電子走行部の側面44c上に形成された電子供給部46とを備えて構成される。

(もっと読む)

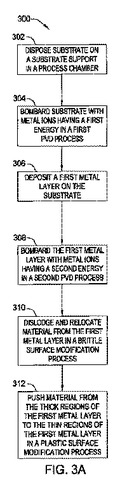

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置、パターン形成方法および半導体装置の製造方法

【課題】開口部の間口部分の拡大を抑制しつつ、開口部内に埋め込み導体を埋め込みやすくする。

【解決手段】半導体ウェハW1の中心から左側に離れたチップ領域C1a、C1bでは、開口部13a、13b内の左右の壁面のうち右側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心から右側に離れたチップ領域C1d、C1eでは、開口部13d、13e内の左右の壁面のうち左側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心の近傍のチップ領域C1cでは、開口部13c内の左右の壁面には傾斜面を設けないようにする。

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板を使用したSOI基板上に形成しても、ゲート電極を形成する導電膜を成膜する際に該導電膜の加える応力により、ガラス基板上の絶縁膜及び半導体膜がはがれないような半導体装置の作製方法の提供を課題の一つとする。

【解決手段】ボンド基板上に第1の絶縁膜を形成し、ボンド基板の表面からイオンを添加することによって脆化層を形成し、ボンド基板を、第1の絶縁膜を介してガラス基板と貼り合わせ、ボンド基板を脆化層において分離してガラス基板上に第1の絶縁膜を介して半導体膜を形成し、第1の絶縁膜及び半導体膜の周辺領域を除去してガラス基板の一部を露出させ、半導体膜、第1の絶縁膜及びガラス基板上に接してゲート絶縁膜を形成し、ゲート絶縁膜上に接して2層構造の積層導電膜を形成し、2層構造の積層導電膜として、上層に引っ張り応力を有する導電膜、下層に圧縮応力を有する導電膜を用いて半導体装置を作製する。

(もっと読む)

ガス導入機構及び成膜装置

【課題】ガスの切り替えの応答性を向上させることが可能なガス導入機構及びこれを用いた成膜装置を提供する。

【解決手段】被処理体Wに対して成膜処理を施す成膜装置22の処理容器24内へ必要な複数種類のガスを導入するためのガス導入機構62において、処理容器24に取り付けられるガス導入機構本体64と、ガス導入機構本体64に設けられて、複数種類の各ガスを供給するガス通路に接続された複数のガス室66A〜66Cと、各ガス室66A〜66Cと処理容器24内とを連通するようにそれぞれ設けられたガス噴出口68A〜68Cと、各ガス室66A〜66C内に設けられてガス噴出口68A〜68Cを開閉する可動蓋70A〜70Cと、可動蓋70A〜70Cを駆動する蓋駆動部72A〜72Cと、蓋駆動部72A〜72Cを制御する可動蓋制御部74とを備える。これにより、ガスの切り替えの応答性を向上させる。

(もっと読む)

半導体装置の製造方法

【課題】加工精度を改善し、かつ厚い配線を得るための半導体装置の製造方法を提供することを課題とする。

【解決手段】絶縁性基板上に形成された導電性膜上に配線形成領域を覆う第1のフォトレジストパターンを形成する工程と、前記第1のフォトレジストパターンをマスクとする異方性エッチングにより前記導電性膜の上部を除去することで第1溝を形成する工程と、前記第1のフォトレジストパターンを除去した後、前記第1溝の底部の少なくとも一部が露出した開口を有する第2のフォトレジストパターンを形成する工程と、前記第2のフォトレジストパターンをマスクとする異方性エッチングにより前記第1溝の底部に露出する前記導電性膜の下部を少なくとも除去することで第2溝を形成する工程を備えることで、前記第1溝と第2溝に由来する配線分離溝と、前記配線分離溝により分離された配線とを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

光電変換素子および光検出素子

【課題】 長波長領域の光の透過性に優れ、これを効率よく活用できる光電変換素子および光検出素子を提供する。

【解決手段】 第一の電極層、光電変換層および第二の電極層が順に配置され、前記第二の電極層側から入射する光によって光起電力を発生させる光電変換素子においては少なくとも前記第二の電極層が、もしくは、一対の電極と該電極間に挟まれた光検知材料層とを有する光検出素子においては一対の電極のうち少なくとも一方が、(A)チタン化合物に過酸化水素を反応させた反応生成物と(B)ニオブ化合物またはタンタル化合物に過酸化水素を反応させた反応生成物とを含む前駆体液を塗布し、焼成した後、還元雰囲気下にて加熱によるアニール処理を施すことにより形成された酸化チタン系透明導電性膜である。

(もっと読む)

ガードリング構造およびその製造方法

半導体素子用のガードリング構造。ガードリング構造は、第1層および第1層の上面に第2層を有する半導体積層体と、第1層内に形成されたゲート構造と、第1層内に形成されたガードリングとを有する。第2層は、第1層のドーパント濃度よりも高いドーパント濃度を有する。ゲートおよびガードリングは、単一のマスクを用いて同時に形成される。  (もっと読む)

(もっと読む)

バックグラウンドめっきの抑制

【課題】半導体上のバックグラウンドめっきを抑制する方法を提供する。

【解決手段】方法は、高い光透過性を有する相変換レジストを誘電体上に選択的に堆積させてパターンを形成すること、そのレジストで覆われていない誘電体の部分をエッチング除去すること、並びにその誘電体のエッチングされた部分上に金属シード層を堆積させることを含む。次いで、光誘導めっきによって、その金属シード層上に金属層が堆積させられる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体ウエハ面内におけるゲート形成領域の開口部のエッチング深さを均一化して所望の閾値電圧を得ることができ、併せて歩留を向上した半導体装置及びその製造方法を提供する。

【解決手段】本発明は、半絶縁性基板上に、バッファ層と、チャネル層と、p型不純物が拡散される拡散層と、前記拡散層よりもエッチングレートが大きい被エッチング層を順次エピタキシャル成長して積層するステップと、前記被エッチング層よりもエッチングレートが大きい絶縁層を前記被エッチング層上に設けるステップと、エッチングレートの違いを利用して、前記絶縁膜に開口部を設け、さらに、前記開口部を介して前記被エッチング層を選択的にエッチング除去するステップと、前記開口部から前記拡散層に前記p型不純物を拡散してゲート領域を形成するステップと、を有する。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

載置台構造、成膜装置及び成膜方法

【課題】可逆反応を生ずる原料ガスを用いて薄膜を形成する際に、被処理体の周辺部に向けて分解抑制ガスを供給して原料ガスの可逆反応による熱分解を抑制することにより、膜厚の面内均一性を高く維持しつつ、被処理体のベベル部及び裏面への薄膜の堆積を防止することが可能な載置台構造を提供する。

【解決手段】可逆反応を生ずる原料ガスを用いて処理容器4内にて被処理体Wに対して薄膜を形成するために被処理体を載置するための載置台構造29において、上面の載置面43に被処理体を載置するための載置台32と、載置された被処理体の周辺部に向けて原料ガスの可逆反応による熱分解を抑制する分解抑制ガスを供給するための分解抑制ガス供給手段70とを備える。これにより、被処理体の周辺部に向けて分解抑制ガスを供給して原料ガスの可逆反応による熱分解を抑制する。

(もっと読む)

半導体素子

【課題】無機半導体と有機物とを能動的な役割に用い、かつ有機物の劣化を防止することができる半導体素子を提供する。

【解決手段】ZnO系半導体1上に有機物電極2が形成されており、有機物電極2の上にはAu膜3が形成されている。ZnO系半導体1の裏面には有機物電極2に対向するように、Ti膜4とAu膜5の多層金属膜で構成された電極が形成されている。有機物電極2とZnO系半導体1との接合界面は、ショットキー障壁が形成されており、これらの間で整流作用が発生する。しかも、有機物電極2の表面には、撥水膜3が被覆されているため、水等から有機物電極2表面を防護することができ、有機物電極の劣化を防止することができる。

(もっと読む)

半導体素子およびその製造方法

【課題】本発明はトレンチの上部縁部位でゲート絶縁膜が薄くなる現象を防止し、均一な厚さを有するゲート絶縁膜を形成することができる半導体素子、およびその製造方法を提供する。

【解決手段】本発明の半導体素子は、活性領域を画定するトレンチが形成された基板と、該トレンチに埋め込まれた素子分離膜と、前記活性領域上にゲート絶縁膜の成長時に前記トレンチの上部縁部位での酸化を促進するために前記トレンチの上部縁部位に形成された酸化促進領域と、ゲート絶縁膜上に形成されたゲート導電膜と、を備える。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

ゲイン変化補償を伴うトランジスタ

半導体装置(10)およびこれを製造方法は、活性素子領域(12)および隔離領域(14)を提供する工程を含み、隔離領域は、活性素子領域との境界(32)を形成する。パターン化ゲート材料(16)は、境界の第1部分(34)と第2(36)部分との間において、活性素子領域と重なる。パターン化ゲート材料は、活性素子領域内において、チャネルを画定し、ゲート材料は、境界領域の第1部分および第2部分の付近において、境界の第1部分と第2部分との間よりも大きい(24+26,28+30)、ゲート材料の主要寸法に沿って中心線(18)と直交するゲート長さ寸法を有する。チャネルは、境界の第1部分に隣接する第1端と、境界の第2部分に隣接する第2端とを含み、更に、チャネルの両端においてテーパが付けられたゲート長さ寸法によって特徴付けられる。  (もっと読む)

(もっと読む)

161 - 180 / 523

[ Back to top ]