Fターム[4M104AA05]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000) | GaAs (523)

Fターム[4M104AA05]に分類される特許

201 - 220 / 523

半導体基板、半導体基板の製造方法および半導体装置

【課題】半導体−絶縁体界面の界面準位が低減した半導体基板とその製造方法および半導体装置を提供する。

【解決手段】砒素を含む3−5族化合物の半導体層と、酸化物、窒化物または酸窒化物の絶縁層と、を備え、前記半導体層と前記絶縁層との間に砒素の酸化物が検出されない半導体基板が提供される。当該第1の形態において半導体基板は、前記半導体層と前記絶縁層との間に存在する元素を対象としたX線光電子分光法による光電子強度の分光観察において、砒素に起因する元素ピークの高結合エネルギー側に、酸化された砒素に起因する酸化物ピークが検出されないものであってよい。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

電極構造および半導体装置

【課題】Ga原子及びAs原子の電極表面への拡散を低減可能なn型GaAs系半導体の電極構造及びこの電極構造を備える半導体装置を提供する。

【解決手段】本発明に係る電極構造は、Au及びGeを含む化合物から成り、n型GaAs半導体基板10上に設けられたオーミック金属層11と、オーミック金属層11上に設けられた第1のPt層13と、第1のPt層13上に設けられたTi層14とを備える。Ti層14は、Ga原子及びAs原子の電極表面への拡散を防止する。第1のPt層は、Ti層14のTi原子が、Au電極層12及びオーミック金属層11へ拡散することを防止する。その結果、Ti層14の拡散防止機能が維持される。これらにより、電極表面へのGa原子及びAs原子の拡散を低減することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の異なる半導体層上においても、良好にゲート電極を形成可能な半導体装置の製造方法を提供する。

【解決手段】絶縁体2上の膜厚の異なる半導体層3a,3bにそれぞれ形成された電界効果型トランジスタを有する半導体装置の製造方法である。まず、膜厚の異なる半導体層3a,3bを絶縁体上に形成する。そして、半導体層3a,3b上にゲート絶縁膜5a,5bを形成し、ゲート絶縁膜5a,5b上にゲート電極材料を積層する。パターニング時におけるフォトリソグラフィに影響を与えない膜厚を有する犠牲膜をゲート電極材料上に形成し、エッチングにより犠牲膜をパターニングするとともに、パターニングされた犠牲膜8aをマスクに用いてゲート電極材料をパターニングしてゲート電極11,12を形成する。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】異なる誘電体材料を含む、デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】第1領域Iと第2領域IIとを有する基板5を用意し、(i)第1領域Iと第2領域IIを覆うようにホスト誘電体層1を形成し、(ii)第1領域Iと第2領域IIの上のホスト誘電体層1を覆うように第1誘電体キャップ層2を形成した後、(iii)第1領域Iの上の下位層1に対して選択的に、第1誘電体キャップ層1を除去して、第1領域Iの上の下位層1を露出させ、(iv)第1領域Iの上の下位層1と、第2領域IIの上の第1誘電体キャップ層2とを覆うようにHfベースの誘電体キャップ層3を形成し、(v)第1領域Iと第2領域IIの上のHfベースの誘電体キャップ層3を覆うように制御電極4を形成する。

(もっと読む)

電子素子とその製造方法

【課題】ショットキー障壁を生じさせず,所望する電気伝導特性を有する電子素子及び電子素子の製造方法を提供することを課題とする。

【解決手段】本発明に係る電子素子では,離間されて配置された一対の電極102と,電極102間それぞれに接続され,半導体的性質を有する半導体ナノワイヤ101とを備え,電極102が,ナノワイヤ101と同一の材料又は同一の半導体的性質を有する材料からなることを特徴とする。

(もっと読む)

半導体装置

【課題】GaAsなどの閃亜鉛鉱構造と負のピエゾ電気定数e14を有する化合物半導体材料よりなる半導体基板や半導体層の良好な結晶性を維持した状態で、電極とのコンタクト抵抗を下げる。

【解決手段】半絶縁性のGaAsから構成され、主表面が(100)面とされた基板101の上に、圧縮性の内部応力を伴う絶縁体から構成されて[0−11]方向に延在するストライプ状の絶縁パターン111と、絶縁パターン111のとなりの、導電性領域102が形成されている領域の基板101の上に形成されたオーミック電極103とを備える。

(もっと読む)

検出素子

【課題】 テラヘルツ波等の高周波を検出するためのショットキー接合部において、熱電子放出電流特性(フェルミレベルピニングの影響)を抑制することができる検出素子を提供する。

【解決手段】 第一ショットキー接合を形成する第一金属部20と、第一金属部20に接続され、高周波を検出する外部接続部材2と、第一金属部20の周辺に形成される絶縁体3と、オーミック接合を形成する金属層4とを備える検出素子10であって、第二ショットキー接合を形成する第二金属部21と、第一金属部20と第二金属部21とを接続する抵抗値R3の抵抗部材27とを備え、第一ショットキー接合部は、交流抵抗値R1−AC、直流抵抗値R1−DCを有し、第二ショットキー接合部は、交流抵抗値R2−AC、直流抵抗値R2−DCを有し、抵抗値R3は、式(1)を満たすことを特徴とする。

R1−AC<<R3<<R2−DC・・・・・・(1)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明は半導体装置および半導体装置の製造方法に関し、半導体装置の洗浄工程において半導体装置の半導体層の腐食防止を可能とすることを目的とする。

【解決手段】本発明に係る半導体装置は、半導体層と、前記半導体層に接続した電極部と、前記電極部に接続した、前記半導体層および前記電極部の構成材料よりイオン化傾向の大きい金属からなる犠牲金属層と、を備える。本発明に係る半導体装置の製造方法は、半導体ウェハに、半導体層と前記半導体層に接続した電極部を有する半導体装置と、前記半導体層と電気的に接続した電気接触領域と、を形成する形成工程と、洗浄液の電位に対して負の電位を導き得る導電体を、前記電気接触領域に接続する接続工程と、前記半導体ウェハを前記洗浄液に浸漬した状態で、前記電気接触領域に前記負の電位を印加しながら、洗浄する洗浄工程と、を備える。

(もっと読む)

半導体装置

【課題】低閾値動作に可及的に適した実効仕事関数を有するMISトランジスタを備えた半導体装置を提供することを可能にする。

【解決手段】Hf(或いはZr)酸化物に高価数金属を添加することでギャップ内準位を作りだし、窒素あるいはフッ素などによりギャップ内準位の位置を変化させることで、最適な実効仕事関数を有する電極を備え、低閾値動作が可能なCMISデバイスを実現した。

(もっと読む)

半導体装置

【課題】通常のC−MOSFET回路との整合性、混載可能性を保ちつつ安定した動作で、不揮発な再構成可能論理回路を構築することが可能なスピンMOSFETを備えた半導体装置を提供することを可能にする。

【解決手段】半導体基板と、半導体基板に離間して形成された第1ソース領域12および第1ドレイン領域14と、第1ソース領域と第1ドレイン領域との間に設けられる第1チャネル領域と、第1チャネル領域上に形成された第1ゲート絶縁膜と、ゲート絶縁膜上に形成された第1ゲート電極18と、第1ソース領域上に形成され第1方向に磁化容易軸を有する強磁性層を含む第1ソース電極Ms1と、第1ドレイン領域上に形成され第1方向に対して0度より大きく180度未満の角度をなす第2方向に磁化した強磁性層を含む第1ドレイン電極Md1と、第1ドレイン領域上に第1ドレイン電極と離間して形成され第2方向と略反平行な方向に磁化した強磁性層を含む第2ドレイン電極Md2と、を備えている。

(もっと読む)

半導体装置とその製造方法

【課題】SGOI(110)基板上のp、n両領域で高移動度の半導体装置を実現する。

【解決手段】Si1-xGex(0.25≦x≦0.90)の(110)面を表面に有する半導体基板(1,2,3)と、(110)面上に形成されたn及びpチャネル型MISFETとを具備し、両MISFETは、[−110]方向が[001]方向より長い線状で、(311)若しくは(111)面のファセットを有する活性領域(5,6)を有し、活性領域の[−110]方向に、ソース領域・チャネル領域・ドレイン領域が形成され、nチャネル型MISFETのチャネル領域(5C)はSiで形成され、pチャネル型MISFETのチャネル領域(6C)はSi1-yGey(x<y≦1)で形成され、両MISFETのチャネル領域は、活性領域の[−110]方向に、一軸圧縮ひずみを有する。

(もっと読む)

デュアルゲート半導体装置の製造方法およびその構造

【課題】2つのゲート配線間の接続を容易に、かつ低抵抗で行えるデュアルゲート半導体装置を提供する。

【解決手段】半導体基板を準備する工程と、半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、第1および第2の電極の上部を層間絶縁層から露出させる工程と、第2の電極の第1ゲート金属膜を選択的に除去する工程と、第1および第2の電極を覆うように、層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する工程と、第2ゲート金属膜とゲート配線膜をパターニングして、第1ゲート電極と第2ゲート電極とを形成するとともに、第1ゲート電極と第2ゲート電極とをゲート配線膜で接続する工程とを含む。

(もっと読む)

ALD法又はCVD法による金属含有膜の調製

【課題】より高い結晶化温度を有する改良型誘電体層の構造及び該構造の製造方法には、誘電体層の等価酸化膜厚を減らすこと並びに界面特性の改良によってデバイス性能を改良する必要が今も残っている。

【解決手段】例えば金属ケイ酸塩又は金属酸窒化ケイ素の膜のような金属含有膜の化学気相成長又は原子層成長による堆積法が本書に開示されている。一実施形態における金属含有膜の堆積法は、金属アミド前駆体、ケイ素含有前駆体、及び酸素源を燃焼室に導入する工程(ただし、パージガスを導入した後に各前駆体を導入する)を含む。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタ等の半導体素子を介して上層と下層に形成された配線層間の良好な接続を可能にし、配線の自由度を向上させた半導体装置及びその作製方法を提供すること目的の一とする。

【解決手段】絶縁体でなる基板上の第1の絶縁層と、第1の絶縁層上に形成された第1の配線層と、第1の絶縁層上の第1の配線層が形成された領域以外の領域に形成された第2の絶縁層と、第1の配線層及び第2の絶縁層上に形成され、チャネル形成領域と不純物領域を有する単結晶半導体層と、単結晶半導体層のチャネル形成領域上にゲート絶縁層を介して形成されたゲート電極と、第1の配線層、第2の絶縁層、単結晶半導体層及びゲート電極を覆うように形成された第3の絶縁層と、第3の絶縁層上に形成された第2の配線層とを設け、第1の配線層と単結晶半導体層の不純物領域が接続し、第1の配線層と第2の配線層が電気的に接続する。

(もっと読む)

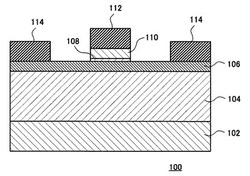

スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール

【課題】挿入損失を増大させることなくマルチゲートのゲート間の電位安定化が可能なスイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュールを提供すること。

【解決手段】電界効果型トランジスタを成すように、半導体基板上に形成された2個のオーミック電極39,40と、上記2個のオーミック電極の間に配置された少なくとも2個のゲート電極41,42と、隣り合うゲート電極の間に挟まれて配置された導電領域45とが備えられる。導電領域は、一端に、上記隣り合うゲート電極に挟まれている導電領域よりも幅が広い幅広部分を有し、隣り合うゲート電極の間の距離が幅広部分の幅よりも狭い。更に、幅広部分を介して2個のオーミック電極の間に直列に抵抗44,46が接続されている。

(もっと読む)

相互接続の製造方法

【課題】余分な工程を削減し二重ダマシン構造を形成できる製造工程を提供する。

【解決手段】二重ダマシン構造を製造する工程である。この工程は、スタックの上方に2

個のマスクが形成される絶縁体層とストップ層を含むスタックを形成するものである。マスクのうちの1個は、絶縁体層にビアあるいはコンタクト開口を形成するのに用いられ、第2のマスクは絶縁体層の相互接続のための凹部を形成するのに用いられる。より好ましくは、凹部はビアあるいはコンタクト開口に先行して形成される。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】絶縁破壊を抑制することができ、チップ面積の縮小化を実現することができる、窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この窒化物半導体素子は、n+型GaN基板1と、n-型GaN層2、p型GaN層3およびn+型GaN層4が順に積層されてなる窒化物半導体積層構造部5とを備えている。窒化物半導体積層構造部5には、トレンチ7が形成されている。トレンチ7の壁面8には、ゲート絶縁膜9を介してゲート電極10が形成されている。n+型GaN層4には、ソース電極15がオーミック接触している。また、n+型GaN基板1の他方表面には、ドレイン電極18がオーミック接触している。ゲート絶縁膜9のコンタクト開口16から露出するn-型GaN層2上には、ショットキー電極17が形成されている。ショットキー電極17は、n-型GaN層2に対してショットキー接触している。

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

半導体発光素子およびその製造方法

【課題】電流の制御が可能になり、電流密度が最適化でき、高輝度化が可能な半導体発光素子およびその製造方法を提供する。

【解決手段】半導体基板10と、半導体基板10の第1表面に配置された第1金属層21と、半導体基板の第2表面に配置された第2金属層22とを備える半導体基板構造と、半導体基板構造上に配置され、第3金属層20と、第3金属層20上に配置され,透明絶縁膜12と電流制御電極18からなる電流制御層(12,18)と、電流制御層(12,18)上に配置されるエピタキシャル成長層14とを備える発光ダイオード構造とから構成され、第1金属層21および第3金属層20を用いて、半導体基板構造と、発光ダイオード構造を貼り付けることを特徴とする半導体発光素子およびその製造方法。

(もっと読む)

201 - 220 / 523

[ Back to top ]