Fターム[4M104AA05]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | III−V族 (2,000) | GaAs (523)

Fターム[4M104AA05]に分類される特許

121 - 140 / 523

非対称型半導体デバイス及び製造方法

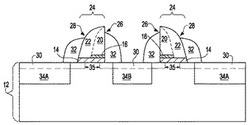

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

銀含有金属オーミック接触電極

【課題】既存の業界工程と互換でき、有効に、生産コストを低減できる銀含有金属オーミック接触電極を提供する。

【解決手段】ニッケル(Ni)層とゲルマニウム(Ge)層、銀(Ag)層、パラジウム(Pd)層或いはプラチナ(Pt)層及び厚い膜金属(Thick Metal)層からなり、順に、n形III-V族化合物半導体層上に堆積されてから、アニール(Anneal)処理を介して形成された構造で、上記銀層とゲルマニウム層との厚さ比例範囲が、Ag/Ge=7〜8の間にある。また、上記の低い電気抵抗率(Electric

Resistivity)と高い熱伝導率(Thermal Conductivity)のオーミック接触電極は、銀が材料として形成される。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】被処理体の表面に形成されている凹部の内径や幅が小さくても、薄膜の成膜時のステップカバレジを向上させることが可能な成膜方法を提供する。

【解決手段】真空排気が可能になされた処理容器22内へ凹部を有する絶縁層が表面に形成された被処理体Wを収容すると共に処理容器内へチタンを含む原料ガスと還元ガスとを供給してプラズマCVD法によりガスを反応させて被処理体に対してチタンを含む薄膜を形成する成膜方法において、反応が原料ガスの反応律速の反応状態となるように原料ガスと還元ガスの各流量を設定するように構成する。これにより、被処理体の表面に形成されている凹部の内径や幅が小さくなったり、凹部のアスペクト比が大きくなっても、薄膜の成膜時のステップカバレジを向上させることが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

集積型光発電素子及び集積型光発電素子の製造方法

【課題】集積型光発電素子の集電効率を高めること。

【解決手段】複数のセルが直列に接続された集積型光発電素子Iであって、基板10と、基板10上に形成され、隣接する他のセル側に突き出る形状を有する第1のパターニングにより分割された複数の裏面電極層11と、隣接する2個の裏面電極層11を跨ぐように裏面電極層11上に形成され、且つ分割溝15によって分割された複数の半導体層12と、分割された半導体層12上にそれぞれ形成された電極層(透明電極層)13と、少なくとも半導体層12の一部に裏面電極層11を分割する第1のパターニングに倣う形状の第2のパターニングにより形成され、隣接する他のセルから電流を集電する集電端部14と、を有することを特徴とする集積型光発電素子I。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

半導体レーザ用耐破損金属膜パターン

半導体レーザにおけるチップ破損の確率を低めるための金属膜パターンが提供される。明細書に開示される一実施形態にしたがえば、金属膜パターンのパッド辺がレーザ基板の複数の結晶面にかけて延びる。このようにすれば、いずれの与えられた応力集中点から始まるクラックも有意な大きさに達するには基板の多くの結晶面にわたって伝搬することが必要であろう。開示される別の実施形態は隣り合うコンタクトパッドの対のそれぞれの幾何学的形状及び方位に関する。さらに別の実施形態が開示され、特許請求される。  (もっと読む)

(もっと読む)

半導体素子およびその製造方法

【課題】 より高いレベルの、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、大電流を流すことができる半導体素子およびその製造方法を提供する。

【解決手段】 導電性GaN基板1と、半導体層2と、半導体層上に位置するショットー電極11と、バック電極12と、ショットキー電極に接続して半導体層上に延在する2次元電子ガス形成層と、2次元電子ガス形成層と、導電性GaN基板またはバック電極とを電気的に接続する導電部5とを備え、電流パス形成部は、ショットキー電極とバック電極間への電圧印加によって、横方向に2次元電子ガスを形成することを特徴とする。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】生産性に優れたフレキシブル半導体装置を提供する。

【解決手段】可撓性を有するフレキシブル半導体装置100であり、樹脂フィルム30と、樹脂フィルム30の上に形成された金属層10とを備え、金属層10は、絶縁壁51によって分断され、且つ、絶縁壁51の一端53は樹脂フィルム30に接しており、絶縁壁51によって金属層10から、ゲート電極10g、ソース電極10sおよびドレイン電極10dが形成されている。ゲート電極10gの上には、絶縁壁51に接するゲート絶縁膜22が形成されており、ゲート絶縁膜22の上には半導体層20が形成されている。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

リフトオフ方法及び薄膜トランジスタの製造方法

【課題】歩留まりの低下を防止して、製造工程の簡素化を図ることが可能になるとともに、製造コストの低減を図ることができる表示装置及びその製造方法を提供することを目的とする。

【解決手段】半導体ナノワイヤ3とリフトオフレジスト12と金属膜13とが形成された基板1を、気体のマイクロバブルが混合された液体により構成された剥離液に浸漬させることにより、リフトオフレジスト12とともにリフトオフレジスト12上の金属膜13を剥離して、基板2上に金属膜13からなる所定のパターンを形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電極の接触抵抗の低減を図るようにした高周波特性の良い電界効果トランジスタ及びその製造方法を提供すること。

【解決手段】III−V族化合物半導体薄膜をエピタキシャル結晶成長させてなる多層膜半導体構造を有しており、多層膜半導体構造は、基板1と、基板1上に形成されたバッファ層2と、バッファ層2上に形成された電子走行層3と、電子走行層3上に形成されたスペーサ層4と、スペーサ層4上に形成された電子供給層5と、電子供給層5上に形成されたバリア層6と、バリア層6上に形成された高電子濃度キャップ層7とを備え、さらに、高電子濃度キャップ層7上に形成されたソース電極101及びドレイン電極103と、バリア層6の表面に形成されたゲート電極102とを備えている。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体層の一方の面に基板が形成された半導体素子について、特性の劣化を避けながら容易に形成することを実現する。

【解決手段】半導体素子1は、半導体材料からなる半導体層5と、半導体層5の一方の面に接合された金属層18とを備え、金属層18は、磁性体層16を有し、磁性体層16は、少なくともFe及びNiを含む合金からなる層を有する。

(もっと読む)

High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体

【課題】High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体を提供する。

【解決手段】デバイスを形成する方法は、基板を用意するステップと、基板上に界面層を形成するステップと、界面層上にHigh−k誘電体層を堆積するステップと、High−k誘電体層上に酸素除去層を堆積するステップと、アニールを実施するステップとを含む。High−k金属ゲート・トランジスタは、基板と、基板上の界面層と、界面層上のHigh−k誘電体層と、High−k誘電体層上の酸素除去層とを含む。

(もっと読む)

ショットキーデバイス

本発明に係るデバイスは、半導体ナノワイヤ(1)と金属接触(5)との間の半導体金属接合によって形成されたショットキー障壁を備える。前記金属接触(5)は、その長さに沿って各ナノワイヤ(1)の周辺領域を少なくとも部分的に囲む。前記ナノワイヤ(2)は、前記半導体金属接合の一部である低濃度ドープ領域を備える。この低濃度ドープ領域は、ナノワイヤセグメント、ナノワイヤの全体又は高濃度ドープナノワイヤコア(3)を備えたコアシェル構造によって形成され、前記低濃度ドープ領域は、シェル(4)に含まれる。前記デバイスは、本発明に係る方法を用いて製造され、かかる方法は、2つの異なる成長モードを使用し、第1のステップは、前記半導体金属接合の形成用の適切なテンプレートを与えながら基板(2)から軸方向に成長させることを備え、第2のステップは、前記低濃度ドープ領域においてドーピングレベルを制御可能に放射状に成長させることを備える。 (もっと読む)

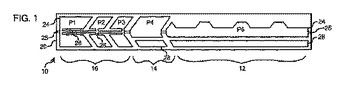

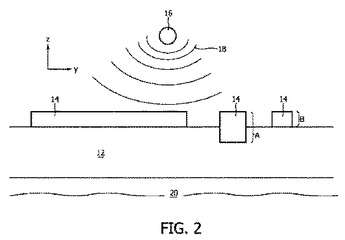

集積回路を製造する装置及び方法

本発明は、厚膜金属層14を有する集積回路10を製造する装置に関する。金属ペースト14の層は、熱伝導基板12上に適用手段24によって適用される。金属ペースト14は、予め決められたサイズの金属粒子を含む。RF生成器16は、金属ペースト14にRFエネルギー18を選択的に誘導結合させる。金属粒子を加熱するために、金属ペースト14の金属粒子の予め決められたサイズは、RFエネルギー18の結合周波数に対応する。このようにして、金属ペースト14の金属粒子は、従来のプロセスのパワーの何分の一かのパワーで、金属ペースト14を予備焼結する必要なく、加熱される。  (もっと読む)

(もっと読む)

メッシュ構造を有する電極を具備した太陽電池及びその製造方法

【課題】低抵抗と高透過性を併せ持ち、さらに太陽光を効率よくキャリアの励起に利用できる、安価な材料を用いた光入射面側電極を備えた太陽電池、及びその製造方法を提供する。

【解決手段】本発明の太陽電池は、光電変換層と、光入射面側電極層と、対向電極層とを具備し、前記光入射面側電極層が前記層を貫通する複数の開口部を有し、かつその膜厚が10nm以上200nm以下の範囲にあり、前記開口部の1つあたりの面積が80nm2以上0.8μm2以下の範囲にあり、開口部の開口率が10%以上66%以下の範囲にあり、光吸収層の少なくとも一部が、前記光入射面側電極層と前記光電変換層の接触面から1μm以内の距離に配置されていることを特徴とする。この電池の光入射面側電極層は、微粒子の単粒子層や、ブロックコポリマーの自己組織化によるドットパターンをマスクにエッチングしたり、スタンパーを利用して形成させることができる。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

121 - 140 / 523

[ Back to top ]