Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

221 - 240 / 2,474

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

金属薄膜電極及びその製造方法

【課題】本発明は、金属薄膜電極及びその製造方法に関する。

【解決手段】本発明の一実施例による金属薄膜電極の製造方法は、基材上に金属粉末、有機バインダ及び有機溶媒を含む金属ペーストを塗布して金属薄膜を形成する段階と、金属薄膜を有機酸と水系液の比が10:90〜90:10の雰囲気で還元焼成する段階と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

金属ナノペーストを用いた配線及び電極の形成方法

【課題】本発明は、金属ナノペーストを用いた配線及び電極の形成方法に関する。

【解決手段】本発明は、金属ナノペーストが印刷された基板を炉(furnace)に入れて窒素雰囲気下で220〜240℃に昇温させる段階と、炉の温度を前記範囲に維持しながらカルボン酸と空気の混合雰囲気下で前記基板を加熱する段階と、カルボン酸と空気の混合雰囲気下で炉の温度を100〜150℃に下降させる段階と、窒素雰囲気下で炉の温度を常温まで下降させる段階と、を含む焼結工程を含むことにより、低温焼結工程を経ても高温焼結工程を経た場合と同様に、金属膜の密度が高く、残留金属粒子量を最小化することができる金属配線及び電極の形成方法に関する。

(もっと読む)

ショットキーダイオードおよびその製造方法

【課題】 強誘電体層を有し、逆方向バイアス電圧印加時のリーク電流を低減させ、順方向バイアス電圧印加時の電圧降下を小さくすることができるショットキーダイオードを提供する。

【解決手段】 ショットキーダイオード1は、支持基板11を備え、さらに、支持基板11の表面上に形成された絶縁膜12と、絶縁膜12上に形成された密着層13と、密着層13上に形成されたショットキー金属層14と、ショットキー金属層14の表面上に、ショットキー金属層14とショットキー接触されるように形成され、Mnが添加された第一の誘電体層15と、第一の誘電体層15の表面上に形成され、Mnなどの添加物が添加されていない第二の誘電体層16と、第二の誘電体層16上に、第二の誘電体層16とオーミック接触するように形成されたオーミック金属層17を備えている。

(もっと読む)

薄膜トランジスタ

【課題】寄生容量を小さくでき、応答速度低下を抑制することが可能なTFTを提供する。

【解決手段】基材110上に配設した有機半導体層150と、有機半導体層150と接触し、対向してチャネル領域を形成するソース電極120及びドレイン電極130と、有機半導体層150と絶縁層160を介して設けられるゲート電極140と、ソース電極120と導電接続するソース電極配線部125と、ドレイン電極130と導電接続するドレイン電極配線部135と、ゲート電極140と導電接続するゲート電極配線部145と、からなるTFT100であって、積層方向からみて、有機半導体層150が、ゲート電極140を含み、ゲート電極140が、ソース電極120とドレイン電極130とチャネル領域とからなる領域を含み、有機半導体層150の周縁でソース電極配線部125とドレイン電極配線部135との間にはゲート電極配線部145が配される。

(もっと読む)

半導体装置

【課題】しきい値電圧の経時的な低下を抑制でき、またアルミ配線による絶縁膜の腐食やAlスパイクに起因するゲート・ソース間の短絡を防止できる半導体装置を提供する。

【解決手段】半導体装置のMOSFETセルは、ポリシリコンのゲート電極6およびn-ドリフト層2の上部に形成されたn+ソース領域4を備える。ゲート電極6上は層間絶縁膜7によって覆われており、Alのソース電極101は、層間絶縁膜7上に延在する。またゲート電極6にはAlのゲートパッド102が接続される。ソース電極101と層間絶縁膜7との間、並びにゲートパッド102とゲート電極6との間のそれぞれに、Alの拡散を抑制するバリアメタル層99が配設される。

(もっと読む)

エッチング剤及びこれを用いたエッチング方法

【課題】金属酸化物層と銅層とが共存する被処理物のエッチングに用いられ、前記銅層を選択的にエッチングできるエッチング剤と、これを用いたエッチング方法を提供する。

【解決手段】Zn、Sn、Al、In及びGaから選ばれる1種以上の金属の酸化物を含む金属酸化物層と銅層とが共存する被処理物のエッチングに用いられ、前記銅層を選択的にエッチングするエッチング剤において、第二銅イオン源を銅イオンとして0.1〜3.0重量%、炭素数が6以下の有機酸を0.1〜30.0重量%、並びに、環内に窒素原子を2つ以上有する複素環式化合物、及び炭素数が8以下のアミノ基含有化合物からなる群より選ばれる1種以上の窒素含有化合物を0.1〜30.0重量%含有する水溶液からなり、pHが5.0〜10.5であることを特徴とするエッチング剤とする。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

アクティブマトリックス基板、及び液晶装置

【課題】TFTの光リーク電流が低減され、かつ、従来よりも少ないフォトリソフォグラフィ工程で製造することが可能なアクティブマトリックス基板を提供する。

【解決手段】アクティブマトリックス基板201は、絶縁性基板1上に、基板1側から、ゲート電極2と、ゲート電極2を覆うゲート絶縁膜6と、互いに離間形成されたドレイン電極9及びソース電極11と、チャネル層を含む少なくとも1層の半導体膜21とが順次形成された薄膜トランジスタ101と、画素電極10とが複数対アレイ状に形成されたものである。ドレイン電極9及びソース電極11は、基板1側から透光性導電膜EM2と非透光性導電膜EM3とが順次積層された積層構造を有し、かつ、ドレイン電極9の透光性導電膜EM2及び/又は非透光性導電膜EM3が延設され、この延設部分により画素電極10が形成されたものである。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】メモリセルは、ダイオード層、可変抵抗層、及び電極層を備える。ダイオード層は、整流素子として機能する。可変抵抗層は、可変抵抗素子として機能する。電極層は、可変抵抗層とダイオード層との間に設けられ、可変抵抗層及びダイオード層に接するように形成されている。電極層は、窒化チタンにて構成された窒化チタン層を備える。ここで、窒化チタン層内の第1領域における窒素原子に対するチタン原子の割合を第1割合とし、窒化チタン層内であって且つ第1領域よりも可変抵抗層に近い第2領域における窒素原子に対するチタン原子の割合を第2割合とする。この場合、第2割合は第1割合よりも大きい。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

機能性膜の形成方法、積層構造体、多層配線基板、アクティブマトリクス基板及び画像表示装置、並びに図面製造装置、インクジェット装置、積層構造体製造装置

【課題】インクジェット法により微細なパターンでショートさせることなく機能性膜を形成することができる機能性膜の形成方法を提供する。

【解決手段】被印刷面上に、低表面エネルギー領域を隔てて隣接する高表面エネルギー領域231,241を有する表面において、高表面エネルギー領域231,241の形状及び機能液の着弾範囲に基づいて、高表面エネルギー領域231(241)に機能液を供給する際に該機能液が高表面エネルギー領域231(241)のみに触れるための滴下許容範囲231A(241A)を決定し、ついで滴下許容範囲231A(241A)内の任意の位置を高表面エネルギー領域231(241)に対する機能液の滴下位置231C(241C)として決定し、高表面エネルギー領域231(241)の滴下位置231C(241C)にインクジェット法を用いて選択的に機能液を供給して所定パターンの機能性膜を形成する。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

半導体エピタキシャル結晶基板及びその製造方法

【課題】高性能の窒化ガリウム系トランジスタを製造するための、誘電体膜付の半導体エ

ピタキシャル結晶基板を提供すること。

【解決手段】下地基板1上にエピタキシャル法によって、バッファ層2、チャネル層3、

及び電子供給層4から成る窒化ガリウム半導体結晶層を形成した後、エピタキシャル成長

炉内で連続してAlNを電子供給層4上に誘電体膜の前駆体として積層し、しかる後、積

層した前駆体に対して酸化処理を施すことによって誘電体膜5を形成する。

(もっと読む)

透明導電膜の形成方法

【課題】透明導電膜を低コストかつ高効率で作製することができ、基板の大面積化への対応も容易な透明導電膜の形成方法を提供する。

【解決手段】本発明の透明導電膜の形成方法は、酸化インジウム錫化合物からなるITO粒子を含有する導電性インク(Ink)を、その表面に所定のパターンのインク保持部が形成されたフレキソ印刷版11に保持させる工程と、このフレキソ印刷版11に、絶縁透光性基板10を密着させ、上記インク保持部に保持された導電性インクを基板10の所定位置に転写する工程と、この転写後に上記転写された導電性インクを加熱して、絶縁透光性基板10上に、所定パターンの透明導電膜を形成する工程と、を備える。

(もっと読む)

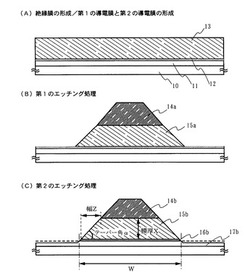

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

221 - 240 / 2,474

[ Back to top ]