Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

181 - 200 / 2,474

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

MOSトランジスタの製造方法

【課題】 本発明は、メタルソース/ドレインを有するMOSトランジスタにおいて、メタルソース/ドレインの位置制御且つショットキーバリアハイトの制御の両者を実現できる技術を提供することを課題とする。

【解決手段】 SOI層上にゲート電極構造を形成する工程と、該ゲート電極構造をマスクにSOI層上に窒素添加Ni膜を成膜する工程と、窒素添加Ni膜上にTiN膜を形成する工程と、窒素雰囲気中でアニールしSOI層中にMOSトランジスタのソース及びドレインとなるエピタキシャルNiSi2層を形成する工程と、TiNと残ったNi膜を除去する工程と、該ゲート電極構造をマスクに該エピタキシャルNiSi2層中にPイオンを注入する工程と、該Pイオンを活性化アニールする工程とを含むMOSトランジスタの製造方法。

(もっと読む)

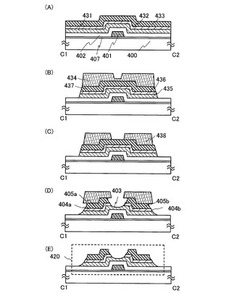

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

酸化物半導体用電極、その形成方法、及びその電極を備えた酸化物半導体装置

【課題】薄膜トランジスタなどの素子動作層をなす導電性インジウム含有酸化物半導体層に電気的接触抵抗が小さい金属電極を形成できるようにする。

【解決手段】インジウム含有酸化物半導体層とその層の上方に設けた素子動作電流を流通させる金属電極層との間に、酸化物半導体層をなすインジウム酸化物などを化学的に還元でき、且つ易酸化性の金属からなる金属膜を素材とした金属酸化物層と金属層とを設け、更に、金属酸化物層と金属層との境界には還元されたインジウムを蓄積したインジウム濃化層を設ける構成とする。

(もっと読む)

電子素子用金属層、電子素子用金属層積層体、電子素子、トランジスタ素子

【課題】電流のリークを抑制する電子素子用金属層を提供する。

【解決手段】被形成面12に、金属インクを塗布し金属粒子層を形成しパターニングする。基板側からランプ照射し、金属粒子層の下層部分のみを溶融させ、下層部分の金属粒子どうしを融着させる。金属粒子の融着層14Aと金属粒子の非融着層14Bとをこの順で有する積層体で構成されたゲート電極14とする。

(もっと読む)

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な金属配線用膜を提供すること。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層(第1層)と、Al系膜からなる第2層とを含む積層構造を有することに要旨を有する配線用膜。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

配線の形成方法および形成装置

【課題】有機導電性材料を含む塗布組成物をプラスチック基板上に形成した後、高い電気電導度の配線を形成することができる配線の形成方法および形成装置を提供すること。

【解決手段】プラスチック基板上に有機導電性材料を含む塗布組成物が塗布されて配線パターンが形成された部材を準備し、少なくとも前記配線パターンに電磁波を照射してアニールし、有機導電性材料からなる配線を形成する。

(もっと読む)

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】薄膜トランジスタは、第1方向に形成された少なくとも1本のゲートラインを含むゲート11と、ゲート上に形成されたゲート絶縁層12と、ゲート絶縁層12上に形成された少なくとも1つのソース13及びドレイン14と、を含み、ソース13及びドレイン14のうち少なくともいずれか一つは、延長部分13b、14bを含み、延長部分13b、14bは、少なくとも1本のゲートラインと平行するように、第1方向に形成される。ゲート11は、ライン状に均一厚を有し、その側面と上面との間に曲面を含み、1本または2本以上のゲートラインを含む形態となる。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子、インクジェットインク

【課題】接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】カーボンナノホーンを含んで構成された有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】電極材料が拡散するのを抑制し、特性の向上を実現する。

【解決手段】半導体装置を、ゲート電極3とゲート絶縁膜2との間、Al含有オーミック電極4、5とAu配線9との間、及び、ゲート電極3の下方及びAl含有オーミック電極4、5の上方、のいずれかに設けられ、第1TaN層6A、Ta層6B、第2TaN層6Cを順に積層した構造を有する電極材料拡散抑制層6を備えるものとする。

(もっと読む)

181 - 200 / 2,474

[ Back to top ]