Fターム[4M104AA09]の内容

Fターム[4M104AA09]に分類される特許

321 - 340 / 2,474

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

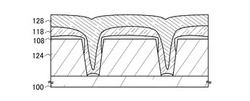

薄膜トランジスタ及びこれを用いた表示装置、並びに、薄膜トランジスタの製造方法

【課題】オフ電流を抑制するとともにオン電流を確保することができる薄膜トランジスタを提供する。

【解決手段】基板10と、基板の上方に形成されたゲート電極11及びゲート絶縁膜12と、ゲート絶縁膜を介して配置されたチャネル層13と、チャネル層に接続されたバッファ層14と、バッファ層に接続され、不純物が添加された第1コンタクト層15a(15b)と、第1コンタクト層に接続され、第1コンタクト層よりも不純物濃度が高い第2コンタクト層16a(16b)と、第2コンタクト層に接続されたソース電極17S及びドレイン電極17Dとを備える。ソース電極とドレイン電極との間におけるキャリアの移動経路は、チャネル層、バッファ層、第1コンタクト層及び第2コンタクト層を経由してキャリアが移動する第1経路と、チャネル層及び第2コンタクト層を経由してキャリアが移動する第2経路とを含む。

(もっと読む)

導電部形成方法、導電部及び発光装置

【課題】導電部の欠損を防止すること。

【解決手段】Al含有膜2からなるゲートラインLgやコンタクト部42などの導電部を形成する際に、下層保護導電膜/Al含有膜/上層保護導電膜の導体膜を成膜した後、その導体膜に改質処理として酸化処理を施して、上層保護導電膜3で覆われずにピンホールPから露出してしまったAl含有膜2部分に酸化保護領域4を形成することによって、Al含有膜2がレジストの剥離液などに晒されて消失してしまうことを防ぎ、導電部の欠損を防止した。

(もっと読む)

感光性塗布型電極材料を用いたTFTの製造方法

【課題】従来の電極方法であるフォトリソグラフィ、マスクスパッタリングは、工程の簡略化、材料使用効率、コスト、多様な基板サイズに対応において解決するには困難な課題があり、インクジェット方式では高精細度なパターンが得られないという課題がある。

【解決手段】感光性塗布型電極材料を用いて、所望の電極パターンニングを行う。本発明による電極作成工程において、コストメリットがある拡散光を光源とするランプを用いて第1の露光と第1の露光よりも大きい露光量をもった第2の露光を施すことで、所望の電極パターンを得ることができる。拡散光を用いた2回露光プロセスによって、例えばTFT作成において従来の方法では解決できない材料使用効率、コスト、多様な基板サイズに対応という課題かつ、インクジェット方式では解決できない高精細パターニングを解決するものである。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

パターン画像の形成方法

【課題】有機薄膜トランジスタソース/ドレイン電極などに適する厚みが均一で高精細なパターン画像の形成方法を提供する。

【解決手段】特定の構造単位を有するポリイミド前駆体及び該ポリイミド前駆体を脱水閉環して得られるポリイミドからなる群より選ばれる少なくとも一種の重合体を含むパターン画像下層膜形成液を基板上に塗布し、乾燥、焼成することでパターン画像下層膜を得る工程と、

得られるパターン画像下層膜に紫外線を照射しパターン画像下層膜の濡れ性を変化させる工程と、

パターン画像形成液が付着したブレードと上記パターン画像下層膜とを相対的に移動させることにより、上記パターン画像下層膜の紫外線照射領域に上記パターン画像形成液を塗布させ、乾燥する工程と、

を有することを特徴とする。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】柱状結晶構造を有する金属を用いた場合でも、簡便な方法で、再現性良く階段構造状のテーパーを有する電極を形成する。

【解決手段】真空状態を保ったままの状態において、同一種類の金属を用いて、スパッタリング法で少なくとも2層の金属膜を成膜する成膜工程と、該成膜工程によって成膜された複数の金属膜にエッチング処理を施すことにより、階段構造状のテーパー形状を端部に有する、ゲート電極、ソース電極およびドレイン電極のうちの少なくとも1つを形成するエッチング工程とによって薄膜トランジスタを製造する。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38及びソース電極34はドレイン電極36を囲み、ソース電極34の上部に、ゲート電極38の上方を通過してドレイン電極36側に庇状に突き出したフィールドプレート170が形成され、GaN系エピタキシャル基板32の表面層とフィールドプレート170との間に、誘電体膜46が形成され、誘電体膜46は、フィールドプレート170の直下領域においてフィールドプレート終端面と面一状態となるように切れ込み、その下端からドレイン電極36に接続するようにドレイン電極36に向かって延びている。

(もっと読む)

ウェットエッチング性に優れた表示装置用配線膜

【課題】ウェットエッチング性が良好な表示装置用配線膜を提供する。

【解決手段】希土類金属元素、Zn、Mg、およびCaよりなる群から選択される少なくとも一種の元素を5原子%以上50原子%以下の範囲で含むMo合金と、純CuまたはCu合金との積層構造を有する表示装置用配線膜である。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、疎水化処理を要することなく、フォトリソグラフィー技術による酸化シリコン膜のパターニングが可能な半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明は、基板上に形成された酸化シリコン膜上に機能層を形成する機能層形成工程と、上記機能層上に第1フォトレジストを塗布し、フォトリソグラフィー法により上記機能層および上記酸化シリコン膜をパターニングし、上記第1フォトレジストを除去する第1パターニング工程と、パターニングされた上記機能層上に第2フォトレジストを塗布し、フォトリソグラフィー法により上記機能層をさらにパターニングし、上記第2フォトレジストを除去する第2パターニング工程とを有し、上記機能層と上記第1フォトレジストおよび上記第2フォトレジストとの接触角が20度以下であることを特徴とする半導体素子の製造方法を提供する。

(もっと読む)

電界効果型有機トランジスタ

【課題】ゲート絶縁層に含まれる高誘電体粒子がゲート電極側に偏在していない場合に比べ、低電圧でも駆動する電界効果型有機トランジスタを提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、チャネル層と、ソース電極と、ドレイン電極と、を有し、前記チャネル層は有機半導体層であり、前記ゲート絶縁層は高誘電体粒子及び絶縁性樹脂を含み、前記高誘電体粒子がゲート電極側に偏在している電界効果型有機トランジスタ。

(もっと読む)

薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板

【課題】静電気による薄膜トランジスタの閾値電圧変動や絶縁破壊短絡を抑制できる薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板を提供する。

【解決手段】薄膜トランジスタと、静電気誘導素子と、を基板上に有する薄膜トランジスタ回路基板の製造方法であって、基板に設けられた半導体層の上に、薄膜トランジスタの半導体層のパターンを形成する第1のフォトリソ工程と、静電気誘導素子の半導体層のパターンを形成する第2のフォトリソ工程と、基板に設けられた半導体層をエッチングする工程と、を実施することにより薄膜トランジスタの半導体層及び静電気誘導素子の半導体層を形成し、第1のフォトリソ工程におけるフォトレジストの硬化温度は、第2のフォトリソ工程におけるフォトレジストの硬化温度よりも高いことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

液晶表示装置および液晶表示装置の製造方法

【課題】液晶表示装置の製造コストの低減を図る。

【解決手段】電界効果型の薄膜トランジスタを備える液晶表示装置であって、薄膜トランジスタの半導体層に、インジウムを材料に含む透明アモルファス酸化物半導体が用いられ、半導体層は、ソース電極およびドレイン電極並びにそれらの電極線として必要な領域を含む形状に形成され、半導体層に積層されるソース・ドレイン層に、インジウムを含む金属薄膜が用いられ、ソース・ドレイン層に積層される絶縁層に、窒化珪素による絶縁膜が用いられ、薄膜トランジスタのチャネル部が、絶縁層とソース・ドレイン層とに設けられた開口部によって形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】有機TFTは、ゲート電極2および有機半導体層6と、それらの間に位置すると共に有機半導体層6に隣接するゲート絶縁層3とを備えている。このゲート絶縁層3は、スチレンおよびその誘導体のうちの少なくとも一方である第1単量体(α−メチルスチレンなど)と、炭素間二重結合および架橋性反応基を有する第2単量体(メタクリル酸グリシジルなど)とが共重合および架橋された材料を含んでいる。

(もっと読む)

321 - 340 / 2,474

[ Back to top ]