Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,761 - 2,780 / 2,965

半導体装置およびその製造方法

【課題】 基板浮遊効果を抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】 絶縁層と、前記絶縁層の上方に形成された半導体層と、前記半導体層の上方に形成されたゲート絶縁層と、前記ゲート絶縁層の上方に形成されたゲート電極と、前記半導体層に形成されたソース領域およびドレイン領域と、前記ゲート絶縁層の下方に形成されたボディ領域と、前記半導体層において、前記ボディ領域に対して前記ソース領域側に形成され、かつ、前記ボディ領域とショットキー接合する複数のショットキー接合領域と、を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】従来と同等の駆動力を確保しつつ、ヘテロ界面で生じる漏れ電流を低減することが可能な高耐圧電界効果トランジスタを容易に製造する。

【解決手段】基板1とドレイン領域2からなる半導体基体の一主面側に第二のヘテロ半導体領域形成用半導体層400を積層する工程と、所定の開口14を有するマスク層9をマスクとして用いて、第二のヘテロ半導体領域形成用半導体層400を選択的にエッチングして第二のヘテロ半導体領域4を形成する工程と、マスク層9を有した状態で、第一のヘテロ半導体領域形成用半導体層300を積層する工程と、第一のヘテロ半導体領域形成用半導体層300を選択的にエッチングして第一のヘテロ半導体領域3を形成する工程と、第一のヘテロ半導体領域3並びに半導体基体に接するようにゲート絶縁膜5を形成する工程を有する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 製造工程を単純化し、製造費用を最少化でき、かつ安定した特性を確保できる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタ表示板は、画素部と駆動部を有する絶縁基板、絶縁基板上に形成され、ソース領域及びドレイン領域、チャンネル領域及び低濃度ドーピング領域を有する多結晶シリコン層、多結晶シリコン層を覆うゲート絶縁膜、ゲート絶縁膜を介在してチャンネル領域と重畳し、不純物がドーピングされているケイ素を有する不純物層、不純物層上部に形成されているゲート電極、ゲート電極を覆い、各々ソース領域及びドレイン領域を露出させる第1及び第2コンタクトホールを有する層間絶縁膜、層間絶縁膜上に形成され、第1コンタクトホールを介してソース領域と接続されるソース電極、層間絶縁膜上に形成され、第2コンタクトホールを介してドレイン領域と接続されるドレイン電極を有する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

【解決手段】基板101上に第1の膜102を形成する工程と、前記第1の膜102上にマスク材料を含有する溶液を吐出して前記第1の膜102上にマスク103を形成する工程と、前記マスク103を用いて前記第1の膜102をパターニングして前記基板101上に塗れ性の低い領域104と塗れ性の高い領域105を形成する工程と、前記マスク103を除去する工程と、前記塗れ性の低い領域104に挟まれた前記塗れ性の高い領域105に、絶縁膜、半導体膜又は導電膜材料を含有する溶液106を吐出して絶縁膜、半導体膜又は導電膜のパターンを形成する工程とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ソースおよびドレインにおける接合リークを抑制し、膜厚が互いに異なるシリサイドをゲート電極に含むトランジスタを同一半導体基板上に備えた半導体装置を提供する。

【解決手段】 半導体基板10の表面に形成された第1のソース層13aおよび第1のドレイン層23aとこの上に形成された第1のシリサイド層14aと、半導体基板表面に設けられた第1のゲート絶縁膜5a上に形成され、第2のシリサイド層20aを有する第1のゲート電極6aと、前記第1のゲート電極の側壁に設けられたシリコン窒化膜9aとを含む第1のトランジスタ101および、半導体基板10の表面に形成された第2のソース層13bおよび第2のドレイン層23bと、この上に形成され、第1のシリサイド層14aと膜厚が同じである第3のシリサイド層14bと、半導体基板表面に設けられたゲート絶縁膜5b上に形成され、第2のシリサイド層20aと膜厚が異なる第4のシリサイド層20bを有する第2のゲート電極6bとを含む第2のトランジスタ102、を備えている。

(もっと読む)

無線チップ及びその作製方法

【課題】本発明は、無線チップのコストを下げることを課題とする。また、無線チップの大量生産を可能として、無線チップのコストを下げることを課題とする。さらに、小型・軽量な無線チップを提供することを課題とする。

【解決手段】本発明は、ガラス基板や石英基板から剥離された薄膜集積回路が第1の基体と第2の基体に設けられた無線チップを提供する。本発明の無線チップは、シリコン基板からなる無線チップと比較して、小型、薄型、軽量を実現する。本発明の無線チップが含む薄膜集積回路は、少なくとも、LDD(Lightly Doped drain)構造のN型の薄膜トランジスタと、シングルドレイン構造のP型の薄膜トランジスタと、アンテナとして機能する導電層とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】 半導体装置がオフのときに、ドリフト層内の電界強度を高くし、半導体装置の耐圧を向上させる。

【解決手段】 IGBTにおいて、ドリフト層28内を伸びてバッファ層26に達するとともに、バッファ層26とドリフト層28の界面に沿って分散配置されている絶縁領域62が形成されている。この絶縁領域62は、バッファ層26とドリフト層28の界面の電界強度を高くすることができる。これにより、ドリフト層28内の電界強度を膜厚方向に積分した値が増大するので、IGBTの耐圧が向上される。

(もっと読む)

リンが注入されたポリシリコンのシート抵抗の減少

リンが注入されたポリシリコンのシート抵抗を減少するプロセスが存在する。一実施の形態において、MOSトランジスタ構造(300)が存在する。構造は、ゲート領域、ドレイン領域及びソース領域を有する。ゲート領域のシート抵抗を減少する方法(220)は、予め決定された温度で真性アモルファスシリコンをゲート領域に堆積する(221)。アモルファス化の種が、真性アモルファスシリコンに注入される(222)。その後、リンの種が、MOSトランジスタ構造のゲート領域に注入される(223)。この実施の形態の特徴は、アモルファス化の種としてのAr+の使用を含む。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】シリコン窒化膜を堆積してもシート抵抗が上昇しない配線構造を提供する。

【解決手段】半導体基板上に第一の高融点金属膜5を形成する工程と、前記第一の高融点金属膜上に高融点金属窒化物の反応物7を持つ第二の高融点金属膜6Aを形成する工程と、前記第二の高融点金属膜上にシリコン窒化膜8を形成する工程とからなる。これにより、シリコン窒化膜の膜質を変化させることなく、また成膜時のパーティクルの発生を従来方法と同等としたまま、シリコン窒化膜下の高融点金属のシート抵抗の上昇を最小限に抑えることができる。

(もっと読む)

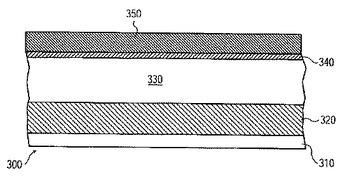

ポリシリコンゲルマニウムゲートスタック及びその形成方法

従来のCMOSゲートスタックと比べて反転キャパシタンスを増大させるCMOSゲートスタックが記載される。ゲート誘電体層に近い従来のポリSiゲートの代わりに、ポリSiGeゲートを用いて、活性化され得る埋込まれたドーパント量を増加させる。この増加は、従来のCMOSゲートスタックにおける反転キャパシタンスを制限するポリシリコンの枯渇を克服する。ポリSiGe層をゲートスタックに組込むために、ゲート誘電体層とポリSiGe層との間にSi薄層を堆積させる。適切なサリサイド形成を確実にするために、ポリSiGe層の上にポリSi層のキャップを被せる。ポリSiGeの上に微粒子のポリSiを得るために、ポリSi層とポリSiGe層の間に第2のSi層を堆積させる (もっと読む)

半導体装置およびその製造方法

【課題】抵抗値を低減してRC遅延を低減でき、高速化に有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子分離領域10と、この素子分離領域に囲まれた素子領域AAとを有する半導体基板11と、前記素子領域の前記半導体基板上に形成された第1ポリシリコン層13と、前記素子分離領域の前記半導体基板表面に形成された素子分離絶縁膜22と、この素子分離絶縁膜上に形成された第2ポリシリコン層25と、前記第1ポリシリコン層上に形成された第1シリサイド層13Sと、この第1シリサイド層の膜厚より厚く、前記第2ポリシリコン層上に形成された第2シリサイド層25Sとを備える。

(もっと読む)

電界効果トランジスタ

【課題】 基板バイアス電圧を印加することなく、正確且つ確実な低温動作を実現する構成を有する電界効果トランジスタを提供する。

【解決手段】 本発明の実施の一形態に係る電界効果トランジスタは、300K以下の温度条件で動作することが想定された電界効果トランジスタであって、4.05未満の仕事関数WFnを有するゲート電極材により形成されたゲート電極を備えているnチャネル電界効果トランジスタを含むものである。また、本発明の実施の一形態に係る電界効果トランジスタは、5.17を超える仕事関数WFpを有するゲート電極材により形成されたゲート電極を備えているpチャネル電界効果トランジスタを含み得るものである。

(もっと読む)

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 黒鉛の発生を充分に回避しながら、n型SiC基板に対して良好なオーミック接触を得ることができるSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】 n型SiC基板1の電極形成領域上に、第1層2a1を形成し、第1層2a1上に第2層2b1を形成し、第1層2a1及び第2層2b1に対してアニールを施すことにより、前記電極形成領域上に電極を形成するSiC半導体装置10Aの製造方法であって、前記第1層2a1は、Ni、Cu、W、Co、Mo、Ta、Pd、Tiのいずれかと、Ni、Cu、W、Co、Mo、Ta、Pd、Tiのうちの2つ以上からなる合金と、のうちの一つで形成し、前記第2層2b1は、Siで形成することを特徴とする。

(もっと読む)

半導体デバイス及び同デバイスを形成する方法

MOSFETの製造において、MOSFETに関する幾つかの構造的目的を果たす再酸化段階を提供することが知られている。しかしながら、より小型の集積回路用のドライブを収容するMOSFETのゲート絶縁層用の高誘電率材料を提供する必要性によって、ゲート絶縁層と基板との間のSiO2界面層の過剰な成長をもたらした。SiO2層の過剰成長は、MOSFET内の漏れ電流の増大につながる酸化膜換算膜厚(EOT)を生じる。更に電極としてポリシリコンを金属と置き換えることは、処理中の酸素曝露を妨げる。結果として、本発明は、MOSFETのゲート電極(32)の少なくとも側壁(34)を覆う酸素障壁層(40)の堆積段階と再酸化段階とを置き換え又は先行して行うことで、誘電界面及び金属ゲート電極への酸素拡散のための障壁を形成し、EOTの増大を防ぎ金属ゲート電極の完全性を保持する。 (もっと読む)

半導体装置

【課題】 高誘電率膜により構成されたゲート絶縁膜と、P型不純物を含む多結晶シリコン膜により構成されたゲート電極とを含む半導体装置において、閾値電圧の増加を抑制する。

【解決手段】 P型MOSFET120は、半導体基板(Nウェル102b)と、半導体基板上に形成され、Hf、Zr、およびランタノイド元素のいずれかからなる群から選択される第一の元素と、ならびにNとを含むシリケート化合物を含む高誘電率膜108により構成されたゲート絶縁膜と、ゲート絶縁膜上に形成されるとともに、P型不純物を含む多結晶シリコン膜114により構成されたゲート電極と、ゲート絶縁膜とゲート電極との間に形成され、第一の元素と多結晶シリコン膜114との反応を阻止するとともに、比誘電率が8以上の阻止酸化膜110と、を含む。

(もっと読む)

金属層を有する半導体素子の形成方法

半導体基板(12)上に形成された金属酸化物(14)上に金属層(24)を形成する。金属層の所定の限界寸法を決定する。第1エッチングにより金属層を下方へと金属酸化物に至るまでエッチングし、金属層の側壁にフーティング(26)を形成する。金属酸化物に対し選択的である第2エッチングにより、所定の限界寸法を狙ってフーティングを除去する。一実施形態において、金属層上に導電層(22)を形成する。金属層と接触している部分を残存させつつ、導電層の大部分をエッチングする。次に、金属層と接触している残余部分を、金属層に対して選択的な化学物質を用いてエッチングする。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】 異方性ドライエッチングによって所望の適正な加工形状を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板11と、半導体基板上に形成されたゲート絶縁膜12と、ゲート絶縁膜上に形成されたゲート電極膜13とを含む被処理体10をチャンバーに導入する工程と、チャンバー内で、異方性ドライエッチングによりゲート電極膜をゲート絶縁膜に対して選択的にエッチングしてゲート電極を形成する工程と、を備えた半導体装置の製造方法であって、ゲート電極を形成する工程は、少なくともゲート絶縁膜の一部が露出した後に、チャンバー内におけるエッチングガスのレジデンスタイムが100ミリ秒以下となる条件でゲート電極膜をエッチングする工程を含む。

(もっと読む)

半導体装置、およびその半導体装置を用いた電力変換器、駆動用インバータ、汎用インバータ、大電力高周波通信機器

イオン注入で形成されたP型、N型の不純物半導体領域を有する炭化珪素半導体基板を用いた半導体装置において炭化珪素半導体基板表面の凹凸を小さくすることにより、最終的に半導体装置の電気特性を向上できるようにする。この発明の半導体装置は、(000−1)面あるいは(000−1)面からある角度傾いた面を最表層面として有する炭化珪素半導体領域1,2に、P型半導体領域3およびN型半導体領域の少なくとも一方がイオン注入により選択的に形成され、その最表層面に金属電極が形成され、その金属電極に電圧を印加することにより最表層面に垂直な方向に流れる電流の方向を制御するショットキー・バリア・ダイオード、若しくはPN型ダイオードである。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 多結晶Si膜と高誘電率絶縁膜との界面特性を簡単な手段を適用することで改善し、高誘電率ゲート絶縁膜を用いたMOS−FETに於ける閾値電圧Vthがシフトする問題を解消しようとする。

【解決手段】 SiO2 に比較して高い誘電率の材料、例えばHfO2 からなるゲート絶縁膜3GをもつMOS−FETを製造する工程に於いて、ゲート電極用の多結晶Si膜3を成膜後のゲート加工前の状態で高誘電率絶縁膜2と多結晶Si膜3との界面特性を改善する為に酸化雰囲気中で熱処理を行う工程が含まれてなることを特徴とする。

(もっと読む)

2,761 - 2,780 / 2,965

[ Back to top ]