Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,821 - 2,840 / 2,965

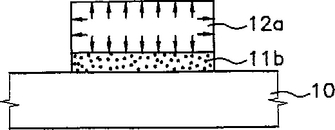

LCDのTFT基板及びその製造方法

【課題】 液晶表示装置の薄膜トランジスタ基板及びその製造方法が開示されている。

【解決手段】 シリコン元素を含む基板、前記基板上に形成された拡散防止膜、及び前記拡散防止膜上に形成され、前記拡散防止膜形成物質が0.5〜15at%範囲で含まれた銅合金層を含んで形成される。前記拡散防止膜は、Zr、Ti、Hf、V、Ta、Ni、Cr、Nb、Co、Mn、Mo、W、Rh、Pd、Pt等のような化合物を50〜5000Å範囲で蒸着して熱処理して、シリサイド化合物に変換して製造する。銅合金配線を用いてトランジスタ基板を製造するので、低い抵抗と高い伝導度を具現することができる。又、薄い厚さの拡散防止膜と同じ元素を添加した銅合金と用いて銅配線を形成したので、同時エッチングが可能であり、後続工程で基板との相互拡散を防止することができる。  (もっと読む)

(もっと読む)

ウェハ接合によって製造される半導体−誘電体−半導体デバイス構造体

【課題】 デバイス性能を犠牲にすることなく様々なゲート材料の使用を可能にする、半導体基板上に少なくとも部分的にゲート・スタックを作るための技術を提供する。

【解決手段】 高k誘電材料を含む少なくとも1つの構造体のウェハ接合を利用して、半導体電子デバイスのためのゲート・スタックを形成する方法が提供される。本発明の方法は、まず、それぞれが主面を有する第1及び第2の構造体を選択するステップを含む。本発明によれば、第1及び第2の構造体の少なくとも一方又は両方は、少なくとも高k誘電材料を含む。次に、第1及び第2の構造体の主面同士を接合して、ゲート・スタックの高k誘電材料を少なくとも含む接合構造体を形成する。

(もっと読む)

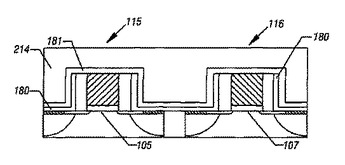

半導体装置及びその製造方法

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

デュアル・ゲートCMOSの製造

本発明は、CMOS素子を製造する方法に関し、その方法は、絶縁材料層(102)をその中に有する半導体基板(101)を準備するステップと、絶縁層(102)の上に第1の材料層(106)を形成するステップとを備え、第1の材料層(106)の厚さが、第1の能動素子を担持する第1の領域(103)では、第2の能動素子を担持する第2の領域(104)より薄い。次いで、第2の材料層(107)が、第1の材料層(106)上に形成され、次いで、その構造体に熱処理が行われて、第1と第2の材料が合金化される。第1の領域上の両層部分は全体が合金化されるが、第2の領域上の両層部分はそうはならず、その結果、第1の材料層(106)の一部分(109)が残留する。  (もっと読む)

(もっと読む)

半導体製造装置システム及びそれを用いた半導体装置の製造方法

本発明は、効果的にシステムLSIの少量多品種生産を実現するための、プロセス開発期間の短縮を目的とする。本発明は、半導体ウエハ主面の複数ブロックにゲート電極パターンをドライエッチングにより形成するための半導体製造装置システムであって、ゲート電極パターン形成時におけるブロック内の被エッチング面積比に対するレシピが格納されたデータベースと、半導体ウエハに表示された被エッチング面積比の認識情報を読み取る手段と、ドライエッチング装置とを有し、前記認識情報に対するデータベースに格納されたレシピを検索し、該レシピにより前記ドライエッチング装置を制御することを特徴とする。  (もっと読む)

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】 高い信頼性を有する半導体素子を提供する。

【解決手段】

ドリフト領域11の表面領域にはベース領域13が形成され、ベース領域13の表面領域にはソース電極14が形成され、ドリフト領域11上には、酸化膜20、ゲート電極30、及び、層間絶縁膜40が形成されている。ソース領域14、酸化膜20、及び、層間絶縁膜40には、層間絶縁膜40上のソース電極50とベース領域13及びソース領域14とを接続するためのソース開孔50aが形成されている。酸化膜20は、ゲート電極30下の厚い第1酸化膜と、ソース開孔50aの外縁から延伸する薄い第2酸化膜と、第1酸化膜と第2酸化膜との間に配置され、第1酸化膜と第2酸化膜との中間の厚さを有する第3酸化膜と、から構成される。これにより、酸化膜20の厚さは、ソース開孔50aの外縁からゲート電極30に向かって階段状に増加する。

(もっと読む)

半導体基板内の分離溝に隣接するコンタクト用開口の形成方法

【課題】フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法を提供する。

【解決手段】トレンチ形成・埋め込み法によって半導体基板の中にフィールド分離マスを形成し、該フィールド分離マスに隣接した基板上に基板マスキング層を形成する工程であって、前記フィールド分離マスの上面はエッチングストップキャップによって覆われ、その側壁は前記マスキング層によって覆われる工程と、前記分離マス側壁の少なくとも一部を露出するために、分離マスから分けて前記基板マスキング層を除去する工程と、露出した分離マス側壁上にエッチングストップカバーを形成する工程と、前記分離マス及び該分離マスに隣接する基板領域上に絶縁層を形成する工程と、前記分離マスエッチングストップキャップ及びカバーに対して選択的に、前記分離マスに隣接する前記絶縁層を貫通するコンタクト用開口をエッチング開口する工程とからなる、フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

サリサイド工程及びこれを利用した半導体素子の製造方法

【課題】サリサイド工程及びこれを利用した半導体素子の製造方法を提供する。

【解決手段】 本発明による金属シリサイド膜の形成方法は、シリコン領域を備える基板を準備する段階と、前記基板上にシリコン層を形成する段階と、前記シリコン層と接触する金属膜を形成する段階と、前記金属膜を有する基板を熱伝達気体を採択した対流または伝導方式を使用して等温熱処理して前記少なくとも前記金属膜の一部を金属シリサイド膜に転換する段階と、を含む。

(もっと読む)

陥没トレンチを用いた表面側ドレインを有する半導体電力素子

本発明による半導体電力素子は、第1導電型を有する基板と、該第1導電型を有し且つ該基板の表面を覆ってこれと接触するエピタキシャル層とを含む。第1トレンチが該エピタキシャル層の内部に伸張してそこで終端する。陥没トレンチが該エピタキシャル層の表面から伸張し該エピタキシャル層を通って該基板の内部で終端する。該陥没トレンチは、該第1トレンチの横に間隔をおいて設けられ、該第1トレンチよりも広く且つ深く伸張する。該陥没トレンチは自身の側壁に沿ってのみ絶縁体によって裏打ちされることで、該陥没トレンチを充填する導電材料が該基板との電気的接続を該陥没トレンチの底部に沿ってなすと共に、相互接続層との電気的接触を該陥没トレンチの表面側に沿ってなす。  (もっと読む)

(もっと読む)

PMOSを具備する半導体素子の形成方法

【課題】本発明はPMOSを具備する半導体素子を形成する方法を提供する。

【解決手段】前記方法によると、半導体基板の全面上にポリシリコン膜を形成する。前記ポリシリコン膜にP型不純物をドーピングする。熱処理工程を進行する。そして、前記P型不純物がドーピングされたポリシリコン膜の上部を第1厚さだけ除去する。これによって、漏洩電流を防止して、素子の速度を向上させることができるPMOSを具備する半導体素子を形成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ドライエッチングにより半導体基板やポリシリコン層に生じるダメージ層を効果的に除去して、寄生抵抗や接合リークが低減された半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記絶縁膜を、ドライ工程によりエッチングする工程と、前記エッチングにより前記半導体基板上に生じたダメージ層を、熱分解した原子状の水素により、所定の温度下で除去する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド領域および非シリサイド領域を有する半導体装置において、接合リーク電流を低減する方法を提供する。

【解決手段】第1のトランジスタ10と半導体素子20とを覆うシリコン酸化膜30を形成した後、非シリサイド領域をフォトレジスト4で覆う。この状態でスパッタエッチングを行うことにより、シリサイド領域におけるシリコン酸化膜30のうちサイドウォールスペーサ14を覆う部分の肩部を除去する。その後、異方性ドライエッチングを行うことによりシリサイド領域におけるシリコン酸化膜30のうちサイドウォールスペーサ14の下端部と接する部分以外を除去し、フォトレジスト4を除去した後、ウェットエッチングを行う。その後、非シリサイド領域において残存するシリコン酸化膜30をマスクとして、シリサイド領域に対してシリサイド化を行う。

(もっと読む)

半導体装置

【課題】 同一基板上にゲート絶縁膜の耐圧の異なる複数の電界効果型トランジスタを設ける際に、これを簡便なプロセスで作製する。

【解決手段】 シリコン基板101上に高耐圧トランジスタ102および低耐圧トランジスタ104が形成された半導体装置100において、高耐圧トランジスタ102のポリシリコンゲート電極膜117のゲート不純物濃度を低耐圧トランジスタ104のゲート不純物濃度よりも小さくする。

(もっと読む)

半導体基板洗浄用組成物を用いた半導体装置製造方法

【課題】不純物の除去力を向上させながらも、金属層の損傷を最小化することができる半導体基板洗浄用組成物を用いた半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法において、半導体基板上に金属を含む構造物パターン形成し酸性水溶液78ないし99.98質量%、第1キレート剤0.01ないし11質量%を含む半導体基板洗浄用組成物を、半導体基板に適用して構造物パターンの不純物が覆っていない第1表面部位上に第1腐食抑制膜を形成し、構造物パターンの不純物が覆っている第2表面部位上の不純物を除去する。

(もっと読む)

絶縁ゲート型半導体装置及びその駆動方法

【課題】 絶縁ゲート型半導体装置及びその駆動方法に関し、高駆動電流化及び微細化構造においても基板バイアス効果によってオフリークIoff を低減して低消費電力化を実現する。

【解決手段】 幅が3〜20nmの第1のサイドウォール4、幅が30nm〜60nmの第2のサイドウォール5、及び、その外側に第3のサイドウォール6を有するとともに、第1のサイドウォール4の直下に第1のサイドウォール4と自己整合する長さのエクスエンション領域7を設けるとともに、第2のサイドウォール5の直下に第2のサイドウォール5と自己整合する長さで且つエクステンション領域7と深接合のソース・ドレイン領域9の中間の深さのバッファ領域8を設けてソース・ドレイン構造を3重構造にする。

(もっと読む)

半導体デバイスのゲートのクリティカルディメンションを改善するためのゲート材料のプレーナ化

半導体デバイス(100)を製造する方法は、絶縁体(120)上にフィン構造(210)を形成するステップを含む。このフィン構造(210)は、側面および上面を含んでいてもよい。この方法はさらに、フィン構造(210)上にゲート材料(320)をたい積するステップと、たい積したゲート材料(320)をプレーナ化するステップを含んでいてもよい。反射防止膜(520)は、プレーナ化したゲート材料(320)上にたい積することができ、また、ゲート構造(510)は、反射防止膜(520)を使用して、プレーナ化したゲート材料(320)から形成することができる。  (もっと読む)

(もっと読む)

カーボンナノチューブトランジスタの製造方法

【課題】 カーボンナノチューブトランジスタの製造方法に関し、カーボンナノチューブトランジスタの製造歩留まりを向上させる。

【解決手段】 ソース部5、ドレイン部6、及び、ソース部5とドレイン部6との間の領域以外の領域上に堆積したカーボンナノチューブ9を除去する。

(もっと読む)

半導体装置

【課題】光近接効果に起因するトランジスタのゲート長ばらつきを抑制しうる半導体装置を提供する。

【解決手段】半導体装置は、P型拡散領域,N型拡散領域及び素子分離領域に跨って形成され、拡散領域上に位置するゲート電極部G21a〜G21cと、素子分離領域上に位置するゲート配線部G22a〜G22cとを有する複数のゲートポリシリコン膜G20a〜G20cを備えている。そして、層間絶縁膜を貫通して、ゲート配線部G22a〜G22cに接続されるゲートコンタクトC23a〜C23cと、各ゲートコンタクトC23a〜C23cに接続される配線M21とが設けられている。ゲートコンタクトC23a〜C13cの径Rは、ゲートポリシリコン膜G20のゲート長Lよりも大きい。

(もっと読む)

固体撮像素子の製造方法

【課題】 単層電極構造の電荷転送電極を形成するに際し、平坦化工程におけるアクティブ領域の膜減りを防止し、均一な膜厚の配線を形成することにより配線抵抗のばらつきを低減する。

【解決手段】 固体撮像素子の製造方法において、ゲート酸化膜の形成された半導体基板表面に、第1の電極、前記光電変換部および前記周辺回路部の第1層配線を構成する第1層導電性膜のパターンを形成する工程と、前記第1の電極の少なくとも側壁に電極間絶縁膜となる絶縁膜を形成する工程と、前記第1の電極および前記電極間絶縁膜の形成された前記半導体基板表面に第2の電極を構成する第2層導電性膜を形成する工程と、前記第1の電極上に突出する前記第2層導電性膜の突出部を除去し、表面を平坦化する工程と、前記アクティブ領域の前記第2層導電性膜をパターニングする工程とを含み、前記平坦化する工程に先立ち、アクティブ領域に除去抑制層を形成する工程を含む。

(もっと読む)

2,821 - 2,840 / 2,965

[ Back to top ]