Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,861 - 2,880 / 2,965

微小共振器およびその製造方法、ならびに電子機器

【課題】 各共振器素子間における中心周波数のばらつきを抑制することにより周波数特性を確保することが可能な微小共振器を提供する。

【解決手段】 複数の共振器素子Fを有して共振動作に寄与する共振器素子構造体11と共に、その共振器素子構造体11の周囲に配設され、複数の非共振器素子Nを有して共振動作に寄与しない非共振器素子構造体12を併せて備えるように、微小共振器構造体10を構成する。微小共振器構造体10の製造工程においてフォトリソグラフィ処理時に反射光の影響を受けたとしても、その反射光の影響が外郭の非共振器素子Nの形成精度に及びやすい一方で中央の共振器素子Fの形成精度に及びにくいため、非共振器素子Nの形成精度が低下する一方で共振器素子Fの形成精度が確保される。これにより、各共振器素子Fの形成寸法がばらつきにくくなるため、各共振器素子F間において中心周波数がばらつきにくくなる。

(もっと読む)

パターン形成方法を含む半導体装置の製造方法

【課題】 本発明は半導体装置の製造工程において、レジストなどのマスクパターンを用いる際に発生する反応生成物等のレジスト等への不均一な付着によるパターン形状等の不良を生じさせず、また、寸法精度が良好な微細パターンの形成方法を提供することを目的とする。

【解決手段】 パターン形成方法を含む半導体装置の製造方法として、第1の薄膜の側壁に第2の薄膜を形成し、その側壁に形成された第2の薄膜の先端部が不均一にならないように、平坦化法により、精度良くエッチバックして揃える。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、信頼性の高く、且つしきい値電圧の変化量を高めることが可能な半導体不揮発性記憶素子を有する半導体装置の作製方法を提供する。また、信頼性の高い半導体不揮発性記憶素子を有する半導体装置を、大面積基板を用いて製造する方法を提供する。

【解決手段】本発明は、固溶限界を超えるシリコンを有する固溶体をターゲットとしてスパッタリングを行い、固溶体の主成分である金属元素の導電層と、シリコン粒子とからなる導電膜を成膜した後、金属元素の導電層を除去してシリコン粒子を露出する。また、当該シリコン粒子をフローティングゲート電極とする半導体不揮発性記憶素子を有する半導体装置を作製する。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

高信頼性コンタクト

ニッケル基ゲルマニドコンタクトが、コンタクトを形成するための加工中並びにゲルマニド化後のプロセス(post-germanidation processes)中に、ニッケル基ゲルマニドの凝集を妨げる加工助剤を含有する。この加工助剤は、ニッケル層を覆うキャップ層の形をとる、或いは、ニッケル基コンタクトを形成するために使用されるニッケル層内に組み入れられる。凝集を減少させることにより、コンタクトの電気特性を向上させる。  (もっと読む)

(もっと読む)

電子素子の製造方法および電子素子

【課題】 有機半導体層との相性のよい電極を形成した電子素子の製造、及びその製造方法により製造された電子素子を提供する。

【解決手段】 基板上に有機半導体及び/または有機導電体の前駆体の層を形成し、該層を加熱して、有機半導体及び/又は有機導電体の前駆体を有機 半導体及び/または有機導電体とすることにより、パターニングされた電極を形成することを特徴とする電子素子の製造方法、及び該製造方法により製造された電子素子。

(もっと読む)

ゲート酸化膜形成法

【課題】厚さを異にする複数のゲート酸化膜を1回の熱酸化処理により形成する際に厚いゲート酸化を効率的に行なう。

【解決手段】半導体基板10の一方の主表面にフィールド絶縁膜12を形成した後、酸化膜14a,14bとして犠牲酸化膜又はゲート酸化膜を形成する。素子孔12a内にレジスト層16をマスクとし且つ酸化膜14aを介してアルゴン(又はフッ素)イオンを1又は複数回の注入処理により注入してイオン注入層18を形成する。酸化膜14a,14bを犠牲酸化膜としたときはレジスト層16及び酸化膜14a,14bの除去後に素子孔12a,12b内にゲート酸化膜を形成する。酸化膜14a,14bをゲート酸化膜としたときはレジスト層16の除去後に酸化膜14a,14bをエッチングで薄くしてから酸化膜14a,14bを厚くする。イオン注入層18を形成したことで14b対応のゲート酸化膜より14a対応のゲート酸化膜が厚くなる。

(もっと読む)

半導体装置の製造方法

【課題】加工パターンの疎密に依存することなく面内均一に精度良好なパターン加工行うことが可能なエッチング工程を備えた半導体装置の製造方法を提供する。

【解決手段】基板11上にSiOCH系絶縁膜からなる被エッチング膜13を形成し、マスクパターン15上からのプラズマ処理を行う。これにより、マスクパターン15から露出している被エッチング膜13部分をSiO2化して改質部13bを形成する前処理を行う。次に、マスクパターン15およびSiOCH系材料からなる未改質部13aに対して選択的に改質部13bをエッチング除去する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ダミーパターンの面積を大きくしなくても、半導体素子や配線へのプラズマチャージ量を少なくする。

【解決手段】 半導体基板1にトランジスタ11を形成すると共に、半導体基板1上にMNOS素子10を形成する。MNOS素子10に電荷を蓄積した後、層間絶縁膜20を形成する。層間絶縁膜20に、ゲート電極5b上に位置する第1の接続孔20b、及びMNOS素子10上に位置する第2の接続孔20aを形成する。層間絶縁膜20上に、第1の接続孔20bを介してゲート電極5bに接続する配線22bを形成すると共に、第2の接続孔20aを介してMNOS素子10に接続するダミーパターン22aを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】炭化珪素層に対する良好なコンタクトを確保しつつ、炭化珪素層に接続された電極の剥離を抑制する。

【解決手段】炭化珪素層11を有する半導体装置の製造方法であって、(A)炭化珪素層11の上に導電層21を形成する工程と、(B)導電層21と炭化珪素層11を反応させて、炭化珪素層11に接する反応層12およびシリサイド層23からなる合金層を形成する工程と、(C)シリサイド層23の少なくとも一部を除去することにより、反応層12の表面の少なくとも一部を露出させる工程と、露出させた反応層12の表面上に電極層13を形成する工程とを含む。

(もっと読む)

不揮発性半導体記憶装置の製造方法、及び不揮発性半導体記憶装置

【課題】 周辺回路の分離酸化膜上にエッチング残渣を発生させることなく、高いカップリング比を有するメモリセルを有する不揮発性半導体記憶装置を製造する。

【解決手段】 上面が基板1表面よりも高い分離酸化膜6を基板1に形成する。次に、分離酸化膜6間の基板1上にシリコン酸化膜7を形成する。そして、分離酸化膜6間のシリコン酸化膜7上にポリシリコン膜8を自己整合的に形成する。周辺回路を覆うレジストパターン9を形成した後、メモリセルにおける分離酸化膜6を所定の膜厚だけエッチングする。基板1全面にONO膜を形成し、メモリセルを覆う第2レジストパターンを形成した後、周辺回路におけるONO膜とポリシリコン膜8とシリコン酸化膜7とを除去する。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】パターンの解像度よりもチャネル長を短くすることが容易で、これにより低コストで取り扱い電流量を増加させることが可能な薄膜トランジスタを提供する。

【解決手段】基板3上に、ゲート電極5、これを覆うゲート絶縁膜7、このゲート絶縁膜7を介してゲート電極5を覆うチャネル層(チャネル部半導体薄膜)11がこの順またはこれと逆の順に積層され、チャネル層11の表面側と裏面側とに、ソース電極9とドレイン電極15とが分け置かれていることを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】 高耐圧、低耐圧トランジスタを同一基板に備える半導体装置の、高耐圧トランジスタ領域の面積の削減を図る装置及び方法の提供。

【解決手段】 支持基板10a上の絶縁層10b上に形成された第1半導体層10cと、前記第1半導体層10c内に形成された第1高耐圧トランジスタ100Pと、前記絶縁層上に形成された第2半導体層内に形成された第2高耐圧トランジスタ100Nと、第1半導体層と第2半導体層との間に設けられた絶縁層10bに到達する深さを有する第1素子分離領域110aと、前記絶縁層10b上に形成された第3半導体層内の第1低耐圧トランジスタ200Nと、前記第3半導体層内に形成された第2低耐圧トランジスタ200Pと、前記第3半導体層内に形成され、かつ、前記第1低耐圧トランジスタ200Nと前記第2低耐圧トランジスタ200Pとの間に設けられた、前記絶縁層10bに到達しない深さを有する第2素子分離領域とを含む。

(もっと読む)

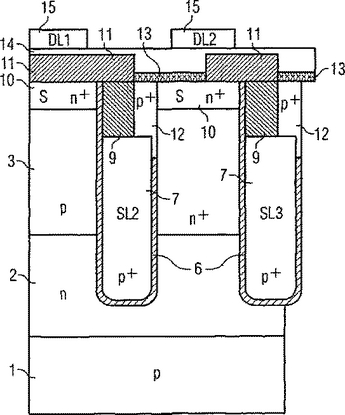

ビット線構造およびその製造方法

本発明は、表面ビット線(DLx)および埋め込みビット線(SLx)を備えたビット線構造に関するものである。これに関して、埋め込みビット線(SLx)は、トレンチ絶縁層(6)を備えたトレンチに形成されており、トレンチの上部に設けられた被覆接続層(12)と自動調心電極層(13)とを介して形成された接触部とともに、ドープ領域(10)に接続されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 遷移金属化合物膜を含むゲート絶縁膜を有する半導体装置のリーク電流及び閾値電圧のシフトを抑制する。

【解決手段】 半導体装置は、高誘電率材料である遷移金属化合物膜からなるゲート絶縁膜104と、n型又はp型のドーパントを含み且つ多結晶シリコン又はシリコン化合物からなるゲート電極105とを備え、ゲート絶縁膜104に含まれる炭素及びハロゲン元素の総量が0.1atomic%以下となっている。このような純度の膜は、遷移金属をターゲットとするスパッタ法によって成膜することによって実現でき、特に、純度が99.999atomic%以上の遷移金属をターゲットとして用いると確実に実現できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 セルフアライン形成技術によりセルフアライン形成領域の絶縁膜に形成されたコンタクトホールの径に比較してさらに開孔幅の大きな穴部を絶縁膜の上部に形成するためセルフアライン形成領域を再度エッチング処理する必要があったとしても、セルフアライン形成領域内のセルフアラインマスク膜に悪影響が及ぼされることなく、さらにセルフアライン形成領域に対して複数回に分けて接続配線を埋込み形成する必要をなくす。

【解決手段】 領域CB2に対して第1のコンタクトホール16を形成した後、フォトレジスト38、塗布型酸化膜39、フォトレジスト40の3層構造の多層レジスト構造41を形成し、第5のシリコン酸化膜23の上部に穴部24および25を形成する。

(もっと読む)

ナノクラスタ電荷蓄積デバイスの形成方法

一実施形態では、ナノクラスタ電荷蓄積デバイスを形成する方法が提供される。半導体装置(10)の第1の領域(26および30)が1つまたは複数の非電荷蓄積デバイスを配置するために特定される。この半導体装置の第2の領域(28)が1つまたは複数の電荷蓄積デバイスを配置するために特定される。この1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物(22)がこの半導体装置の第1の領域(26および30)中に形成され、引き続きナノクラスタ電荷蓄積層がこの半導体装置の第2の領域(28)中に形成される。  (もっと読む)

(もっと読む)

2,861 - 2,880 / 2,965

[ Back to top ]