Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,801 - 2,820 / 2,965

膜スタックをエッチングするための方法およびシステム

膜スタックを設け、複数のドライ・エッチング・プロセスを用いてこの膜スタック中にフィーチャを形成するための方法およびシステムが記載される。膜スタック中に形成されたフィーチャは、約25nm以下の限界寸法を有するゲート構造を含み得る。この限界寸法は、4つのマスク層を用いてポリシリコン層中に形成できる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

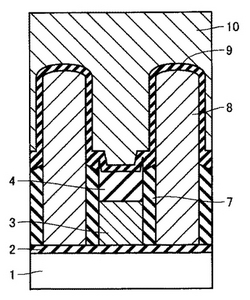

【課題】 複数のコントロールゲート電極間のショートが抑制された半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、アシストゲート電極3および窒化シリコン膜4を形成する工程と、アシストゲート電極3および窒化シリコン膜4の側壁上にアシストゲート電極3および窒化シリコン膜4よりも上方に突出するサイドウォール絶縁膜7を形成する工程と、サイドウォール絶縁膜7上にフローティングゲート電極8となるポリシリコン層を形成する工程と、半導体基板1の主表面に向かって厚みが徐々に増加するように窒化シリコン膜4より上方にサイドウォール絶縁膜7を残存させながらサイドウォール絶縁膜7をエッチングする工程と、窒化シリコン膜4よりも上方に位置する部分に残存したサイドウォール絶縁膜7を除去する工程と、フローティングゲート電極8上にONO膜9およびコントロールゲート電極10を形成する工程とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】 プラズマ処理によりシリコン表面に形成される、SiCを含む変質層を、シリコン表面の侵食を最小限に抑止しながら除去する。

【解決手段】 前記変質層を、酸素ラジカルに、前記半導体表面のSi原子に結合してSi原子と酸素原子との間の二重結合の形成を阻害するような元素の活性種を添加して改質し、形成された改質層をウェットエッチングにより除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装装置を構成する半導体素子の微細化にともない、電極の間の距離も縮小され、電極の間に設ける層間絶縁膜の中にボイドが発生していた。このボイドは、半導体装置の信頼性を悪化するため、大きな問題であった。

【解決手段】半導体基板11の上部に絶縁膜21を設け、この上部に第1の導電性材料14と第2の導電性材料15とを積層して設ける。絶縁性を有する被服層16を第1の導電性材料14の側端部に設け、これらにより電極10を構成する。第2の導電性材料15の側端部は、第1の導電性材料14の側端部より内側に設け、第1の導電性材料14と第2の導電性材料15とが接する面積は、第1の導電性材料14の上面部の面積よりも小さい。

(もっと読む)

CMOSデバイスのソースおよびドレインの寄生抵抗低減

ドープされた半導体基板を与えることと、pn接合部を画定するべく基板に第二ドーパントを導入することと、pn接合部に対応する容量を低減するべくpn接合部付近の基板中に中性化種を導入することとを含む、半導体系デバイスを製造するための方法である。半導体系デバイスは、第一および第二ドーパントを有する半導体基板と、中性化種とを含む。第一および第二ドーパントはpn接合部を画定し、中性化種は、pn接合部に対応する容量を低減するべくpn接合部付近の第一ドーパントの一部を中性化する。 (もっと読む)

半導体装置

【課題】直接トンネル電流が流れる程度に薄膜化されたゲート絶縁膜におけるゲート電極からのドーパント原子の基板への拡散を防止すると共に、ゲートリーク電流を低減できるようにする。

【解決手段】第1の素子形成領域51及び第2の素子形成領域52に区画された半導体基板11上に、酸化膜からなる第1のゲート絶縁膜13Aを形成する。次に、第1のゲート絶縁膜13Aの第2の素子形成領域52に含まれる部分を除去し、半導体基板11に対して酸窒化性雰囲気で熱処理を行なうことにより、第2の素子形成領域52上に膜厚が第1のゲート絶縁膜13Aよりも小さい酸窒化膜からなる第2のゲート絶縁膜15Bを形成する。次に、第1のゲート絶縁膜13B及び第2のゲート絶縁膜15Bを窒素プラズマに暴露することにより、窒素原子をさらに導入された第1のゲート絶縁膜13C及び第2のゲート絶縁膜15Cを形成する。

(もっと読む)

ゲート・スタックをエッチングするための方法およびシステム

調整可能耐エッチング性反射防止(TERA:tunable etch resistant anti−reflective)コーティングをエッチングするための方法およびシステムが記載される。TERAコーティングは、例えば、リソグラフィ構造を補完するためのハード・マスクまたは反射防止コーティングとして利用できる。TERAコーティングは、構造式R:C:H:Xを有することができ、式中、Rは、Si、Ge、B、Sn、Fe、Ti、およびそれらの組み合わせのうちの少なくとも1つを含む群から選ばれ、Xは、存在しないかまたはO、N、S、およびFのうちの1つ以上を含む群から選ばれる。膜スタック中の構造の形成の間、パターンが、SF6ベースのエッチング化学的性質を有するドライ・プラズマ・エッチングを用いてTERAコーティングに転写される。 (もっと読む)

半導体装置

【課題】素子サイズの削減が可能な半導体装置を提供すること。

【解決手段】N+型炭化珪素から構成される基板領域1上に形成した炭化珪素半導体基体内において、N−型のドレイン領域2がP型のベース領域3を介してN+型のソース領域4と接し、ドレイン領域2およびソース領域4に絶縁膜5を介して接するゲート電極6と、ドレイン領域2に基板領域1を介して接続するドレイン電極8と、ソース領域4に接続するソース電極7とが設けられ、ソース電極4に接続されドレイン領域2とショットキー接合100を形成するショットキー接合領域9が設けられ、ソース電極7からベース領域3を介してドレイン領域2に流れる電流を阻止するショットキー接合120がソース電極7とベース領域3との間に設けられていることを特徴とする半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ボディコンタクトを有するSOIデバイスにおいて、ボディコンタクトとボディ領域との間に所望の抵抗値を持たせると共に、当該抵抗値のばらつきを抑制する。

【解決手段】SOI層3におけるコンタクト61との接続部分(即ち、素子分離絶縁膜41の下)に、不純物濃度の高いP+領域を形成せずに、SOI層3とボディコンタクト61とをショットキー接合させる。また、ボディコンタクト61の表面にはバリアメタル61aが形成されており、ボディコンタクト61とSOI層3との間に、バリアメタル61aとSOI層3とが反応したシリサイド70が形成される。

(もっと読む)

ニッケル−シリコン化合物の形成方法

【課題】 工程の増加を招くことなく、Si上に高温安定性の高いNiシリサイドを短時間で形成することができ、トランジスタ特性向上に寄与する。

【解決手段】 シリコン基板上にNi膜を形成した後、最終アニール温度THを800℃としたアニール処理を施してNiシリサイド膜を形成する方法であって、アニール温度をステップ的に変えることのできるアニール装置を用い、基板を400℃近傍の第1のステップ温度まで昇温した後にこの温度で一定時間アニールし、次いで基板を600℃近傍の第2のステップ温度まで昇温した後にこの温度で一定時間アニールし、次いで基板を700℃近傍の第3のステップ温度まで昇温した後にこの温度で一定時間アニールし、次いで700℃近傍の温度から800℃までは、アニール温度を50℃以内でステップ的に上げると共に各ステップで一定時間アニールする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 側壁絶縁膜の形成などのプロセスにおけるチャージングによるダメージを抑制する。

【解決手段】 不揮発性半導体記憶装置のメモリセルアレイ形成領域に複数のワード線を形成するための第1の導電膜と半導体装置形成領域に第2の導電膜を形成する。次に、第1のドライエッチングによってメモリセルアレイ形成領域におけるワード線が互いに離間して配置されるように、第1の導電膜に開口部を形成した後、開口部にワード線の側壁絶縁膜を形成する。次に、ウェットエッチングによって側壁絶縁膜におけるワード線の端部近傍領域に存在する部分を除去する。次に、第2のドライエッチングによって第1の導電膜におけるワード線の端部近傍領域に存在する部分を除去する。第1の導電膜における開口部の形成は、第1の導電膜における開口部形成後の残存部分が、メモリセルアレイ形成領域の外部領域に位置する半導体基板中の活性領域上にて、活性領域と電気的に接続されるように形成された第2の導電膜と接続されるように行なわれる。

(もっと読む)

半導体デバイスの形成方法およびその構造

一実施形態では、半導体デバイス(10)の形成方法が示される。半導体基板(11)は、第1の部分(14または16)および第2の部分(18または20)を有する。第1の誘電体層(24または26)は半導体基板の第1の部分の上に形成され、第2の誘電体層(30)は半導体基板の第2の部分の上に形成される。ポリシリコンなどのシリコンを含み得るキャップ(28)は第1の誘電体層の上に形成される。第1の電極層(40)はキャップの上に形成され、第2の電極層(32,36または40)は第2の誘電体の上に形成される。  (もっと読む)

(もっと読む)

温度評価方法及びそれを用いた半導体装置の製造方法

【課題】 高融点金属とシリコン基板中のシリコンとを熱処理により反応させてシリサイド層を形成する際のシリコン基板の温度を非破壊の測定方法により正確に評価する。

【解決手段】 シリコン基板101の上に高融点金属膜107を形成した後、非破壊測定方法を用いて高融点金属膜107の膜厚を測定する。高融点金属膜107が形成されたシリコン基板101に対して熱処理を行なって、シリコン基板101の上にシリサイド膜108を形成する。第2の非破壊測定方法を用いてシリサイド膜108の膜厚を測定した後、高融点金属膜107の測定膜厚と、シリサイド膜108の測定膜厚とに基づいて、熱処理中のシリコン基板101の温度を算出する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電気抵抗化および高信頼性化可能なコンタクトを備え、高速伝送が可能で信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 コンタクト20、23を、CVD法を用いて、シリサイド膜19、22、シリコン窒化膜15aおよび第1層間絶縁膜15bの内壁に接する表面に、表面からコンタクト内部方向への距離に応じて窒素含有量が減少する組成勾配を有する窒化タングステン部24を形成し、その内側にタングステンが充填されたタングステン部25を形成する。窒化タングステン部24とタングステン部25との界面の酸化や汚染を防止する。

(もっと読む)

半導体装置の製造方法

【課題】裏面電極工程のウェハの反りを抑制して、ウェハの割れやキズの発生率を低下させることで、良好なデバイス特性と低コスト化を達成できる半導体装置の製造方法を提供する。

【解決手段】図1(d)の工程において、100μm厚みのウェハ1のp型コレクタ層4上に、アルミニウム(Al)膜5a、チタン(Ti)膜5b、ニッケル(Ni)膜5c、金(Au)膜5dなどの金属膜を組合わせて裏面電極5をスパッタ法を用いて形成する場合に、ウェハ1の温度を110℃から150℃とすることで、ウェハ1の反り量を4mm程度に抑制できて、ウェハ1の割れやキズの不良率が低減し、良好なデバイス特性と低コスト化を図ることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リーク電流を低減することができる半導体装置及びその製造方法を提供すること

【解決手段】半導体装置1aは、素子分離領域RXによって囲まれた素子領域RYを有する基板10と、その素子領域RY中に形成されたソース/ドレイン61、62と、そのソース/ドレイン61、62間の領域の上にゲート絶縁膜30を介して形成された第1ゲート電極41と、素子領域RYと素子分離領域RXの境界Bの少なくとも一部を覆うように、ゲート絶縁膜30上に形成された第2ゲート電極42とを備える。第1ゲート電極41と第2ゲート電極42は分離している。

(もっと読む)

半導体装置及びその製造方法

【課題】同一の半導体基板上に、2種類以上のゲート絶縁膜及びゲート電極を有するMIS型トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板11の第1のNMISトランジスタ形成領域AreaAには、ハフニウム酸化膜のような金属酸化膜からなるゲート絶縁膜21aとタングステン膜のような金属膜からなるゲート電極22aを有する第1のNMISトランジスタを形成する。また、半導体基板11の第2のNMISトランジスタ形成領域AreaCには、シリコン酸化膜からなるゲート絶縁膜13とポリシリコン膜のような半導体材料からなるゲート電極14cを有する第2のNMISトランジスタを形成する。ゲート電極22aは、ゲート電極14cと同時に形成した第1のダミーゲート電極14aを除去して設けられたゲート電極形成用開口20a内に金属膜を埋め込んで形成されたダマシン構造を有する。

(もっと読む)

半導体装置

【課題】 原子レベルで平坦な界面をもって基板上に堆積され、しかも低抵抗のシリサイド層を有する半導体装置を提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成された拡散領域と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記拡散領域上に形成されたシリサイド層(3)とを具備するMISトランジスタを含む半導体装置である。前記シリサイド層は、前記半導体基板との界面にEr、Gd、Tb、Dy、Ho、Tm、Yb、Lu、およびPtからなる群から選択される少なくとも1種の金属のシリサイドからなる界面層(5)を有することを特徴とする。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】 高い信頼性を有する半導体素子を提供する。

【解決手段】

ドリフト領域11の表面領域にはベース領域13が形成され、ベース領域13の表面領域にはソース電極14が形成され、ドリフト領域11上には、酸化膜20、ゲート電極30、及び、層間絶縁膜40が形成されている。ソース領域14、酸化膜20、及び、層間絶縁膜40には、層間絶縁膜40上のソース電極50とベース領域13及びソース領域14とを接続するためのソース開孔50aが形成されている。酸化膜20は、ゲート電極30下の厚い第1酸化膜と、ソース開孔50aの外縁から延伸する薄い第2酸化膜と、第1酸化膜と第2酸化膜との間に配置され、第1酸化膜と第2酸化膜との中間の厚さを有する第3酸化膜と、から構成される。これにより、酸化膜20の厚さは、ソース開孔50aの外縁からゲート電極30に向かって階段状に増加する。

(もっと読む)

半導体基板内の分離溝に隣接するコンタクト用開口の形成方法

【課題】フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法を提供する。

【解決手段】トレンチ形成・埋め込み法によって半導体基板の中にフィールド分離マスを形成し、該フィールド分離マスに隣接した基板上に基板マスキング層を形成する工程であって、前記フィールド分離マスの上面はエッチングストップキャップによって覆われ、その側壁は前記マスキング層によって覆われる工程と、前記分離マス側壁の少なくとも一部を露出するために、分離マスから分けて前記基板マスキング層を除去する工程と、露出した分離マス側壁上にエッチングストップカバーを形成する工程と、前記分離マス及び該分離マスに隣接する基板領域上に絶縁層を形成する工程と、前記分離マスエッチングストップキャップ及びカバーに対して選択的に、前記分離マスに隣接する前記絶縁層を貫通するコンタクト用開口をエッチング開口する工程とからなる、フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法。

(もっと読む)

2,801 - 2,820 / 2,965

[ Back to top ]