Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,881 - 2,900 / 2,965

固体撮像素子の製造方法および固体撮像素子

【課題】 単層電極構造の電荷転送電極を形成するに際し、第2層導電性膜の平坦化工程に起因する膜減りを防止し、均一な膜厚の電荷転送電極を形成することにより電荷転送効率の改善を図る。

【解決手段】 ゲート酸化膜の形成された半導体基板表面に、第1の電極を構成する第1層導電性膜のパターンを形成する工程と、前記第1の電極の少なくとも側壁に電極間絶縁膜となる絶縁膜を形成する工程と、前記第1の電極および前記電極間絶縁膜の形成された前記半導体基板表面に第2の電極を構成する第2層導電性膜を形成する工程と、少なくとも前記第1の電極上の前記第2層導電性膜を除去し、平坦化する工程とを含み、前記平坦化する工程に先立ち、前記第2層導電性膜の上層の一部に除去抑制層を形成する工程を含む。

(もっと読む)

High−k誘電材料をエッチングするための方法及びシステム

【課題】high−k(高誘電率)誘電材料をエッチングするための方法及びシステム

【解決手段】本発明のある実施形態では、エッチ反応剤が、high−k層と反応したときに揮発性エッチ製品を形成するために利用される。代わりに、high−k層はパターン化されたフォトレジストまたはハードマスクに従って異方エッチングすることができ、中性原子のハイパーサーマルビームがhigh−k層とのエッチ反応剤の反応を助けるために使用される。代わりに、中性原子のハイパーサーマルビームまたはプラズマ処理はhigh−k層を修正し、その後、該修正されたhigh−k層と反応するエッチ反応剤を活用して該修正されたhigh−k層をエッチングするために使用することができる。

(もっと読む)

半導体装置の製造方法

【課題】 寄生容量の増加を抑制しつつ、所望のゲート耐圧を有するパワーMISFETを製造できる技術を提供する。

【解決手段】 基板上に多結晶シリコン膜を堆積し、その多結晶シリコン膜で溝部7、8を埋め込んだ後、その多結晶シリコン膜をパターニングすることにより、活性セル領域においては溝部7内にてゲート電極11を形成し、ゲート配線領域においては溝部8内を埋め込み、一部が溝部8内から連続して溝部8の外部に延在し、ゲート電極11と電気的に接続するゲート引き出し電極12を形成し、溝部8外のゲート引き出し電極12には、ゲート引き出し電極12の端部から延在するスリット14を形成する。その後、基板上に酸化シリコン膜19およびBPSG膜20を堆積する。

(もっと読む)

シリコンゲルマニウム犠牲層を用いた半導体素子の微細パターンの形成方法及びそのパターンの形成方法を用いた自己整列コンタクトの形成方法

【課題】 シリコンゲルマニウム犠牲層を使用して半導体素子の微細パターンを形成する方法、及びそれを用いた自己整列コンタクトを形成する方法を提供する。

【解決手段】 基板上に導電性物質膜、ハードマスク膜及び側壁スペーサを含む導電ライン構造物を形成し、基板の全面に少なくとも導電ライン構造物の高さと同じであるか、またはそれ以上の高さにシリコンゲルマニウム(Si1−XGeX)犠牲層を形成し、犠牲層上にコンタクトホールを限定するフォトレジストパターンを形成した後、犠牲層を乾式エッチングすることで基板を露出させるコンタクトホールを形成し、ポリシリコンを使用してコンタクトホールを埋め込む複数のコンタクトを形成した後に残留する犠牲層を湿式エッチングした後、その領域にシリコン酸化物を満たして第1層間絶縁層を形成する半導体素子の自己整列コンタクトの形成方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 第1層配線と、拡散層あるいはゲート電極との層間容量を抑えつつ、拡散層あるいはゲート電極に確実に接続するコンタクトプラグを形成する。

【解決手段】 基板上方に形成されたゲート電極と、ゲート電極の両側に形成された拡散層とを有する半導体装置において、一端において、ゲート電極の上面に接し、かつ、他端が、ゲート電極上面よりも、基板に近い位置に伸びる導電体膜を形成する。そして、基板上に、ゲート電極と、導電体膜とを埋め込む層間絶縁膜を形成し、この層間絶縁膜を貫通し、導電体膜の、ゲート電極上面よりも基板に近い位置において、導電体膜に接続する第プラグを形成する。

(もっと読む)

線幅の狭い半導体素子の製造方法

【課題】セルの周辺領域における線状パターンのCDを減少させることができる半導体素子の製造方法を提供する。

【解決手段】セル領域及び周辺領域が画定された基板200上にシリコン窒化膜201Aを形成する工程、シリコン窒化膜上に反射防止膜としてシリコン酸窒化膜202Aを形成する工程、セル領域では最終パターンの線幅W1Aより広い幅W1を有し、周辺領域ではパターンの崩れの発生を抑える最小の線幅W2を有するようにシリコン酸窒化膜上にフォトレジストパターン203を形成する工程、フォトレジストパターンをエッチングマスクとしてシリコン酸窒化膜とシリコン窒化膜とをエッチングする処理を、残留するシリコン酸窒化膜202Bとシリコン窒化膜201Bとの線幅W1A,W2Bがフォトレジストパターンの線幅W1,W2に比べて狭くなるまで行う工程、及び残留するシリコン窒化膜を過度エッチングする工程を含む。

(もっと読む)

半導体装置

【課題】デュアルゲート構造を有するMIS型トランジスタにおいて、デュアルゲートにおけるシリサイド部分の断線に起因する遅延の劣化を防止して、動作不良を防止できるようにする。

【解決手段】 半導体装置は、上部がシリサイド化されたゲート電極22を有するP型MOSトランジスタ100及びN型MOSトランジスタ200を備え、ゲート電極22におけるP型MOSトランジスタ100部分は、P型不純物が導入されたポリシリコンを含み、そのN型MOSトランジスタ200部分は、N型不純物が導入されたポリシリコンを含む。P型MOSトランジスタ100及びN型MOSトランジスタ200の互いのドレインは、シリサイド化されたポリシリコンを含む共有配線23により接続されている。共有配線23の線幅は、ゲート電極22の線幅よりも大きくなるように設定されている。

(もっと読む)

半導体装置および電子機器

【課題】 半導体集積回路において、今後のさらなるゲート電極の微細化を進める技術を提供することを課題とする。

【解決手段】 本発明は、レジストマスクをエッチングにより後退させて導電膜のエッチングを行い、ゲート配線の断面形状は上層配線とコンタクト可能な幅を有する台形とし、且つ、ゲート配線から分岐するゲート電極の断面形状を意図的に3つの内角をもつ形状、代表的には三角形状として1μm以下のゲート幅を実現する。本発明により、オン電流の増大が実現し、高速動作する回路(代表的にはCMOS回路やNMOS回路)を得ることができる。

(もっと読む)

ナノワイヤによってコンタクトがとられる導電性材料の層を有する電子装置を製造する方法

本発明による電子装置(100)は、第1値と第2値との間で電気的にスイッチ可能な電気抵抗率を有するメモリ材料の層(107)を備える。メモリ材料は相変化材料でもよい。電子装置(100)は電子装置の第1端子(172)とメモリ材料の層(107)を電気的に接続する一組のナノワイヤ(NW)をさらに備え、それによって、第1端子からナノワイヤ(NW)及びメモリ材料の層(107)を介して電子装置の第2端子(272)への電流の伝導を可能にする。各ナノワイヤ(NW)は各々のコンタクト領域でメモリ材料の層(107)に電気的にコンタクトがとられる。全てのコンタクト領域ほぼ同一である。本発明による方法は、本発明による電子装置(100)を製造するのに適している。  (もっと読む)

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置において、セル面積の縮小化を図ることにある。

【解決手段】 半導体装置100は、半導体基板10と、半導体基板10の内部に形成され、コントロールゲートとして機能する不純物領域22と、半導体基板10の上方に形成されたゲート絶縁層16と、ゲート絶縁層16の上方に、不純物領域22とオーバーラップして形成されたフローティングゲート18と、フローティングゲート18の上方に形成された層間絶縁層50と、層間絶縁層50の上方に、フローティングゲート18とオーバーラップして形成された遮光層52と、を含む。遮光層52は、不純物領域22と電気的に接続している。

(もっと読む)

半導体装置およびその作製方法

【課題】 高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】 ゲート電極106と異なる層に走査線102を形成し、容量配線107が信号線109と平行になるよう配置する。各画素はそれぞれ独立した容量配線107に誘電体を介して接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

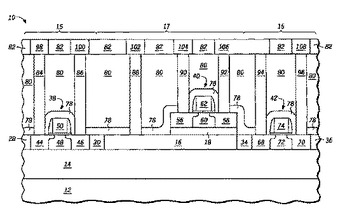

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

半導体装置

【課題】 オン抵抗を低減でき、リーク電流も抑制できる半導体装置。

【解決手段】 半導体装置は、所定間隔を隔てて略平行に配置される複数のトレンチ1と、これらトレンチ1の内部に絶縁層2を介して形成される複数のソース3と、トレンチ1の上部に形成されるソース金属層4と、隣接するトレンチ1の間に形成されるn-半導体領域5と、トレンチ1の下部に形成されるn型ドリフト層6と、n型ドリフト層6の下部に形成されるn+基板7と、n+基板7の下面に形成されるドレイン金属層8とを備えている。トレンチ1内のソース3はp型ポリシリコンで形成されている。ソース3はソース金属層4と接触している。n-半導体領域5とソース金属層4とはショットキー接合されている。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】 不純物のプロファイルを精度よく制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体領域1に不純物元素のイオンを注入する工程と、半導体領域に、所定元素としてIV族の元素又は不純物元素と同一導電型であって不純物元素よりも質量数が大きい元素のイオンを注入してアモルファス状態の結晶欠陥領域5を形成する工程と、不純物元素及び所定元素が注入された領域にフラッシュランプの光を照射してアニールを行い、アモルファス状態の結晶欠陥領域の結晶欠陥を回復させるとともに不純物元素を活性化する工程と、を備え、フラッシュランプの光を照射してアニールを行う工程を、結晶欠陥領域のアモルファス状態が維持される温度で半導体領域を予め加熱した状態で行う。

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

2,881 - 2,900 / 2,965

[ Back to top ]