Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,901 - 2,920 / 2,965

基板への相互接続を有する集積回路およびその製造方法

ソース/ドレイン(20)とゲート(26)との間の接点(32)が、ゲート誘電体(46)の選択部分(35)へ埋設物を注入することによりゲート誘電体(46)の選択部分(35)を導電性にすることで行われる。ゲート材料は集積回路全体(10)の上の層に位置する。ゲート(26)がソース/ドレイン(20)に接続する領域(32)が識別され、この識別位置(35)においてゲート誘電体(46)が導電性となるよう埋設物が注入される。ソース/ドレイン(20)が導電性ゲート誘電体(35)のそのような導電性領域の下を延び、該位置で埋設物が注入されたゲート誘電体(35)がゲート(26)をソース/ドレイン(20)に短絡するように、ソース/ドレイン(20)は形成される。これによって集積回路(10)上のスペースが節約され、相互接続層の必要性が低減され、露出したシリコン基板上にポリシリコンを堆積およびエッチングさせることに付随する問題を回避することができる。  (もっと読む)

(もっと読む)

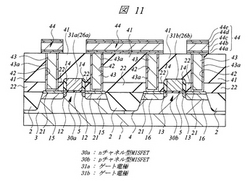

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 リーク電流の少ない半導体装置を提供する。

【解決手段】 半導体装置は、第1導電型を有する半導体基板1を含む。第2導電型を有する1対のソース/ドレイン領域4が半導体基板の表面に形成される。ゲート絶縁膜3がソース/ドレイン領域相互間のチャネル領域上に配設される。第1導電型を有するゲート電極5がゲート絶縁膜上に配設される。ゲート電極は、チャネル領域の上方に位置する第1部分5aと、ソース/ドレイン領域の上方に位置する第2部分5bとを有する。第2部分の多数キャリア濃度は第1部分の多数キャリア濃度より低い。

(もっと読む)

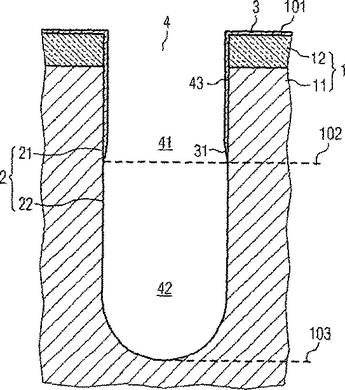

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 Bモード故障とシリサイド未形成による動作不良の双方を解消した半導体装置を提供する。

【解決手段】 素子分離領域により画成された第1および第2の素子領域を有する基板と、前記第1の素子領域に形成された第1のポリシリコンゲート電極を有する第1の電界効果トランジスタと、前記第2の素子領域に形成された第2のポリシリコンゲート電極を有する第2の電界効果トランジスタと、前記第1のポリシリコンゲート電極と前記第2のポリシリコンゲート電極とを結んで前記素子分離領域上を延在するポリシリコンパターンと、前記第1のポリシリコンゲート電極の表面および前記第2のポリシリコンゲート電極の表面、さらに前記ポリシリコンパターンの表面に形成され、前記第1のポリシリコンゲート電極から前記第2のポリシリコンゲート電極まで、前記ポリシリコンパターン上を延在するシリサイド層とよりなる半導体装置において、前記シリサイド層は前記ポリシリコンパターン上において層厚が増大した厚膜部を含み、前記厚膜部では、前記シリサイド層の表面が上方に突出する。

(もっと読む)

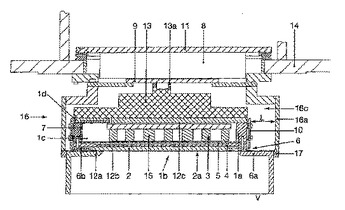

可動な平らなターゲットを用いて材料を飛散させるための装置及び方法

真空室内で材料を飛散させる装置であって、−平面内で可動な、平らでかつカソードとして接続可能な少なくとも1つのターゲットを有するターゲット装置を有し、

定置のターゲット環境と、ターゲット装置に対応配置された駆動装置と、ターゲット

に対応配置された少なくとも1つのアノードを有するアノード装置と、

ターゲットの飛散表面からの材料の遊離を助けるための磁場を発生させるための磁気

装置と

を備えている形式のものにおいて、少なくとも1つの非回転対称的な有利には方形のターゲットプレートとして構成されたターゲットが設けられ、該ターゲットがターゲット装置で−平面内で可動であることが提案されている。さらに本発明は材料を飛散させる方法にも関する。  (もっと読む)

(もっと読む)

金属ゲート集積化のためのゲートスタック及びゲートスタックのエッチングシーケンス

【課題】本発明は半導体デバイス(205)における金属ゲートスタック(200)を製作するためのプロセスを提供する。

【解決手段】本願の方法は、半導体基板(220)上に位置するゲート誘電体層(215)の上に金属層(210)を堆積させる段階を含む。本方法は、金属層(210)上にポリシリコン層(225)を形成する段階と、そのポリシリコン層(225)上に保護層(230)を生成する段階とを更に含む。本方法はは、また、保護層(230)上に無機反射防止被覆(235)を配置する段階を含む。他の実施形態では、金属ゲートスタックの前駆構造体及び集積回路の製造方法を含む。

(もっと読む)

シリサイド層を有する半導体素子の製造方法

半導体素子を形成する方法では、半導体基板を設け、絶縁層を半導体基板の上に形成し、導電層を絶縁層の上に形成し、第1金属シリサイド層を導電層の上に形成し、導電層をパターニングして、制御電極の一部分であるパターニング済み第1層を形成し、第1金属シリサイド層をパターニングしてパターニング済み第1金属シリサイド層を制御電極の上に形成してパターニング済み第1金属シリサイド層が制御電極の上に残るようにし、そして第2金属シリサイド層をパターニング済み金属シリサイド層の上に形成し、第2金属シリサイド層は第1金属シリサイド層の膜厚よりも厚い膜厚を有する。  (もっと読む)

(もっと読む)

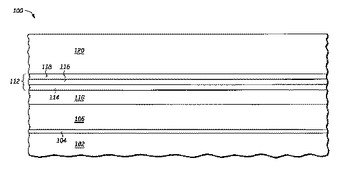

分離相補型マスクパターン転写方法

パターニング方法は、相補的なレチクルの組を個別に転写することを可能にする。一実施形態においては、例えば本方法では、位相シフトマスク(PSM)(112)をエッチングし、次にcPSMマスク(110)に対応するカットマスクをエッチングする。更に、分離相補型マスクパターン転写方法は2つの個別の、かつ分離されたマスクパターニング工程を含み、これらの工程では、像を最終ウェハパターニングの前に、複合パターンを、中間ハードマスク(112)に部分的に転写することにより形成する。中間ハードマスク材料(112)及び最終ハードマスク材料(110)は、像が最終エッチングプロセスの前に下層の基板(102)またはウェハに像が転写されることがないように選択される。  (もっと読む)

(もっと読む)

平面デュアルゲート半導体装置

デュアルゲート半導体装置の製造方法は、シリコン体(16)の第1の表面(14)の一部分上に第1のゲート(12)が形成された後であるが、前記第1の表面の反対側のシリコン体の第2の表面(44)上に第2のゲート(52)を形成する前に行われるソース及びドレインコンタクト領域(34,36)のシリサイド化を備える。第1のゲート(12)はソース及びドレインコンタクト領域がシリコンチャネル(18)に位置合わせされることを保証するマスクの働きをする。さらに、製造の早い段階でシリサイド化を行うことにより、第2のゲートの材料の選択が高温処理により制限されない。シリサイド化によるシリコン体の第2の表面での材料特性の違いがシリサイドのソースコンタクト領域とドレインコンタクト領域との間に前記第2のゲートを横方向に位置合わせされることを可能にすることが有利である。  (もっと読む)

(もっと読む)

高誘電率誘電材料への酸窒化シリコン層の形成

本発明の実施形態は、基板上に配置された誘電層上にキャッピング層を堆積するための方法を提供する。一例では、プロセスは、基板を堆積プロセスに曝して、この上に誘電層を形成するステップと、該基板をシリコン前駆体および酸化ガスの順次パルスに曝して、堆積プロセス中にシリコン含有層を該誘電層上に形成するステップと、該基板を窒化プロセスに曝して、この上にキャッピング層を形成するステップと、所定の時間該基板をアニーリングプロセスに曝すステップとを含む。該キャッピング層は約5Å以下の厚さを有していてもよい。一例では、該酸化ガスが、触媒を含有する水蒸気生成器によって処理された水素源ガスおよび酸素源ガスから生じた水蒸気を含有する。別の例では、該堆積、窒化およびアニーリングプロセスが同じプロセスチャンバで生じる。 (もっと読む)

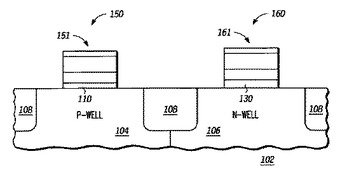

2種類の金属酸化物ゲート誘電体に1種類の金属ゲート電極が設けられる半導体プロセス及び集積回路

半導体形成プロセスでは、第1及び第2トランジスタを第1及び第2ウェル領域のそれぞれの上に形成し、第1トランジスタは第1ゲート誘電体を有し、そして第2トランジスタは第1ゲート誘電体とは異なる第2ゲート誘電体を有する。第1トランジスタは第1ゲート電極を有し、そして第2トランジスタは第2ゲート電極を有する。第1及び第2ゲート電極は組成が同じである。第1ゲート誘電体及び第2ゲート誘電体は共に、酸化ハフニウム及び酸化アルミニウムのような高k誘電体を含むことができる。第1及び第2ゲート電極は共に、ゲート電極層を該当するゲート誘電体の上に含む。ゲート電極層は、TaSiN及びTaCのいずれかであることが好ましい。第1及び第2ゲート電極は共に、導電層をゲート電極層の上に含むことができる。このような一の実施形態では、導電層はポリシリコン及びタングステンからなる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 小型化を図ることができる半導体装置を提供する。また、放熱効率を向上させた半導体装置を提供する。

【解決手段】 配線基板10の裏面にGND用外部配線12を形成する。そして、このGND用外部配線12に接続する複数のビア18を、配線基板10を貫通するように形成し、配線基板10の主面にHBTを含む高消費電力の第1の半導体チップ19を実装する。第1の半導体チップ19のエミッタバンプ電極19bは、第1の半導体チップ19内に形成された複数のHBTのエミッタ電極に共通接続しており、HBTが並んだ方向に延在している。第1の半導体チップ19は、この延在したエミッタバンプ電極19bに複数のビア18が接続するように配線基板10に実装されている。また、第1の半導体チップ19上に第1の半導体チップ19より発熱量の少ない第2の半導体チップ21を搭載して配線基板10の小型化を図る。

(もっと読む)

使い捨てスペーサを隆起ソース/ドレイン処理に取り入れた半導体デバイスの製造方法

半導体形成プロセスでは、ゲート電極(10)を基板(108)の上に形成する。第1シリコン窒化膜スペーサ(122)をゲート電極の側壁に隣接するように形成し、そして次に、使い捨てシリコン窒化膜スペーサ(130)をオフセットスペーサに隣接するように形成する。次に、使い捨てスペーサ(130)の境界によって画定される隆起ソース/ドレイン構造(132)をエピタキシャル成長により形成する。次に、使い捨てスペーサ(130)を除去して、ゲート電極(110)の近位に位置する基板を露出させ、そしてハロイオン注入(140)及びエクステンションイオン注入(142)のようなシャロージャンクションイオン注入を、ゲート電極の近位に位置する露出基板に行なう。取り替えスペーサ(136)を、使い捨てスペーサ(130)が形成されていた領域とほぼ同じ領域に形成し、そしてソース/ドレインイオン注入(140)を行なって、ソース/ドレイン不純物分布を隆起ソース/ドレイン(132)に形成する。ゲート電極(110)は被覆窒化シリコンキャップ層(144)を含むことができ、そして第1シリコン窒化膜スペーサ(122)はキャップ層(144)とコンタクトしてポリシリコンゲート電極(110)を窒化シリコンで取り囲むことができる。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

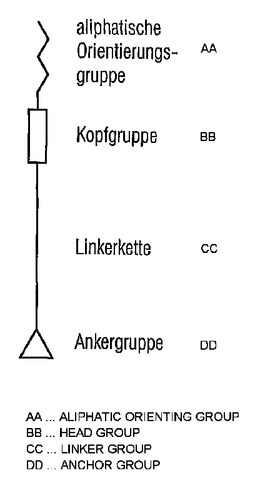

超薄膜誘電体、および、有機電界効果トランジスタでの超薄膜誘電体の使用

本発明は、基板、ソース電極、ドレイン電極、ゲート電極、および有機半導体材料を含む有機電界効果トランジスタに関するものである。このとき、誘電体層(ゲート誘電体)が、ゲート電極と半導体材料との間に配置されている。上記誘電体層は、アンカー基、リンカー基、頭部基、および脂肪族基を含んだ有機化合物の自己組織化単分子層からなる。アンカー基、リンカー基、頭部基、および脂肪族基は、この順にて互いに結合されている。  (もっと読む)

(もっと読む)

ゲート電極構造のトリミングを制御する方法

ゲート電極構造の第1寸法の決定によりゲート電極構造のトリミングをコントロールする方法および処理ツールであって、目標トリム寸法を選択し、プロセスパラメータのセットを生成するためにプロセスモデルに対して第1寸法および目標トリム寸法をフィードフォワードし、ゲート電極構造上にトリミングプロセスを実行する。トリミングプロセスを実行する際には、プロセスパラメータをコントロールし、ゲート電極構造をトリミングし、ゲート電極構造のトリム後の寸法を計測する。目標トリム寸法が得られるまで、トリミングプロセスは少なくとも1回は繰り返し行われる。トリム後寸法は、新たなプロセスパラメータのセットを生成するために、フィードバックされる。  (もっと読む)

(もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

デュアルドープポリシリコン及びシリコンゲルマニウムエッチング

【課題】

【解決手段】処理チャンバ内で、基板上に少なくとも一つのシリコンゲルマニウム層を有するスタックをエッチングする方法を提供する。シリコンゲルマニウムエッチングを提供する。エッチャントガスは、処理チャンバ内に提供され、エッチャントガスは、HBrと、不活性希釈剤と、O2及びN2の少なくとも一方とを含む。基板は、40℃未満の温度に冷却される。エッチャントガスは、シリコンゲルマニウム層をエッチングするために、プラズマに転換される。

(もっと読む)

2,901 - 2,920 / 2,965

[ Back to top ]