Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,941 - 2,960 / 2,965

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

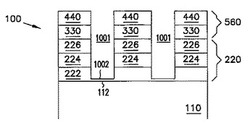

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

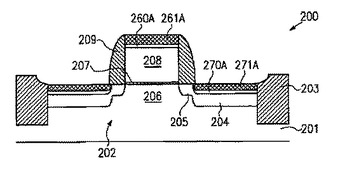

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【構成】自己整列リセス・ゲート構造及び形成方法が開示されている。最初に,絶縁用のフィールド酸化物領域を半導体基板内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。 (もっと読む)

high−kゲート誘電体プロセスインテグレーションのための界面酸化プロセス。

【課題】 high−kゲート誘電体プロセスインテグレーションのための界面酸化プロセスの提供。

【解決手段】 界面酸化層を有した微細構造物を形成する方法は、この微細構造物内のhigh−k層の形成と関係した基板の酸化特性を制御するように拡散フィルタ層を使用することにより提供される。拡散フィルタ層は、表面の酸化を制御する。界面酸化層は、拡散フィルタ層上へのhigh−k層の堆積の後に実行される酸化プロセス中に、または拡散フィルタ層上へのhigh−k層の堆積中に、形成されることができる。

(もっと読む)

液状又は溶液の原料を用いマルチチャンネル装置を介して不連続に射ち込み、単元又は多元の層及びスタック層を堆積する方法及び装置

【課題】 接触なしで原料を蒸発させて、単元又は多元の層及びスタック層を堆積する方法及び装置を提供する。

【解決手段】 本発明は、プロセスチャンバー(2)内で少なくとも1層を少なくとも1つの基板上に堆積する装置であって、複数の成分からなり、絶縁性、パッシベーション性、又は導電性を有する層と、インジェクタユニット(5)を用いて液状又は液体に溶解した原料(3)を温度制御された蒸発チャンバ(4)に不連続に射ち込むことによって成分が蒸発され、これらの蒸気がキャリアガス(7)によってプロセスチャンバーに供給される装置に関する。各インジェクターユニット(5)を通る流量の時間プロファイルを決定する、射出圧、射出周波数、及びデューティ比、並びにオン/オフの他のインジェクターユニットのオン/オフに対する位相関係等の流量パラメータが個別に設定又は変更されることが基本である。

(もっと読む)

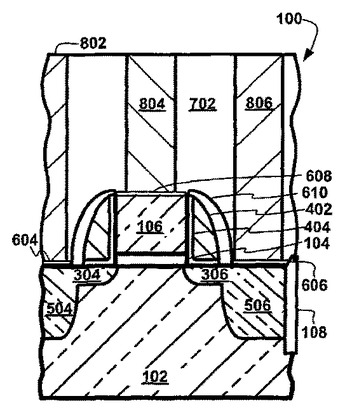

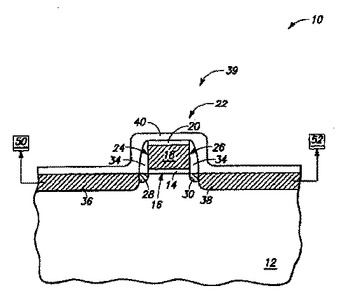

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

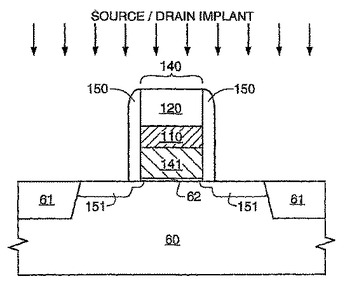

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

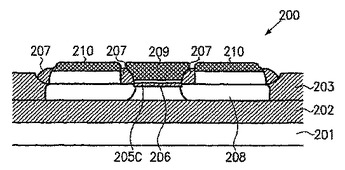

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

有機反射防止膜(ARC)を有する半導体装置及びその方法

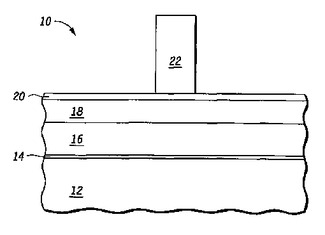

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

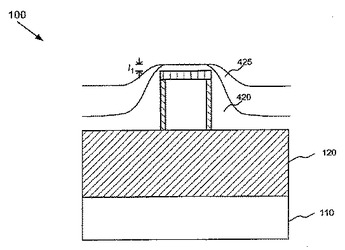

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

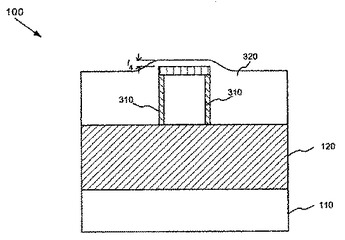

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

パンチスルー・ダイオードおよびそれを処理する方法

ショットキーのような動作を有するモノリシック集積パンチスルー・ダイオード。これは、ショットキー金属領域(16)が第1のpドープ・ウェル(9)の表面の少なくとも一部に堆積されるときに実現される。ショットキー金属領域(16)およびpドープ・ウェル(9)は、ショットキー・ダイオードの金属−半導体−遷移を形成する。順方向特性が0.5V未満の電圧降下を有するので、発明のPTダイオードの過電圧保護は改善される。  (もっと読む)

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

フリップチップFET素子

【課題】電力素子のオン状態抵抗、放熱特性、インダクタンスを改善する。

【解決手段】半導体素子は導電パッド領域26,36を含み、各々の導電パッド領域は複数の金属トレースに電気的に接続される。複数の金属トレースは各々が順番に拡散に接続される。はんだバンプやビアなどの導電接点素子は各々の導電パッド領域に取り付けられ、導体素子が第1のピッチを有する反復パターンに配列され得る。半導体素子は平行移動トレース50,60も含み、各々の平行移動トレースは2つ以上の導電接点素子に電気的に接続され得る。各々の平行移動トレースはそこに取り付けられる相互接続素子を有し得る。相互接続素子は第1のピッチより実質的に大きい第2のピッチを有する反復パターンに配列され得る。

(もっと読む)

2,941 - 2,960 / 2,965

[ Back to top ]