Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,921 - 2,940 / 2,965

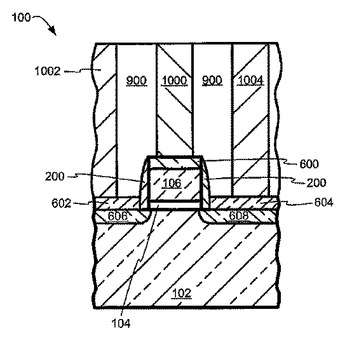

トレンチデバイスのための自動整合された接点構造体

【課題】オン時の電流を下げることなく、セルの実装密度を高める。

【解決手段】 トレンチタイプのパワー半導体デバイスを製造する方法であって、開口部を有するマスク層を半導体の表面に形成するステップを含んでいる。マスクの開口部を通し、半導体本体内に、ゲートを有するトレンチを形成する。次に、ゲートの頂部であって、かつマスク層の開口部内に絶縁プラグを形成する。次に、マスク層を除去し、半導体表面の上方に延びる絶縁プラグを残す。次に、トレンチ間にソース打ち込み領域を形成する。その後、絶縁プラグの側面に沿って、スペーサーを形成し、トレンチに隣接するソース打ち込み領域の部分をカバーする。次に、このスペーサーをマスクとして使用することにより、ソース打ち込み領域の露出部分をエッチングし、除去する。次に、スペーサーの下の残りのソース打ち込み領域を駆動し、ソース領域を形成する。その後、エッチングされた領域内に、浅い高導電タイプの接点領域を形成し、次に、デバイスの上にソースおよびドレイン接点を形成する。

(もっと読む)

半導体製造用のゲート電極ドーパント活性化方法

一実施形態において、本発明は、一般に、基板上に堆積されたドープされた層をアニールするための方法を提供する。この方法は、ゲート酸化物層のような基板の表面に多結晶層を堆積するステップと、この多結晶層にドーパントを注入して、ドープされた多結晶層を形成するステップとを備えている。この方法は、更に、ドープされた多結晶層を急速加熱アニールに露出して、多結晶層全体にわたりドーパントを容易に分配するステップを備えている。その後、この方法は、ドープされた多結晶層をレーザアニールに露出して、多結晶層の上部のドーパントを活性化するステップを備えている。レーザアニールは、ドーパント、即ち原子を多結晶材料の結晶格子へ合体させる。 (もっと読む)

窒化物半導体装置のオーム性電極構造

窒化物半導体を有する窒化物半導体装置のオーム性電極構造であって、窒化物半導体上に形成された第1の金属膜と、第1の金属膜上に形成された第2の金属膜とを有する。第1の金属膜は、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zrから成るグループの中から選ばれた少なくとも一つの材料で構成されている。第2の金属膜は、第1の金属膜102と異なる、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zr、Pt、Auから成るグループの中から選ばれた少なくとも一つの材料で構成されている。 (もっと読む)

半導体装置及び半導体装置の製造方法

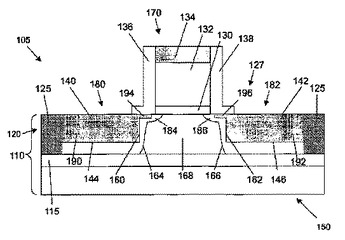

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

ドープされたゲート誘電体を有するトランジスタ

トランジスタおよびその製造方法。ゲート誘電体材料を堆積する前に半導体基材をドープする。別個のアニール工程、または、トランジスタを製造するために使用される後続のアニール工程の間を用いて、ドーパント種を、基材のドープされた領域から、ゲート誘電体内に出力拡散して、ドープされたゲート誘電体を生成する。ドーパント種は、ゲート誘電体の原子構造における各空孔を埋め、その結果、トランジスタの動作速度が上昇し、電力消費が低減され、電圧安定性が改善される。  (もっと読む)

(もっと読む)

バイポーラ接合トランジスタジオメトリ

【課題】

【解決手段】 バイポーラ接合トランジスタ(100)に関連する方法、装置、デバイスの実施例が記載されている。

(もっと読む)

集積回路技術における低応力の側壁スペーサ

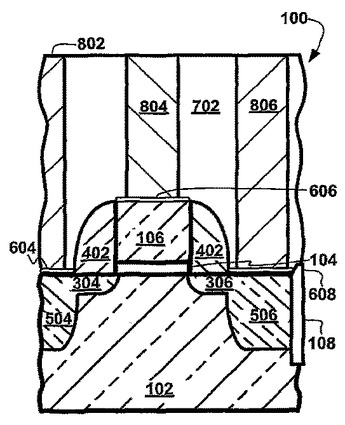

半導体基板(102)に集積回路の形成方法(900)を提供する。半導体基板(102)上にゲート絶縁膜(104)が形成され、このゲート絶縁膜(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(304)(306)が形成される。低出力プラズマ化学気相成長法プロセスを使用して、ゲート(106)の周りに側壁スペーサ(402)を形成する。ソース/ドレイン接合部(304)(306)およびゲート(106)に、シリサイド(604)(606)(608)を形成し、半導体基板(102)上に層間絶縁層(702)をたい積する。その後、層間絶縁層(702)中にシリサイド(604)(606)(608)へのコンタクト(802)(804)(806)が形成される。  (もっと読む)

(もっと読む)

III族窒化物電流制御デバイスおよび製造方法

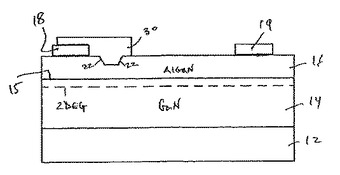

III族窒化物デバイスが、名目上オフ、すなわち、エンハンスメントモードのデバイスを作製するための凹部電極を含む。凹部電極を設けることによって、デバイス中の電流の流れを阻止するために、電極が非能動であるときに2つのIII族窒化物材料の境界面に形成された導電チャネルが中断される。電極はショットキー接点または絶縁金属接点であり得る。名目上オフの特性を有する整流器デバイスを形成するために、2つのオーム接点を設けることができる。電極が形成された凹部は傾斜側面を有することができる。電極は、デバイスの電流運搬電極と組み合わせて幾つもの幾何学配置で形成可能である。電極が凹部でないとき、名目上オンのデバイス、すなわち、ピンチ抵抗が形成される。ダイオードは、絶縁体を貫通してAlGaN層に達する非凹部のオーム接点およびショットキー接点を設けることによっても形成される。  (もっと読む)

(もっと読む)

ゲート電極をトリミングする方法

第1寸法を有するゲート電極層を備えたゲート電極構造をトリミングする方法および処理ツールを提供する。反応層は、ゲート電極構造と反応することによって形成される。そして、この反応層は、化学エッチングによって、ゲート電極構造の未反応部分から選択的に除去される。これにより、第1寸法よりも小さい第2寸法を有するトリミングされたゲート電極構造が形成される。トリミング処理は、反応層の形成が実質的に自己制限的となるプロセス条件にて実行される。トリミング処理は、ゲート電極構造の寸法をさらに減少させるために繰り返し行うことができる。  (もっと読む)

(もっと読む)

整流素子およびそれを用いた電子回路、並びに整流素子の製造方法

一対の電極と、該一対の電極間に設けられた、1本または複数のカーボンナノチューブにより構成されるキャリア輸送体と、を備え、前記一対の電極のうち、一方の電極および前記キャリア輸送体の第1の界面と、他方の電極および前記キャリア輸送体の第2の界面と、が異なる障壁レベルとなるように、これら2つの接続構成を異なる構成とすることで、高周波応答性、耐熱性に優れたキャリア輸送体を備えた整流素子を提供し、併せて、それを用いた電子回路、並びに整流素子の製造方法を提供する。  (もっと読む)

(もっと読む)

シリサイド成長ドーパント雪かき効果の使用による、デバイス中に階段接合の形成

トランジスタ(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に絶縁層(702)をたい積する。その後、絶縁層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

窒化ガリウム材料デバイスおよびその形成方法を提供する。該デバイスは、電極規定層を包含する。電極規定層は典型的にはその内部に形成されたビアを有し、該ビア内に電極が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。 (もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

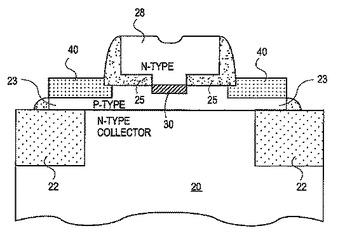

改善された外部ベース領域を備えたバイポーラ接合形トランジスタ及びその製造方法

バイポーラトランジスタ及びその製造方法に関する。第1のエピタキシャル層(23)上への第2の、より高濃度にドープされたエピタキシャル層の成長によって、外部ベース領域(40)が形成される。第2のエピタキシャル層は上にあるポリシリコンエミッタ台座(28)の下まで広がり、かつ、この台座(28)から絶縁される。  (もっと読む)

(もっと読む)

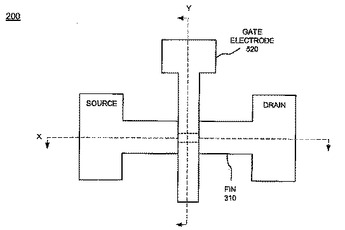

セルフアラインされたダマシンゲート

基板上のフィン領域、ソース領域、およびドレイン領域をパターン化するステップと、フィン領域中にフィン(310)を形成するステップと、フィン領域中にマスク(320)を形成するステップと、を含む、MOS電界効果トランジスタ(MOSFET)(200)を形成する方法である。この方法は、MOSFETのチャネル領域(330)を露出するように、マスク(320)をエッチングするステップと、チャネル領域(330)中のフィン(310)の幅を薄くするようにフィン(310)をエッチングするステップと、フィン(310)上にゲートを形成するステップと、ゲート、ソース領域およびドレイン領域に対するコンタクトを形成するステップと、をさらに含む。  (もっと読む)

(もっと読む)

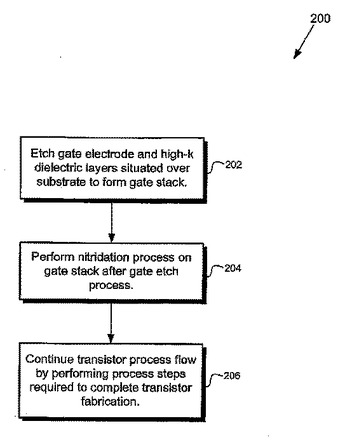

トランジスタ製造プロセスにおいて、high−kゲート絶縁体を組み入れる方法

本発明の例示的な一実施形態は、その上に位置するhigh-k誘電体層と、このhigh-k誘電体層上に位置するゲート電極層と、を含む基板(104)上に電界効果トランジスタを形成する方法である。この方法は、基板(104)上に位置するhigh-k誘電体部(106)と、high-k誘電体部(106)上に位置するゲート電極部とを含むゲートスタック(102)を形成するように、ゲート電極層およびhigh-k誘電体層をエッチングするステップ(202)を含む。この例示的な実施形態によれば、この方法は、ゲートスタック(102)上で窒化プロセスを実行するステップ(204)をさらに含む。この窒化プロセスは、ゲートスタック(102)のサイドウォール(110)を窒化するように、窒素を含むプラズマを利用するステップによって実行することができる。この窒化プロセスの結果、窒素がhigh-k誘電体部(106)に入り込み、窒素がhigh-k誘電体部(106)中に酸素拡散バリアを形成するようにされてよい。  (もっと読む)

(もっと読む)

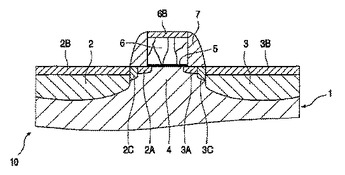

半導体装置とこの種の半導体装置の製造方法

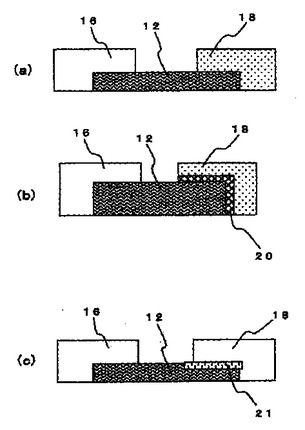

この発明は、基板と半導体本体(1)とを有する半導体装置(10)に関し、半導体本体(1)がソース(2)及びドレイン(3)を有する第一のFET(3)を備え、ソース(2)及びドレイン(3)は、金属シリサイドを含む接続領域(2B,3B)が設けられ、そして、ゲート(6)下部のチャネル領域(4)と境界を成し且つソース(2)及びドレイン(3)より厚みが薄く且つドーピング濃度が低いソース及びドレイン領域拡張部(2A,3A)に接続されている。ソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)とは、第一の導電型で且つ厚み及びドーピング濃度がソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)との間の中間領域(2C,3C)により互いに接続されている。このようにして、接続領域(2B,3B)と基板と間にリーク電流並びに短絡が起きるのが抑制され、一方で、ソース及びドレイン領域拡張部(2A,3A)を用いることの効果が維持される。好ましくは、中間領域(2C,3C)がゲート(6)直近のスペーサ(7)下部に位置し、好ましくは、これらは、なるべく傾けられたイオン注入により形成される。  (もっと読む)

(もっと読む)

2,921 - 2,940 / 2,965

[ Back to top ]