Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

301 - 320 / 3,070

半導体装置及びその製造方法

【課題】ゲート電極の形状を精度良く形成すると共に、隣り合うゲート電極同士がショートすることを防止する。

【解決手段】開口部を有するマスク16Mを用いて、導電膜15にイオンを注入し、ミキシング膜20Xを形成する。次に、マスクを除去した後、導電膜及びミキシング膜の上に、平面形状がライン形状のレジストパターン21を形成する。次に、レジストパターンをマスクとして、導電膜及びミキシング膜をエッチングし、導電膜15aを有するゲート電極を形成すると共に、ゲート電極のゲート幅方向の側面の上に、ミキシング膜20xを残存させる。次に、熱処理により、ミキシング膜に含まれるイオンと、元素(元素は、導電膜に由来する)とを反応させて、絶縁膜24xを形成する。絶縁膜は、ゲート電極と一体に形成されている。絶縁膜により、ゲート電極と、該ゲート電極とゲート幅方向に沿って隣り合う他のゲート電極との間が電気的に分離されている。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、エッチストッパー層を設けなくてもウェットエッチング時の加工性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、前記半導体層と前記金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層は、高融点金属系薄膜とSi薄膜の積層構造を有し、Si薄膜は半導体層と直接接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたN+型ソース層とソース電極のコンタクト抵抗が低減されたパワーMOSトランジスタの実現を図る。

【解決手段】N型ドリフト層2の表面にP型ボディ層6を形成し、該P型ボディ層6の表面にN+型ソース層7を形成する。N+型ソース層7上を被覆する層間絶縁膜8に第1のコンタクトホール9を形成し、N+型ソース層7の一部を露出する。第1のコンタクトホール9の底面に露出したN+型ソース層7の表面からP型ボディ層6内まで第2のコンタクトホール10を形成する。第2のコンタクトホール10の底面に露出したP型ボディ層6の表面にP+型コンタクト層11を形成する。第1のコンタクトホール9の底面にフォトリソグラフィ工程のマスク合わせ精度のばらつき幅より小さい幅のN+型層7aを形成し、第1、第2のコンタクトホール9、10内をタングステン層12等で埋設する。

(もっと読む)

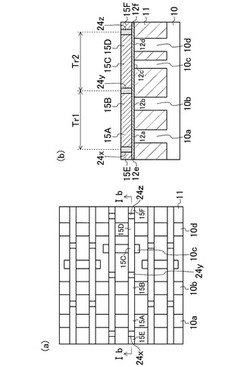

薄膜トランジスタ表示板の製造方法

【課題】半導体層の側壁がデータ線の側壁に対して突出することを最小化する。

【解決手段】ゲート絶縁膜140上に第1、第2非晶質シリコン層150,160、データ金属層170形成段階と、上部データ金属層170r上に第1感光膜パターン50形成段階と、第1感光膜パターンをマスクとしてデータ金属層170をエッチングして、第1下部データ金属パターン及び側壁が突出した突出部を含む第1上部データ金属パターン形成段階と、第1感光膜パターンをマスクとして第1及び第2非晶質シリコン層をエッチングして、非晶質シリコン層パターン形成段階と、第2感光膜パターンをマスクとして第1上部データ金属パターンをエッチングして、第2上部データ金属パターン形成段階と、第2感光膜パターンをマスクとして第1下部データ金属パターン、非晶質シリコン層パターンをエッチングして、半導体、データ線等を形成する段階、とを含む。

(もっと読む)

導電性金属ペースト

【課題】150℃〜250℃の範囲に選択する温度で焼結処理を施すことで、膜厚が厚く、利用する金属の3倍以下の体積固有抵抗率を有する導電体層を高い再現性で作製する用途に十分に適合する、バインダー樹脂成分を含有していない、新規な構成の導電性金属ペーストを提供する。

【解決手段】導電性金属ペースト中に含有される、金属微細粉末の体積比率Vmetal-particle、金属ナノ粒子の体積比率Vnano-particle、その被覆剤分子層の形成に利用される被覆剤分子の体積比率Vcoating-molecule、分散溶媒の体積比率Vsolventについて、比Vmetal-particle:(Vnano-particle+Vcoating-molecule+Vsolvent)を1:1〜1:4.6の範囲に、比(Vnano-particle+Vcoating-molecule):Vsolventを1:0.7〜1:3の範囲に、比(Vmetal-particle:Vnano-particle)を90:10〜60:40の範囲に選択する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

スパッタリング方法

【課題】例えば3以上の所定のアスペクト比を有するホールがパターニング形成されたものを処理対象物とし、これらホールを含む処理対象物の表面全体に亘って金属膜を成膜する際に、カバレッジ率を効果的に向上できるスパッタリング方法を提供する。

【解決手段】真空チャンバ1内に処理対象物Wと、処理対象物に形成しようとする金属膜に応じて作製されたターゲット2とを対向配置し、処理対象物の全面に亘って垂直な磁場が作用するように垂直磁場MFを発生させ、この真空チャンバ内にスパッタガスを導入し、ターゲットに所定の電力を投入して真空チャンバ内にプラズマを形成してターゲットをスパッタリングし、スパッタガスをアルゴンとして、スパッタリング中、真空チャンバ内のアルゴンの分圧を5〜30Paの範囲に保持して成膜する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、ソースドレイン間のリーク電流を低減する。

【解決手段】ゲート絶縁膜112に接する第1のゲート膜114として、インジウムと窒素を有し、バンドギャップが2.8電子ボルト未満の化合物導電体を用いる。この化合物導電体は、仕事関数が5電子ボルト以上、好ましくは5.5電子ボルト以上であるので、酸化物半導体膜106の電子濃度を極めて低く維持でき、その結果、ソースドレイン間のリーク電流が低減する。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

有機薄膜トランジスタの製造方法及び該方法で製造された有機薄膜トランジスタ

【課題】大面積の素子の製造が容易であり、ソース電極及びドレイン電極を形成する際にゲート絶縁層を損傷せず、有機絶縁材料が有する柔軟性を損なわない、有機薄膜トランジスタの製造方法を提供すること。

【解決手段】ゲート電極、及び該ゲート電極を被覆し、有機絶縁材料を含むゲート絶縁層を形成する工程;該ゲート絶縁層上に塗布法、無電解めっき法又は原子層堆積法を用いて導電性材料からなる第1導電層を成膜する工程;該第1導電層上にパターンニングされた第2導電層を形成する工程;該第2導電層で被覆されていない第1導電層の部分を除去して、第1導電層及び第2導電層からなるソース電極及びドレイン電極を形成する工程;及びソース電極、ドレイン電極、及び該ソース電極と該ドレイン電極に挟まれた領域のゲート絶縁層が被覆されるように、有機半導体層を形成する工程;を有する、有機薄膜トランジスタの製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

硬化性組成物およびそれを用いた薄膜トランジスタ

【課題】光硬化性を有し、かつ耐溶剤性、メタル配線への密着性に優れた薄膜を与える硬化性組成物を提供することである。

【解決手段】 必須成分として(A)光重合性官能基を有する化合物、(B)アルケニル基を有する化合物、(C)SiH基を有する化合物、(D)光重合開始剤 (E)ヒドロシリル化触媒を含有する硬化性組成物であり、

成分A、Dよる光重合反応と成分B、Cおよび成分Eによるヒドロシリル化反応の2種の反応が進行することにより、光硬化性を有しながら耐溶剤性、メタル配線への密着性に優れた薄膜を与える得ることが可能となる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

積層構造のソース・ドレイン電極を有する有機薄膜トランジスタ

【課題】柔軟性及び耐久性に優れ、素子特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタを提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、第1導電層は、酸化タングステン、酸化銀、酸化銅、酸化亜鉛、銀塩、銀及び銅からなる群から選ばれる1種以上の材料を含み、該第2導電層は、Ag、Al、Au、Cd、Co、Cr、Cu、Fe、Mg、Mo、Ni、Pb、Pd、Pt、Sn、Ta、Ti、V、W、Zn、Zr、及びこれらの金属のいずれかを含む合金からなる群から選ばれる1種以上の材料を含む、有機薄膜トランジスタ。

(もっと読む)

太陽電池及びその製造方法

【課題】本発明は、太陽電池及びその製造方法に関する。

【解決手段】本発明の一実施形態による太陽電池は、太陽光を吸収して電気を発生させる太陽電池部と、上記太陽電池部の上面及び下面のうち少なくとも一面に形成され、非共有電子対を有する官能基−Yとアルコキシ基−ORとを有する化合物の縮合反応によって形成された表面処理層と、上記表面処理層の非共有電子対を有する官能基−Yと結合された金属電極層と、を含む。本発明による太陽電池はエネルギー変換効率に優れた特徴を有する。

(もっと読む)

半導体装置

【課題】半導体装置の耐圧を向上させる。

【解決手段】半導体装置10は、p型半導体基板1、p型半導体基板1内に設けられたn型ドリフト領域3、及びn型ドリフト領域3内に設けられたp型ボディ領域4を含む。p型ボディ領域4の側面とn型ドリフト領域3とのpn接合部22の上方に、そのpn接合部22に沿って、環状のゲート電極6が設けられる。このゲート電極6の一部を挟んでn型ドリフト領域3内及びp型ボディ領域4内にそれぞれ、n型ドレイン領域7及びn型ソース領域8が設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

TFT用銅スパッタリングターゲット材、TFT用銅膜、及びスパッタリング方法

【課題】成膜条件(成膜中の圧力、成膜に用いるガス種等)を変更しなくても、成膜された銅膜中の引張残留応力を低減できるTFT用銅スパッタリングターゲット材、TFT用銅膜、及びスパッタリング方法を提供する。

【解決手段】本発明に係るTFT用銅スパッタリングターゲット材は、銅材からなり、銅と不可避的不純物とからなる無酸素銅、又は銅合金からなるスパッタ面を備え、かつ、(111)面と、(200)面と、(220)面と、(311)面との総和に対する、(111)面の占有割合が、15%以上であるTFT用銅スパッタリングターゲット材である。

(もっと読む)

301 - 320 / 3,070

[ Back to top ]