Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

241 - 260 / 3,070

半導体装置およびその製造方法

【課題】より良質なゲート電極を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、ドレイン層と、前記ドレイン層の上に設けられたドリフト領域と、前記ドリフト領域の上に設けられたベース領域と、前記ベース領域の表面に選択的に設けられたソース領域と、前記ソース領域から前記ベース領域を貫通し、前記ドリフト領域に到達するトレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、前記ドレイン層に接続された第1主電極と、前記ソース領域および前記ベース領域に接続された第2主電極と、を備える。前記ゲート電極は、第1導電層と、前記第1導電層と前記ゲート絶縁膜との間に介在する第2導電層と、を含み、前記第2導電層の不純物濃度は、前記第1導電層の不純物濃度よりも低い。

(もっと読む)

成膜方法、成膜装置、半導体装置及びその製造方法

【課題】めっき液への溶解性が低く、かつ単膜でCu拡散のバリア性にも優れたコバルト膜の成膜方法及び成膜装置を提供する。

【解決手段】炭素含有コバルト膜の成膜方法は、成膜装置100の処理容器1内にウエハWを搬入し、ステージ3上に配置する工程と、処理容器1内の圧力及びウエハWの温度を調節する工程と、処理容器1内にCo2(CO)8とアセチレンとをそれぞれ供給して処理容器1内で混合し、CVD法によりウエハWの表面に炭素含有コバルト膜を堆積させる工程と、成膜原料の供給を停止し、処理容器1内を真空引きする工程と、処理容器1内からウエハWを搬出する工程とを備えている。

(もっと読む)

半導体集積回路装置用ルテニウムバリア膜とその作製方法及び該ルテニウムバリア膜を有する半導体集積回路装置とその製造方法

【課題】クレバスの面積比が小さく、低抵抗を維持した薄膜の状態で、配線層を構成する銅又はアルミニウム等の拡散を防止できるルテニウムバリア膜とその作製方法及び該ルテニウム膜を有する半導体集積回路装置とその製造方法を提供する。

【解決する手段】ルテニウムバリア膜は、ルテニウムを主成分とする金属からなり、表面上に観測されるクレバス(溝、割れ目又は深く鋭いくぼみ)の占める面積比が、前記バリア膜表面の全面積に対して15%以下であり、広角X線回折測定によって得られるX線回折プロファイルにおいて、ルテニウムの結晶配向面(002)及び(100)に起因するスペクトルのそれぞれのピーク強度比であるRu(002)/Ru(100)が10以上であり、また、スパッタリング法によって、温度を500℃以上に加熱した状態の半導体基板の配線溝上に成膜されることを特徴とする。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてCo2(CO)8を用いてCo膜を成膜する場合に、段差被覆性が良好でかつ再現性高くCo膜を成膜することができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、成膜原料として固体原料であるCo2(CO)8を用い、これをCo2(CO)8の分解開始温度未満の温度で気化させて気体原料とし、これを基板Wに至るまでCo4(CO)12が生成されないようにして基板Wに供給し、前記基板上で熱分解によりCo膜を成膜する。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてCo2(CO)8を用いてCo膜を成膜する場合に、Co膜の針状の異常成長を抑制することができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、基板Wの温度を160〜300℃とし、処理容器1内に気体状のCo2(CO)8を供給し、基板W上でCo2(CO)8を熱分解させて基板W上にCo膜を成膜する。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】ポリイミド膜に対して高い密着性を有するコバルト膜を成膜する方法を提供する。

【解決手段】成膜装置100の処理容器1内で、処理容器1内にCOガスを導入しながら、ポリイミド膜81が形成されたウエハWを110℃以上400℃以下の温度で加熱し、ポリイミド膜81を熱処理する。熱処理によって、ポリイミド膜81中の分子が熱分解し、膜密度が減少するとともに、表面粗度が大きくなる。その後、処理容器1内に成膜原料であるCo2(CO)8を導入してCVD法によりポリイミド膜81上にコバルト膜83を堆積させる。

(もっと読む)

金属薄膜の成膜方法、半導体装置及びその製造方法

【課題】単膜でCu拡散のバリア膜及びめっきシード層として機能するとともに、Cuとの密着性にも優れた金属薄膜の成膜方法を提供する。

【解決手段】金属薄膜の成膜方法は、Ti膜を成膜する工程(STEP1)、Ti膜上にCo膜を形成する工程(STEP2)、Ti膜及びCo膜を熱処理してCo3Ti合金を含む金属薄膜を形成する工程(STEP3)を備えている。Co3Ti合金を含む金属薄膜は、優れた導電性とCu拡散バリア性を有し、Cuとの格子不整合が0.15%と非常に小さいため、Cu配線と優れた密着性が得られる。

(もっと読む)

銅めっき溶液およびこれを用いた銅めっき方法

【課題】高縦横比のビアホールを埋め込むのに好適な銅めっき溶液および銅めっき方法を提供する。

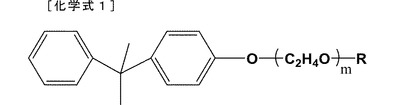

【解決手段】シード層を有する基板を浸漬し、水、銅供給源、電解物質、塩素イオン、第1添加剤、第2添加剤、および第3添加剤を含み、前記第1添加剤は、化学式1に示す化合物である銅めっき溶液を用いて銅めっきを行う。

(式中、Rは、水素原子または炭素原子数1〜6のアルキル基であり、mは、平均重合度であり6〜14の実数である。)

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

電子部品の製造方法

【課題】 基板上に、高い精度で、形成不良なく電極を形成し得る電子部品の製造方法を提供する。

【解決手段】 本発明の電子部品の製造方法は、平板状の基板1を準備する基板準備工程と、基板1の主面上にレジストパターン2aを形成するレジストパターン形成工程と、基板1の主面上のレジストパターン2aが形成されていない部分にIDT電極4を薄膜技術により形成する電極形成工程と、レジストパターン2aを除去するレジストパターン除去工程とを含み、電極形成工程は、基板1を、電極が形成される側の主面が凹むように反らせておこなうようにした。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

Cu配線の形成方法およびCu膜の成膜方法、ならびに成膜システム

【課題】微細なトレンチまたはホール等の凹部にボイドを発生させずに確実にCuを埋め込むことができ、かつ低抵抗のCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202において、トレンチ203の表面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上に、加熱しつつ、PVDによりCuがマイグレーションするようにCu膜206を形成してトレンチ203を埋める工程とを有する。

(もっと読む)

複合シールド組立体、蒸着チャンバー及び高出力蒸着装置

【課題】ワークピースの配置場所を画成する蒸着装置において長期の高出力作動が可能となるシールド組立体を提供する。

【解決手段】複合シールド組立体10は、ワークピースの配置場所の周囲に置かれる第1シールド要素13と、第1シールド要素13の周りに延在して第1シールド要素13を保持する第2シールド要素14であって、第1シールド要素13の熱伝導率が当該第2シールド要素14の熱伝導率よりも大きく、第1シールド要素13及び当該第2シールド要素14が、熱的接触を密接にするように配置される、第2シールド要素14とを含む。

(もっと読む)

半導体装置

【課題】信頼性を犠牲にすることなく、オン抵抗を低減することができるトレンチゲート型の半導体装置を提供する。

【解決手段】半導体装置1は、ドレイン領域21と、ドレイン領域21に積層されたチャネル領域20と、チャネル領域20に積層されたソース領域16とを有するシリコン半導体層からなる活性領域30を含む。半導体装置1は、さらに、ソース領域16からチャネル領域20を貫通してドレイン領域21に至るトレンチ15内に埋め込まれたゲート導体(ポリシリコンゲート)26と、ソース領域16に電気的に接続されたソース電極4とを含む。ソース電極4は、ソース領域16に接するように形成され、ソース領域16との界面がシリサイド化された密着層41を有する。密着層41は、膜厚が150Å以下の金属層からなる。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

Al基合金スパッタリングターゲット、及びCu基合金スパッタリングターゲット

【課題】Al基合金スパッタリングターゲットやCu基合金スパッタリングターゲットを用いたときのプレスパッタリング時、及び続いて行われる基板等へのスパッタリング時の成膜速度が高められ、且つスプラッシュなどのスパッタリング不良を抑制し得る技術を提供すること。

【解決手段】Al基合金またはCu基合金スパッタリングターゲットの最表面から1mm以内の深さのスパッタリング面法線方向の結晶方位<001>±15°と、<011>±15°と、<111>±15°と、<112>±15°と、<012>±15°との合計面積率をP値としたとき、下記(1)および/または(2)の要件を満足するスパッタリングターゲット。

(1)前記P値に対する、<011>±15°の面積率PA:40%以下、

(2)前記P値に対する、<001>±15°と<111>±15°との合計面積率PB:20%以上

(もっと読む)

241 - 260 / 3,070

[ Back to top ]