Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

181 - 200 / 3,070

素子及び太陽電池並びに電極用ペースト組成物

【課題】焼成時における銅の酸化が抑制され、良好なオーミックコンタクトを有する銅含有電極がシリコンを含む基板上に形成された素子及び該素子を構成するのに好適な電極用ペースト組成物を提供する。

【解決手段】シリコンを含む基板と、前記基板上に配置された電極とを有し、前記電極は、銅含有粒子、ガラス粒子、溶剤及び樹脂を含む電極用ペースト組成物の焼物であり、体積抵抗率が1×10−4Ω・cm以下である素子である。また電極用ペースト組成物に、リン含有銅合金粒子、錫含有粒子、ガラス粒子、溶剤及び樹脂を含ませ、25℃における粘度が80Pa・s〜1000Pa・sの範囲であるように構成する。さらにまた電極用ペースト組成物に、リン含有銅合金粒子、錫含有粒子、ガラス粒子、溶剤及び樹脂を含ませ、固形分濃度が70質量%〜98質量%の範囲であるように構成する

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】良好なオン特性を維持したまま、逆方向バイアスに対するリーク電流を低減した半導体デバイスを得る。

【解決手段】窒化物系化合物半導体からなるチャネル形成層と、チャネル形成層上に設けられ、第1の窒化物系化合物半導体からなる第1の半導体層、および、第2の窒化物系化合物半導体からなる第2の半導体層を有する疑似混晶からなる疑似混晶層と、疑似混晶層上に設けられ、窒化物系化合物半導体からなり、チャネル形成層の多数キャリアと反対の導電型を有する導電半導体層と、導電半導体層に接する第1の電極と、チャネル形成層に電気的に接続された第2の電極と、を備える半導体デバイスを提供する。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

トランジスタ、その製造方法および表示装置

【課題】ソース電極およびドレイン電極からのオーミックコンタクト膜の延在部分の表面を介したリーク電流、およびオーミックコンタクト膜と半導体能動膜との接合側面部での欠陥を介したリーク電流を増大させないことが可能な薄膜トランジスタを提供することにある。

【解決手段】オーソミックコンタクト層8の一方は、電極9,10の一方に接触して覆われた接触部分81と、接触部分81よりも厚さ方向D2において薄く、厚さ方向D2から見て電極9,10の一方からはみ出して電極9,10の他方へと延在して半導体能動膜7の少なくとも一部71を避けて覆う延在部分82とを有する。

(もっと読む)

配線膜、薄膜トランジスタ、ターゲット、配線膜の形成方法

【課題】信頼性の高い薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ20のゲート電極15、ソース、ドレイン電極33、34のうち、いずれか一つ以上の電極はバリア膜25を有し、バリア膜25が成膜対象物21又は半導体層30に密着している。NiとMoを100原子%としたときに、バリア膜25は、Moを7原子%以上70原子%以下含有し、ガラスからなる成膜対象物21や半導体層30に対する密着性が高い。また、バリア膜25表面にCuを主成分とする金属低抵抗層26が形成された場合に、Cuが半導体層30に拡散しない。

(もっと読む)

半導体デバイス及び薄膜トランジスタ、並びに、それらの製造方法

【課題】管理コストを低減し、さらに、製造工程を削減して製造原価のコストダウンを図ることの可能な半導体デバイス及び薄膜トランジスタ、並びに、それらの製造方法の提案を目的とする。

【解決手段】所定の材料からなり、活性層41となる半導体と、所定の材料と同じ組成の材料からなり、ソース電極51、ドレイン電極53及び画素電極55の少なくとも一つとなる導電体とを備えた薄膜トランジスタ2の製造方法であって、非晶質の所定の材料からなる被処理体及び導電体(ソース電極51、ソース配線52、ドレイン電極53、ドレイン配線54及び画素電極55)を一括成膜し、さらに一括形成する工程と、形成された被処理体を結晶化させて活性層41とする工程とを有する方法としてある。

(もっと読む)

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

電極箔および有機デバイス

【課題】支持基材、電極および反射層としての機能を兼ね備え、かつ、フレキシブル、軽量、薄型の有機太陽電池等の電子デバイスに有用な電極箔を提供する。

【解決手段】金属箔と、金属箔上に直接設けられるグラフェン層とを備える電極箔が提供される。

(もっと読む)

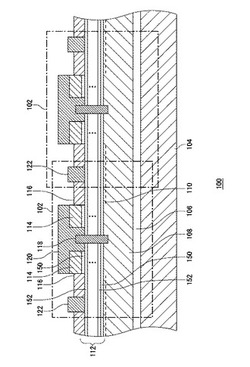

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

基板中間体、基板及び貫通ビア電極形成方法

【課題】貫通ビア電極を形成する際に処理温度が高くなく且つ低コストで、バリア層を均一に、且つ高い密着強度で製造する。

【解決手段】シリコン基板10の厚さ方向に形成された高アスペクト比の、貫通ビア電極形成用の孔12の内周面に、自己組織化単分子膜24を形成し、これに、金属ナノ粒子14を、高密度で吸着させて、この金属ナノ粒子14を触媒として、バリア層を無電解めっきにより形成し、バリア層の上にシード層を無電解めっきにより形成し、次に、貫通ビア電極材を電解めっきにより堆積して、孔12を埋めて、貫通ビア電極を形成する。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボト

ムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン

電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設

けることによってオーミック性のコンタクトを形成する。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理後も低い電気抵抗率を有する新規なCu合金膜を提供する。

【解決手段】基板上にて、基板及び/又は絶縁膜と直接接触するCu合金膜であって、前記Cu合金膜は基板側から順に、合金成分としてX(Xは、Ag、Au、C、W、Ca、Mg、Al、Sn、BおよびNiよりなる群から選択される少なくとも一種の元素)を含有するCu−Mn−X合金層(第一層)と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる層(第二層)で構成されたCu合金膜である。

(もっと読む)

Cu膜の形成方法

【課題】バリアメタル膜とCu膜との密着性を向上する。

【解決手段】基板上に、スパッタ法によりバリアメタル膜としてTi膜又はTa膜を形成し、このバリアメタル膜上にスパッタ法により窒化物膜を形成し、この窒化物膜の上にCVD法によりCu膜を形成した後、100〜400℃でアニール処理を行う。このようにCu膜を形成することにより、バリアメタル膜とCu膜との密着性が向上する。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

181 - 200 / 3,070

[ Back to top ]