Fターム[4M104BB20]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | CoSi (1,014)

Fターム[4M104BB20]に分類される特許

41 - 60 / 1,014

半導体装置及びその製造方法

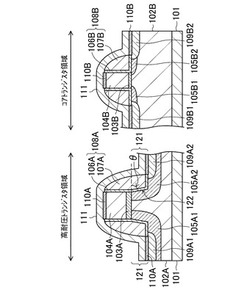

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

NiSi膜の形成方法、シリサイド膜の形成方法、シリサイドアニール用金属膜の形成方法、真空処理装置、及び成膜装置

【課題】 トレンチ及びホールパターンの底面や、側面に被覆カバレッジ性の良好なシリサイド膜を形成できるNiSi膜の形成方法及びシリサイド膜の形成方法、シリサイドアニール用金属膜の形成方法、真空処理装置、並びに成膜装置の提供。

【解決手段】Siを主組成とする基板上にNi膜を形成し、このNi膜を加熱処理することにより基板の上層にNiSi膜を形成する方法であって、NiSi膜を形成する加熱処理の前に、その加熱処理温度よりも低く、NiSi膜が形成されない温度で、H2ガスを用いてNi膜をプレアニールしてNi膜中の不純物を除去し、次いで得られたNi膜をシリサイドアニールする。シリサイド膜を形成する前にプレアニールするためのプレアニール用のH2ガスを導入する手段を備えた装置。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧な半導体素子を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、第一と第二の主面を有する炭化珪素基板と、炭化珪素基板の第一の主面に設けられた第一導電型の第一の炭化珪素層と、第一の炭化珪素層の表面に形成された第二導電型の第一の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第一導電型の第二の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第二導電型の第三の炭化珪素領域と、第一の炭化珪素層、第一の炭化珪素領域および第三の炭化珪素領域の表面に連続的に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された炭化珪素からなる第一の電極と、第一の電極上に形成された第二の電極と、第一と第二の電極を被覆する層間絶縁膜と、第二の炭化珪素領域と第三の炭化珪素領域と電気的に接続される第三の電極と、炭化珪素基板の第二の主面に形成された第4の電極と、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置

【課題】信頼性を犠牲にすることなく、オン抵抗を低減することができるトレンチゲート型の半導体装置を提供する。

【解決手段】半導体装置1は、ドレイン領域21と、ドレイン領域21に積層されたチャネル領域20と、チャネル領域20に積層されたソース領域16とを有するシリコン半導体層からなる活性領域30を含む。半導体装置1は、さらに、ソース領域16からチャネル領域20を貫通してドレイン領域21に至るトレンチ15内に埋め込まれたゲート導体(ポリシリコンゲート)26と、ソース領域16に電気的に接続されたソース電極4とを含む。ソース電極4は、ソース領域16に接するように形成され、ソース領域16との界面がシリサイド化された密着層41を有する。密着層41は、膜厚が150Å以下の金属層からなる。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

41 - 60 / 1,014

[ Back to top ]