Fターム[4M104BB20]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | CoSi (1,014)

Fターム[4M104BB20]に分類される特許

61 - 80 / 1,014

半導体装置

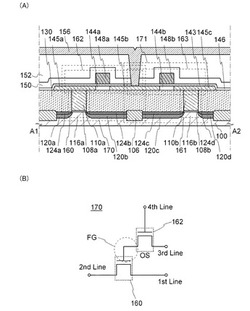

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】所望の抵抗値を有する制御ゲートを備えた半導体装置の製造方法を提供すること。

【解決手段】シリコン基板13の表面上に第1の絶縁膜15、電荷蓄積層16、第2の絶縁膜17、およびポリシリコン膜21をこの順で形成する工程と、ポリシリコン膜21上および両側壁全面に金属膜25を形成する工程と、金属膜25が形成されたポリシリコン膜21を加熱してシリサイド化する工程と、金属膜25を除去する工程と、を具備する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

SiC半導体装置

【課題】アバランシェ降伏時の電流集中を緩和することができ、耐圧およびアバランシェ耐量をともに向上させることができる、SiC半導体装置を提供すること。

【解決手段】n+型のSiC基板2上に、n−型のSiCエピタキシャル層4を形成し、SiCエピタキシャル層4上に、フィールド絶縁膜5を形成する。このフィールド絶縁膜5を貫通して、SiCエピタキシャル層4の表面に、アノード電極7をショットキー接合させる。一方、SiC基板2の裏面には、カソード電極3をオーミック接触させる。これにより、ショットキーバリアダイオード1を形成する。このショットキーバリアダイオード1において、SiCエピタキシャル層4の表層部に、アノード電極7のショットキーメタル9に接するガードリング13を形成する。そして、このガードリング13の表層部17におけるp型不純物濃度を、n型不純物濃度よりも小さくする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

半導体装置

【課題】トレードオフの関係にある臨界オフ電圧上昇率dV/dtとゲート感度との関係を改善した半導体装置を提供する。

【解決手段】少なくとも、ゲートトリガ電流IGTの経路となるベース層(P型ベース領域、P型半導体領域P1)のゲート電極M1bとのオーミック接触面である高濃度不純物層を、高融点金属シリサイド層LMで形成する。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜にハフニウムを含む絶縁膜を使用したMISFETを有する半導体装置において、MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】本発明では、nチャネル型コア用トランジスタQ1のゲート絶縁膜と、pチャネル型コア用トランジスタQ2のゲート絶縁膜の構成を相違させている。具体的に、nチャネル型コア用トランジスタQ1では、ゲート絶縁膜に酸化シリコン膜SO1とHfZrSiON膜HK1の積層膜を使用している。一方、pチャネル型コア用トランジスタQ2では、ゲート絶縁膜に酸化シリコン膜SO1とHfSiON膜HK2の積層膜を使用している。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置の製造方法

【課題】基板に形成される第1の膜と第2の膜との重なり量を精度良く算出する。

【解決手段】半導体装置の製造方法は、基板の第1の領域及び第2の領域に第1の膜を形成する工程と、第2の領域の第1の膜の幅を測定する工程と、基板の第2の領域及び第3の領域に第2の膜を形成する工程と、第2の領域の第2の膜の幅及び第2の領域の第1の膜と第2の膜との距離を測定する工程と、第2の領域における第1の膜の幅の測定値、第2の膜の幅の測定値、第1の膜と第2の膜との距離の測定値及び第1の膜と第2の膜とに関する設計値に基づいて、第1の領域における第1の膜と第3の領域における第2の膜との重なり量を算出する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

61 - 80 / 1,014

[ Back to top ]