Fターム[4M104BB25]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | 高融点金属のシリサイド (2,215) | TiSi (828)

Fターム[4M104BB25]に分類される特許

201 - 220 / 828

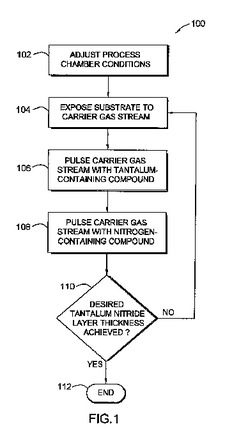

インサイチュチャンバ処理および堆積プロセス

本発明の実施形態は、原子層堆積(ALD)または化学気相堆積(CVD)などの気相堆積プロセス中に、プロセッシングチャンバの内面を処理し、材料を堆積させる方法を提供する。一実施形態では、前処理プロセス中に、プロセッシングチャンバの内面および基板を、水素化配位子化合物などの試薬にさらすことができる。この水素化配位子化合物は、次の堆積プロセス中に使用される有機金属前駆体から形成される遊離配位子と同じ配位子とすることができる。この遊離配位子は、堆積プロセス中に、通常、水素化または熱分解によって形成される。一例では、プロセッシングチャンバおよび基板は、ペンタキス(ジメチルアミノ)タンタル(PDMAT)などのアルキルアミノ配位子を有する有機金属化学前駆体を利用した気相堆積プロセスを行う前に、前処理プロセス中に、アルキルアミン化合物(例えば、ジメチルアミン)にさらされる。  (もっと読む)

(もっと読む)

成膜方法

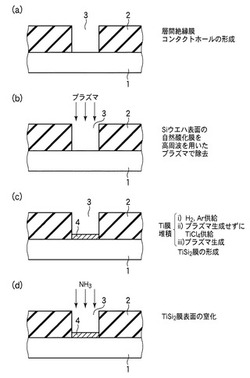

【課題】結晶粒径が均一な金属シリサイド膜、特にチタンシリサイド膜を形成することができる成膜方法を提供すること。

【解決手段】被処理体1のSi含有部分上の自然酸化膜を除去する工程と、被処理体1の自然酸化膜が除去されたSi含有部分上に金属シリサイド膜4を形成する工程とを具備し、金属シリサイド膜4を形成する工程は、最初にプラズマを生成せずに、成膜しようとする金属シリサイド中の金属を含有する金属含有原料ガスを所定時間供給して金属−シリコン結合を生じさせ(ii)、次いで金属含有原料ガスを供給しつつプラズマを生成して当該金属からなる金属膜を成膜し、その際の金属膜とSi含有部分との反応により金属シリサイド膜を形成する(iii)。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】簡易なプロセスで抵抗層上の所定領域を選択的にサリサイド化することができ、かつ、抵抗の占有面積を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】第1素子形成領域1と第2素子形成領域2とを有し、第2素子形成領域2に第1抵抗層30を形成し、その上に第1絶縁層40と導電層を形成し、第2素子形成領域2の導電層を高抵抗化し、導電層の一部を除去して、第1素子形成領域1にゲート電極50を形成すると同時に、第2素子形成領域2に第2抵抗層52を形成し、第2素子形成領域2の第2抵抗層52の上方に第2絶縁層90を形成し、第1素子形成領域1の半導体基板10に不純物を注入して、ソース領域およびドレイン領域70a,70bを形成し、ソース領域およびドレイン領域70a,70bの上と、第2素子形成領域2の第1抵抗層30および第2抵抗層52の上と、にシリサイド層80を形成する。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板10に形成されたシリコンを主成分とするソース・ドレイン拡散層3上、および半導体基板に形成されソース・ドレイン拡散層に隣接する素子分離絶縁膜の上に、金属を堆積して金属膜を形成し、第1の加熱温度の第1の加熱処理によりソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜106を形成し、シリサイド膜を酸化させないようにして、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜105を形成し、第1の加熱温度よりも高い第2の加熱温度の第2の加熱処理によりシリサイド膜のシリコンの濃度を増加させ、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置の製造方法

【課題】仕事関数金属膜と低抵抗膜とで構成されたゲート電極をプラズマエッチングする際に、膜質に応じたエッチングステップの切り替えの遅延を防ぐ。

【解決手段】低抵抗膜6中であって、仕事関数金属膜4との界面の近傍に、プラズマ発光モニタに感度のある、窒素を含む進捗モニタ層5を設けることで、エッチング中のプラズマ発光の変化を検知し、エッチングの進捗をモニタすることでエッチングステップ切り替えの遅延を防止することができる。

(もっと読む)

薄膜の成膜方法及び成膜装置

【課題】被処理体の凹部の径が小さくても、例えばバリヤ層として機能する薄膜が凹部の側壁へ堆積することを抑制しつつ、凹部の底部に効率的に堆積させることが可能な薄膜の成膜方法を提供する。

【解決手段】表面に凹部6が形成されている被処理体Wの表面に薄膜を形成する成膜方法において、凹部の内面を含む被処理体の表面にチタン化合物ガスと還元ガスとを用いてチタン膜100を形成するチタン膜形成工程と、窒化ガスを用いてチタン膜を全て窒化して第1の窒化チタン膜104を形成する窒化工程と、凹部の内面を含む被処理体の表面に第2の窒化チタン膜106を堆積させて形成する窒化チタン膜堆積工程と、を有する。これにより、被処理体の凹部の径が小さくても、薄膜が凹部の側壁へ堆積することを抑制しつつ、凹部の底部に効率的に堆積させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体装置

【課題】ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】基板上の酸化珪素膜と、酸化珪素膜上のソース領域、ドレイン領域、ソース領域の上部に形成された第1のシリサイド、ドレイン領域の上部に形成された第2のシリサイド、及びチャネル形成領域を有する半導体層と、ゲイト絶縁膜と、多結晶珪素膜及び第3のシリサイドを有するゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに密着して形成された第1の金属配線と、第2のシリサイドに密着して形成された第2の金属配線と、を有し、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1乃至第3のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化された構造においても効果を発揮する歪みシリコン技術を適用した半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板中の前記ゲート絶縁膜下に形成されたチャネル領域と、前記チャネル領域の両側に形成された第1の層、および前記第1の層の下層に位置し、ゲート電極中央側の端部の位置が前記第1の層よりも前記ゲート電極中央に近い第2の層を含み、前記チャネル領域に歪みを発生させる歪み付与層と、前記チャネル領域の両側に、少なくとも一部が前記歪み付与層と重なるように形成されたソース・ドレイン領域と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】WPP技術を使用する半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】半導体ウェハW3に形成されている製品チップ領域(例えば、製品チップ領域CAや製品チップ領域CB)に製品パターンを形成する。そして、製品チップ領域の外側にある外周領域の大部分にも製品パターンの一部を形成する。一方、外周領域に形成されているネーミング領域NRを覆うように開口部を有さないレジストパターンRMを形成する。外周領域に形成されているレジストパターンRMと製品チップ領域CBとの間に開口パターンKP1を形成する。このようなパターンが形成された半導体ウェハW3に対して、電解めっきを実施する。

(もっと読む)

半導体装置の製造方法および固体撮像装置の製造方法

【課題】本発明は、コンタクト抵抗の安定性を確保して、コンタクト抵抗にばらつきを抑えることを可能にする。

【解決手段】基板11のシリコン領域12上に第1金属シリサイド層13を形成する工程と、前記基板11上に前記第1金属シリサイド層13を被覆する絶縁膜14を形成する工程と、前記絶縁膜14に前記第1金属シリサイド層13に通じるコンタクトホール15を形成する工程と、前記コンタクトホール15の内面および前記絶縁膜14上にシリサイド化される第2金属層16を形成する工程と、前記第2金属層16と前記コンタクトホール15の底部のシリコンとを反応させて前記第1金属シリサイド層13上に第2金属シリサイド層17を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】FD−SOIの如き半導体層の厚みが薄い基板を使用してトランジスタを形成する際に、比較的簡便なプロセスでリーク電流の増加を回避しつつ、トランジスタの活性領域にシリサイド層を導入してトランジスタ寄生抵抗の低減を実現し得る半導体装置の製造方法を提供する。

【解決手段】SOI基板の半導体層の上にゲート酸化膜、ゲート電極材料を順次形成し、ゲート電極のパターニングを行う。ゲート電極の側壁部を覆う絶縁体からなるサイドウォールを形成する。半導体層のゲート電極を挟む位置にイオン注入してドレイン/ソース領域を形成する。サイドウォールを部分的にエッチングして、ゲート電極の側壁上部を露出させる。ドレイン/ソース領域とゲート電極の上面および露出した側壁部を覆うように金属膜を堆積させる。SOI基板に熱処理を施してゲート電極およびドレイン/ソース領域の表面にシリサイド層を形成する。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、たとえゲート構造間の距離が小さくなったとしても、ゲート構造間の半導体基板上に適正な膜厚のシリサイド膜を形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一実施例によれば、ゲート構造G1,G2間の半導体基板1上の領域である第一の領域に形成される金属膜8の膜厚が、所望の膜厚以上となるように、第一の領域を含む半導体基板1上に、金属膜8を形成する。そして、シリサイド膜11形成のために、所望の膜厚分の金属膜8が半導体基板1を構成するシリコンと反応する程度の熱エネルギーを、半導体基板1に対して加える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

201 - 220 / 828

[ Back to top ]