Fターム[4M104DD04]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | 側壁堆積膜の利用 (769)

Fターム[4M104DD04]に分類される特許

201 - 220 / 769

半導体装置及び半導体装置の製造方法

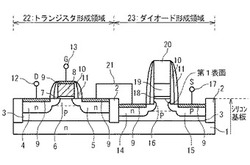

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域に高抵抗不純物領域(HRD

または低濃度不純物領域)を自己整合的に形成する方法を提供する。

【解決手段】ゲイト電極105上面にマスク106を残し、比較的低い電圧でポーラスな

第1の陽極酸化膜107をゲイト電極の側面に成長させる。この陽極酸化膜をマスクとし

てゲイト絶縁膜104’をエッチングする。必要に応じては比較的高い電圧でバリア型の

第2の陽極酸化膜108をゲイト電極の側面および上面に形成する。第1の陽極酸化膜を

選択的にエッチングする。不純物ドーピングをおこなうと、ゲイト電極の下部にはドーピ

ングされず、ゲイト電極に近い領域では、不純物濃度の低い高抵抗領域111,112と

なる。ゲイト電極から遠い領域では、不純物濃度の高い低抵抗領域110,113となる

。

(もっと読む)

半導体装置の製造方法

【課題】簡易な工程で、自己整合シリサイドプロセスを用いた、ポリ抵抗を有する半導体装置を得ることができる製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10に素子分離層20を形成する工程と、素子分離層の上方に抵抗層110を形成する工程と、抵抗層を覆う第1絶縁層120を形成する工程と、半導体基板の上方であって、素子分離層で区画された領域に、ゲート酸化膜220を形成する工程と、ゲート酸化膜の上方にゲート電極210を形成する工程と、ゲート電極の側壁にサイドウォール240を形成する工程と、半導体基板の露出した領域に不純物を注入して、ソースおよびドレイン領域を形成する工程と、第1絶縁層をパターニングすることによって、抵抗層を露出する工程と、抵抗層の露出した領域と、ゲート電極の上と、ソースおよびドレイン領域の上と、にシリサイド層30を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板を使用したSOI基板上に形成しても、ゲート電極を形成する導電膜を成膜する際に該導電膜の加える応力により、ガラス基板上の絶縁膜及び半導体膜がはがれないような半導体装置の作製方法の提供を課題の一つとする。

【解決手段】ボンド基板上に第1の絶縁膜を形成し、ボンド基板の表面からイオンを添加することによって脆化層を形成し、ボンド基板を、第1の絶縁膜を介してガラス基板と貼り合わせ、ボンド基板を脆化層において分離してガラス基板上に第1の絶縁膜を介して半導体膜を形成し、第1の絶縁膜及び半導体膜の周辺領域を除去してガラス基板の一部を露出させ、半導体膜、第1の絶縁膜及びガラス基板上に接してゲート絶縁膜を形成し、ゲート絶縁膜上に接して2層構造の積層導電膜を形成し、2層構造の積層導電膜として、上層に引っ張り応力を有する導電膜、下層に圧縮応力を有する導電膜を用いて半導体装置を作製する。

(もっと読む)

半導体素子の微細パターンの形成方法

【課題】複数の物質層間の溶解度差を利用してダブルパターニングを具現する半導体素子の微細パターンの形成方法を提供する。

【解決手段】半導体素子の微細パターンの形成方法は、基板100上に、空間を介して相互に離隔されている複数の第1マスクパターン120を、基板100の主面と平行方向に形成するステップと、溶解剤に対して第1溶解度を有する第1物質からなる複数のキャッピング層130を、複数の第1マスクパターン120のそれぞれの側壁及び上面に形成するステップと、溶解剤に対して第1溶解度より低い第2溶解度を有する第2物質からなる第2マスク層を、空間内に形成するステップと、溶解剤を利用してキャッピング層130を除去し、かつ、第2マスク層の一部を除去した後、空間に残った第2マスク層の残留部分を、複数の第2マスクパターン140Aとして形成するステップと、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性が高く良好な特性を有する半導体装置を提供する。

【解決手段】半導体基板101上に形成され、チャネル領域とチャネル領域を挟むソース/ドレイン・エクステンション領域108の少なくとも一部とを含むSiGe膜104aと、半導体基板の表面領域に形成され、ソース/ドレイン・エクステンション領域に接するソース/ドレイン・コンタクト領域110と、SiGe膜上に形成されたゲート絶縁膜105およびゲート電極106を有するゲート構造と、SiGe膜上に形成され、且つゲート構造の側面に形成された第1の側壁膜107と、SiGe膜上に形成され、且つ第1の側壁膜上に形成された第2の側壁膜109と、ソース/ドレイン・コンタクト領域上に形成され、且つSiGe膜の側面および第2の側壁膜上に形成された第3の側壁膜111と、ソース/ドレイン・コンタクト領域上に形成されたシリサイド膜112と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】トレンチゲート形成において、ペアスペースパターンの位置ずれの生じないパターン形成方法を提供する。

【解決手段】被加工層1上に、第3〜第1マスク層13,12,11を順次積層する。第1マスク層上に第4マスク層を形成し、第4マスク層をマスクにして第1マスク層をラインパターン形状に成形する。第1マスク層のライン幅方向両側に、サイドウオール層21aを形成してから第1マスク層を除去する。一対のサイドウオール層をマスクにして第2マスク層を一対のラインパターン形状に成形する。第3マスク層上に第5マスク層を形成し、第5マスク層をマスクにして一対の開口部を第3マスク層に設ける。第3マスク層をマスクにして被加工層に一対の溝部を設ける。

(もっと読む)

半導体装置、およびその製造方法

【課題】製造工程におけるエピタキシャル結晶層への熱的負荷を低減することのできる半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板上に第1のゲート絶縁膜を介して形成された第1のゲート電極、前記半導体基板中の前記第1のゲート絶縁膜下に形成された第1のチャネル領域、前記半導体基板中の前記第1のチャネル領域の両側に形成された第1の結晶からなる第1のエピタキシャル結晶層、を含む第1のトランジスタと、前記半導体基板上に第2のゲート絶縁膜を介して形成された第2のゲート電極、前記半導体基板中の前記第2のゲート絶縁膜下に形成された第2のチャネル領域、前記半導体基板中の前記第2のチャネル領域の両側に形成された第2の結晶からなる第2のエピタキシャル結晶層、前記第2のエピタキシャル結晶層上に形成された前記第1の結晶からなる第3のエピタキシャル結晶層、を含む、前記第1のトランジスタと異なる導電型を有する第2のトランジスタと、を有する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】プリ・メタル層間絶縁膜の構成法としては、オゾンTEOSによる酸化シリコン膜の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、高温リフローさせて平坦化した後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜を積層し、更にCMPで平坦化することが考えられる。しかし、コンタクト・ホール形成プロセスにおいて、プリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】NMOSFET及びPMOSFET等のNMOS及びPMOSを有する半導体装置において、ゲート電極の実効仕事関数を、Siバンドギャップのmid-gap付近の値に安定的に設定することが可能な半導体装置及びその製造方法を提供する。

【解決手段】素子分離膜によって分離されてなる、p型拡散層及びn型拡散層を有する半導体基板と、前記半導体基板の、前記p型拡散層及びn型拡散層それぞれの上に形成されてなるゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属膜を含むゲート電極と、前記ゲート絶縁膜と前記金属膜との界面に形成されたGe介在物と、前記金属膜上に形成されたシリコン含有層と、を具えるようにして半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート間のピッチが狭い場合における短チャネル効果の劣化を抑制する。

【解決手段】基板上に、第1ゲートと、第1ゲートに隣接する第2ゲートを形成する工程、第1ゲートの側壁に第1サイドウォールを、第2ゲートの側壁に第2サイドウォールを形成する工程、第1ゲート、第1サイドウォール、第2ゲート、第2サイドウォールをマスクとして、基板に第1不純物の注入を行う工程、全面に絶縁膜を堆積した後、絶縁膜をエッチングして、第1サイドウォールの側面に第3サイドウォールを、第2サイドウォールの側面に第4サイドウォールを、第1ゲートと第2ゲートの間において第3サイドウォールと第4サイドウォールとが接触するように形成する工程、第1ゲート、第1及び第3サイドウォール、第2ゲート、第2及び第4サイドウォールをマスクとして、基板に第2不純物の注入を行う工程、第3及び第4サイドウォールを除去する工程、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】極浅接合の深さが精密制御された半導体装置およびその製造方法を提供する。

【解決手段】主面が第1面方位である第1導電型の第1半導体層11と、第1半導体層11上に直接接合され、主面が第1面方位と異なる第2面方位である第1導電型の第2半導体層12と、第2半導体層12に連接して第1半導体層11上に形成され、主面が第1面方位である第3半導体層13a、13bと、第2半導体層12上にゲート絶縁膜を介して形成されたゲート電極15と、ゲート電極15をゲート長方向に挟むように第2半導体層12に形成され、第1半導体層11と第2半導体層12との接合面16に至る第2導電型の第1不純物拡散領域17a、17bと、第1不純物拡散領域17a、17bをゲート長方向に挟むように第3半導体層13a、13bから第1半導体層11の上部にかけて形成された第2導電型の第2不純物拡散領域18a、18bと、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低減に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11と、前記半導体基板上にゲート絶縁膜12を介して設けられるゲート電極13と、前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるエクステンション領域LDDと、前記エクステンション領域の両側を挟むように前記半導体基板中に設けられ、前記半導体基板とは異なる格子定数有し、前記半導体基板に歪みを付与する歪み付与層22と、前記エクステンション領域の両側の前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるソース/ドレインS/Dと、前記ソース/ドレイン上に設けられるシリサイド層SS/Dとを具備し、前記歪み付与層と前記半導体基板との界面Si-Siは、少なくとも前記シリサイド層の底面の一部に一致する。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセットスペーサが除去されることを防止する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13Aと、ゲート絶縁膜上に形成されたゲート電極15Aと、ゲート電極の側面上に形成されたオフセットスペーサ17Aと、ゲート電極の側面上にオフセットスペーサを介して形成された断面形状がL字状の内側サイドウォール19と、ゲート電極15A、オフセットスペーサ17A、内側サイドウォール19、及び半導体領域10xにおける内側サイドウォール19の外側方に位置する領域を覆うように形成された絶縁膜24とを備え、オフセットスペーサ17Aは、ゲート電極の側面上に形成された内側オフセットスペーサ16と、ゲート電極の側面上に内側オフセットスペーサ16を覆うように形成された外側オフセットスペーサ17とを有し、外側オフセットスペーサは、内側オフセットスペーサの上端及び外側面に接して形成されている。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化と信頼性の向上を図ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】化合物半導体基板に形成されたメサ22と、メサ22の壁面に形成された曲率表面を有する側壁16と、メサ22上に形成されるゲート電極と、ゲート電極と一体化され、側壁16の表面に形成されるゲートメタル18と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート酸化膜やゲート酸化膜と半導体基板の界面にダメージを与えることなく、界面準位の低減を図る。

【解決手段】シリコン酸化膜6で覆われたゲート電極4にポリシリコン膜8aとタングステンシリサイド膜8bの積層膜からなり、弗素を含んだ弗素含有膜8を形成する。この場合、先ず、シリコン酸化膜6で覆われたゲート電極4上にポリシリコン膜8aを形成し、ポリシリコン膜8a上にWF6とSiH4を原料ガスとしてLPCVD法によりタングステンシリサイド膜8bを形成する。この場合、WF6中の弗素はSiH4中の水素と反応し、大半は弗化水素(HF)ガスとして排気され、タングステンシリサイド膜8bを形成する反応が継続するが、弗素の一部はタングステンシリサイド膜8bの中に取り込まれる。その後、タングステンシリサイド膜8bの弗素をゲート酸化膜3中に熱拡散させるための熱処理が施される。

(もっと読む)

固体撮像装置、その製造方法および撮像装置

【課題】本発明は、画素部のMOSトランジスタ上で異なる2層のシリサイドブロック膜の一部が重なるように形成して、白傷、暗電流を低減することを可能にする。

【解決手段】半導体基板11に、光電変換部21を備えた画素部12とその周辺に形成された周辺回路部13を有し、画素部12のゲート電極32の側壁にサイドウォール形成膜で形成された第1サイドウォール33と、周辺回路部13のゲート電極52の側壁にサイドウォール形成膜で形成された第2サイドウォール53と、光電変換部21上および画素部12のMOSトランジスタ30の一部上にサイドウォール形成膜で形成された第1シリサイドブロック膜71と、画素部12のMOSトランジスタ30上に、第1シリサイドブロック膜71の一部上に重なる第2シリサイドブロック膜72を有し、第1、第2シリサイドブロック膜71、72で画素部12のMOSトランジスタ30上が被覆されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】簡易なプロセスで抵抗層上の所定領域を選択的にサリサイド化することができ、かつ、抵抗の占有面積を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】第1素子形成領域1と第2素子形成領域2とを有し、第2素子形成領域2に第1抵抗層30を形成し、その上に第1絶縁層40と導電層を形成し、第2素子形成領域2の導電層を高抵抗化し、導電層の一部を除去して、第1素子形成領域1にゲート電極50を形成すると同時に、第2素子形成領域2に第2抵抗層52を形成し、第2素子形成領域2の第2抵抗層52の上方に第2絶縁層90を形成し、第1素子形成領域1の半導体基板10に不純物を注入して、ソース領域およびドレイン領域70a,70bを形成し、ソース領域およびドレイン領域70a,70bの上と、第2素子形成領域2の第1抵抗層30および第2抵抗層52の上と、にシリサイド層80を形成する。

(もっと読む)

201 - 220 / 769

[ Back to top ]