Fターム[4M104DD04]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 製造工程全般 (1,971) | セルフアライン法(サリサイド法を含む) (1,918) | 側壁堆積膜の利用 (769)

Fターム[4M104DD04]に分類される特許

161 - 180 / 769

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程の増加を抑えて、通常のコンタクトとシェアードコンタクトとをそれぞれ良好なコンタクト特性を有するようにする。

【解決手段】半導体装置100は、第1の不純物拡散領域106aに接続するとともに、第1のゲート電極112aとは接続しないように形成された第1のコンタクト124と、第2のゲート電極112bおよび第2の不純物拡散領域106bに共通して接続するように形成された第2のコンタクト126とを含む。第1のコンタクト124および第2のコンタクト126は、それぞれ、層間絶縁膜122の表面から基板101に向かう途中の位置でテーパー角度が小さくなるように変化する形状を有し、第2のコンタクト126においてテーパー角度が変化する位置が、第1のコンタクト124においてテーパー角度が変化する位置よりも基板101に近い。

(もっと読む)

半導体装置及びその製造方法

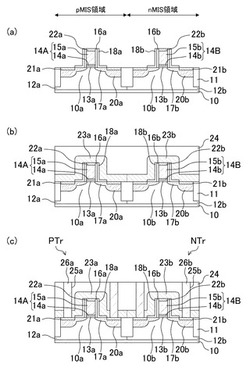

【課題】n型MISトランジスタとp型MISトランジスタとにおいてサイドウォール幅が同一である場合、n型MISトランジスタの高信頼性とp型MISトランジスタの高性能化を両立させることは難しい。

【解決手段】半導体装置は、n型MISトランジスタとp型MISトランジスタとを備えている。n型MISトランジスタは、半導体基板10における第1の活性領域10a上に順次形成された第1のゲート絶縁膜13a及び第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール16aとを備えている。p型MISトランジスタは、半導体基板10における第2の活性領域10b上に順次形成された第2のゲート絶縁膜13b及び第2のゲート電極14bと、第2のゲート電極14bの側面上に形成された第2のサイドウォール16bとを備えている。第2のサイドウォール16bは、第1のサイドウォール16aに比べてサイドウォール幅が小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(110,114又は122)のゲート誘電体層(500,566又は700)は、垂直濃度分布を有する窒素を含有している。

【解決手段】 該垂直濃度分布は、上側に位置しているゲート電極(502,568又は702)内のボロンが該ゲート誘電体層を介して下側のチャンネルゾーン(484,554又は684)内に著しく浸透することを防止し同時に該ゲート誘電体層から下側に存在する半導体ボディ内への窒素の移動を回避するために特別に調整されている。該チャンネルゾーン内の不所望のボロンから及び該半導体ボディにおける不所望の窒素から発生する場合がある損傷は実質的に回避される。

(もっと読む)

半導体構造体およびその製造方法(自己整合型ショットキー・ダイオード)

【課題】 自己整合型ショットキー・ダイオード及びその製造方法を提供する

【解決手段】 ショットキー障壁ダイオードは、セミコンダクタ・オン・インシュレータ(SOI)基板内の第2の導電型のドーピングを有するドープ保護環(リング)を含み、さらにダミー・ゲート電極の一方の側の、第2の導電型とは反対型の第1の導電型のドーピングを有する第1導電型ドープ半導体領域を含み、そしてショットキー障壁構造部は他方の側がドープ保護環により囲まれる。ショットキー障壁領域は、側部をダミー・ゲート電極及びドープ保護環により囲むことができる。ドープ保護環は、第2の導電型のドーピングを有するゲート側第2導電型ドープ半導体領域の非金属化部分を含む。ショットキー障壁領域は、側部を、ゲート側ドープ半導体領域及びSTI側ドープ半導体領域を含むドープ保護環により囲むことができる。ショットキー障壁ダイオードの設計構造体もまた提供する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長の短い微細デバイスの量産を容易にする。

【解決手段】先ず、第1領域22及び第2領域24が設定された半導体基板20の1の主表面20a上に、絶縁膜を形成する。次に、絶縁膜上に、第1領域の絶縁膜を覆い、かつ、第2領域の絶縁膜を露出するレジストパターン42を形成する。次に、絶縁膜の第2領域の部分を除去して、絶縁膜の第1領域の部分を第1絶縁膜32として残存させる。次に、第1絶縁膜の側面32a上に、金属を堆積させて金属膜50を形成する。次に、半導体基板の、第2領域の1の主表面上に、第2絶縁膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

半導体装置

【課題】メタル電極/high−kゲート絶縁膜からなるゲート構造において、半導体特性や信頼性の劣化をおこさせることなく、サイドウォールを形成したゲート構造を有する半導体装置の提供。

【解決手段】半導体基板1上に設けられた、high−k誘電体材料からなるゲート絶縁膜2と、ゲート絶縁膜2の上に設けられたメタル電極3と、メタル電極3の側壁を覆い、ゲート絶縁膜2を挟んで半導体基板1と対向配置された酸化防止膜4と、ゲート絶縁膜2と酸化防止膜4とを覆うように、半導体基板上に設けられたサイドウォール5とを含むゲート構造。

(もっと読む)

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

半導体素子及びその製造方法

【課題】ソース・ドレイン電極及び/又はゲート電極の低抵抗化を図り、微細化・高集積化を損なうことなく、低消費電力で高速操作可能な半導体素子を提供する。

【解決手段】素子分離領域102によりシリコン基板101A表層に画成された素子領域に、チャネル領域を隔てて形成された一対のソース・ドレイン領域106と、ソース・ドレイン領域のそれぞれに導通するソース・ドレイン電極と、チャネル領域上にゲート絶縁膜103を介して形成されたゲート電極と、を備えた半導体素子において、ソース・ドレイン電極及び/又はゲート電極を、ソース・ドレイン領域表面又はゲートを構成するポリシリコン層表面に形成した第1金属膜がシリサイド化されてなるシリサイド層107bと、このシリサイド層上に無電解メッキ法により形成された第2金属膜108と、で構成する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタ製造方法

【課題】ゲート電極材料の耐熱上の問題を克服し、ソース抵抗の低減が可能な電界効果トランジスタを提供する。

【解決手段】ゲート電極9を挟んでソース電極8、ドレイン電極10をそれぞれ形成するソース領域3、ドレイン領域6のいずれか一方または双方の領域にイオンを注入し活性化した第1の高濃度キャリア領域6と、ゲート電極9の直下に形成したチャネル領域4と第1の高濃度キャリア領域6との間の領域に、熱処理によりキャリアを拡散させた熱拡散領域7の第2の高濃度キャリア領域とを形成し、第1の高濃度キャリア領域6は、チャネル領域4と互いに隣接して形成される第2の高濃度キャリア領域7と隣接および/または一部重複し、かつ、チャネル領域4以上に深く形成した第2の高濃度キャリア領域7よりも深く形成する。第1の高濃度キャリア領域6のキャリア濃度を、チャネル領域4よりも高濃度の第2の高濃度キャリア領域7よりさらに高くする。

(もっと読む)

半導体装置

【課題】半導体デバイスに対する多様な要求に対し、柔軟に対応することができる半導体デバイスを提供する。

【解決手段】基板(2)と、ゲート絶縁膜(6)を介して基板(2)の上に設けられるゲート電極(3)と、ゲート電極(3)に隣接して配置されるサイドウォール(5)とを具備する半導体装置(1)を構成する。ゲート電極(3)は、引き出し電極部分(3−2)と実効ゲート電極部分(3−1)とを備えることが好ましい。また、引き出し電極部分(3−2)は、第1方向に沿って延伸する素子分離(9)の上に形成され、第1方向に沿った第1側面(16)(17)を有する部分とする。実効ゲート電極部分(3−1)は、素子分離(9)で分離される領域の上に形成され、第1側面(16)(17)を含む面に交差する面に沿った第2側面を有する部分とする。サイドウォール(5)は、第1側面(16)(17)を覆うことなく第2側面を覆うものとする。

(もっと読む)

半導体装置の製造方法

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体層を有する基板上または基板上に形成されたシリコンを含む導電膜上に、貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、基板に対して熱処理を行って前記貴金属とシリコンとを反応させ、基板上または導電膜上に前記貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて、シリサイド膜のうち未反応の貴金属11の下に位置する部分上に酸化膜12を形成する工程(c)と、第2の薬液を用いて未反応の貴金属を溶解する工程(d)とを備える。

(もっと読む)

半導体装置の製造方法及び設計支援装置

【課題】コンタクト領域の欠損を抑制する技術を提供する。

【解決手段】半導体装置の製造方法は、基板上方に導電膜を形成し、導電膜上に補助パターンを形成し、導電膜及び補助パターンを覆うように金属膜を形成し、金属膜をエッチバックし、補助パターンの側面にサイドウォール膜を形成し、補助パターンを除去し、導電膜及びサイドウォール膜の一部を覆い、一部を露出させるレジストパターンを形成し、レジストパターンをマスクとしてエッチングによりサイドウォール膜の露出している部分を除去し、サイドウォール膜をマスクとして導電膜をエッチングして、ゲート電極及びゲート電極と導通するコンタクト領域を形成し、露出している部分が除去されることにより導電膜上に残存するサイドウォール膜の形状は、ゲート電極及びコンタクト領域の形状に対応し、補助パターンの形状は、コンタクト領域の形状に対応するサイドウォール膜の少なくとも三辺と接する。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】n型MOSトランジスタ、p型MOSトランジスタにおいて共通のゲート絶縁膜構造及びゲート電極材料を用いながら、各々のトランジスタのしきい値電圧を適正な値へ設定し、且つゲート絶縁膜における酸素欠損に伴う移動度の低下を抑制する。

【解決手段】メタルゲート電極及び高誘電率ゲート絶縁膜を用いた半導体装置の製造方法であって、n型半導体領域200及びp型半導体領域300上にそれぞれ、シリコン酸化物からなる第1のゲート絶縁膜、La,Al,Oを含む第2のゲート絶縁膜、Hfを含む第3のゲート絶縁膜を積層し、その上に金属膜からなるゲート電極を形成し、次いでp型半導体領域300上の、第1のゲート絶縁膜,第2のゲート絶縁膜,第3のゲート絶縁膜,及びゲート電極の積層構造を、水素拡散防止膜350で被覆した後、水素雰囲気で熱処理を施す。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

161 - 180 / 769

[ Back to top ]