Fターム[4M104DD68]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | リフトオフ (591)

Fターム[4M104DD68]に分類される特許

61 - 80 / 591

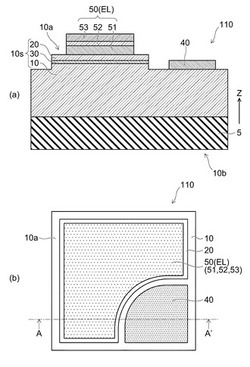

半導体発光素子及び半導体発光装置

【課題】高輝度、高効率、高信頼性を達成する半導体発光素子を提供する。

【解決手段】実施形態に係る半導体発光素子は、積層構造体と、電極と、を備える。積層構造体は、窒化物系半導体からなる第1導電形の第1半導体層と、窒化物系半導体からなる第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、を有する。電極は、第1金属層、第2金属層及び第3金属層を有する。第1金属層は、第2半導体層の発光層とは反対側に設けられ、銀または銀合金を含む。第2金属層は、第1金属層の第2半導体層とは反対側に設けられ、金、白金、パラジウム、ロジウム、イリジウム、ルテニウム、オスミウムの少なくともいずれかの元素を含む。第3金属層は、第2金属層の第1金属層とは反対側に設けられる。第3金属層の第1半導体層から第2半導体層に向かう方向に沿った厚さは、第2金属層の前記方向に沿った厚さ以上である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】イオン注入を用いることなく2次元正孔ガスの所期の濃度分布を容易且つ確実に得て、電界集中のなだらかな緩和を実現する高信頼性の窒化物半導体装置を得る。

【解決手段】n−GaN基板1のN面上に形成されたn−GaN層2と、n−GaN層上に形成されたAlGaNからなるJTE構造10と、n−GaN層2上に形成されたアノード電極4とを有しており、n−GaN層2のJTE構造10との界面に、アノード電極4から離間するほど正孔濃度が低くなるように、2次元正孔ガスが生成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

高耐圧半導体装置

【課題】従来の高耐圧半導体装置の場合よりも耐圧の低下を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタル層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118とを備え、最内周の第1ガードリング層122とエッジターミネーション層120との間隔が3μm〜5μmの範囲内にある高耐圧半導体装置100。

(もっと読む)

化合物半導体装置の製造方法及び洗浄剤

【課題】リセス等の形成に伴う処理で生じる残渣を適切に除去することができる化合物半導体装置の製造方法及び洗浄剤を提供する。

【解決手段】化合物半導体積層構造1を形成し、化合物半導体積層構造1の一部を除去して凹部4を形成し、洗浄剤を用いて凹部4内の洗浄を行う。洗浄剤は、凹部4内に存在する残渣と相溶する基材樹脂と溶媒とを含む。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜を有する窒化物半導体を低コストで製造する。

【解決手段】基板10の上方に形成された半導体層22,23,24と、前記半導体層の一部を酸化することにより形成された絶縁膜30と、前記絶縁膜上に形成された電極41と、を有し、前記絶縁膜は、酸化ガリウムを含むもの、または、酸化ガリウム及び酸化インジウムを含むものにより形成されているものであることを特徴とする半導体装置。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

電子部品の製造方法

【課題】 基板上に、高い精度で、形成不良なく電極を形成し得る電子部品の製造方法を提供する。

【解決手段】 本発明の電子部品の製造方法は、平板状の基板1を準備する基板準備工程と、基板1の主面上にレジストパターン2aを形成するレジストパターン形成工程と、基板1の主面上のレジストパターン2aが形成されていない部分にIDT電極4を薄膜技術により形成する電極形成工程と、レジストパターン2aを除去するレジストパターン除去工程とを含み、電極形成工程は、基板1を、電極が形成される側の主面が凹むように反らせておこなうようにした。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、フィールドプレート構造を絶縁膜の開口中心に対してばらつきなく形成できる半導体装置の製造方法を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、半導体層の表面に絶縁膜を形成する工程と、該絶縁膜の表面に開口を有するレジストを形成する工程と、該レジストと架橋反応するパターンシュリンク剤を該レジストに付着させ、該レジストの内周に硬化層を形成する工程と、該レジスト及び該硬化層をマスクとして該絶縁膜をエッチングする工程と、該硬化層を除去する工程と、該半導体層、該絶縁膜、及び該レジストの表面に金属層を形成する工程と、リフトオフ法により該レジスト及び該レジストの表面の該金属層を除去する工程と、を備えたことを特徴とする。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

パワー半導体素子

【課題】窒化物化合物半導体を用いたパワーダイオード、パワーMOSFET等のパワー

半導体素子について、クラックフリーで形成されて従来よりも厚い窒化物化合物半導体層

を使用して耐圧を向上することである。

【解決手段】シリコン基板1上に厚さ10μm以上の凸状に選択成長された窒化物化合物

半導体からなるキャリア移動層3と、キャリア移動層3上に形成された電極4とを有し、

1つのパワー半導体素子は1つのキャリア移動層3から構成されている。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造工程数を大幅に増加することなく高性能な薄膜トランジスタを備えた薄膜トランジスタ回路基板、及び、薄膜トランジスタ回路基板の製造方法を提供する。

【解決手段】 絶縁基板上に配置されたゲート電極と、前記ゲート電極の上に配置されたゲート絶縁膜と、前記ゲート絶縁膜の上に配置されたポリシリコンによって形成され、前記ゲート電極の直上に位置するチャネル領域、前記チャネル領域に隣接するとともに前記チャネル領域よりも高濃度の不純物を含む低濃度不純物領域、及び、前記低濃度不純物領域に隣接するとともに前記低濃度不純物領域よりも高濃度の不純物を含む高濃度不純物領域を含む半導体層と、前記チャネル領域及び前記低濃度不純物領域の上に配置され、前記チャネル領域の直上の膜厚が前記低濃度不純物領域の直上の膜厚よりも厚い保護膜と、前記高濃度不純物領域に電気的に接続された電極と、を備えたことを特徴とする薄膜トランジスタ回路基板。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】Al原子を有するコンタクト電極が用いられる場合に、絶縁膜の絶縁信頼性を向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】基板面12Bを有する炭化珪素基板10が準備される。基板面12Bの一部を覆うように絶縁膜15が形成される。絶縁膜15に接触するように基板面上にコンタクト電極16が形成される。コンタクト電極16はAl、TiおよびSi原子を含有する。コンタクト電極16は、Si原子およびTi原子の少なくともいずれかと、Al原子とを含有する合金から作られた合金膜50を含む。炭化珪素基板10とコンタクト電極16とがオーミックに接続されるようにコンタクト電極16がアニールされる。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】特性が均一であって、歩留りの高い半導体装置の製造方法を提供する。

【解決手段】第1の半導体層12及び第2の半導体層13が順次形成されている半導体層の表面にレジストパターンを形成する工程と、前記レジストパターンの開口領域における前記第2の半導体層の一部または全部をドライエッチングにより除去しゲートリセス22を形成する工程と、前記レジストパターンを除去した後、ゲートリセスの底面及び側面に付着しているドライエッチング残渣23を除去する工程と、前記ドライエッチング残渣を除去した後、前記ゲートリセスの底面、側面及び前記半導体層上に絶縁膜31を形成する工程と、前記ゲートリセスが形成されている領域に前記絶縁膜を介しゲート電極を形成する工程と、前記半導体層上にソース電極及びドレイン電極を形成する工程と、を有する。

(もっと読む)

半導体エピタキシャル結晶基板及びその製造方法

【課題】高性能の窒化ガリウム系トランジスタを製造するための、誘電体膜付の半導体エ

ピタキシャル結晶基板を提供すること。

【解決手段】下地基板1上にエピタキシャル法によって、バッファ層2、チャネル層3、

及び電子供給層4から成る窒化ガリウム半導体結晶層を形成した後、エピタキシャル成長

炉内で連続してAlNを電子供給層4上に誘電体膜の前駆体として積層し、しかる後、積

層した前駆体に対して酸化処理を施すことによって誘電体膜5を形成する。

(もっと読む)

61 - 80 / 591

[ Back to top ]