Fターム[4M104DD68]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | リフトオフ (591)

Fターム[4M104DD68]に分類される特許

161 - 180 / 591

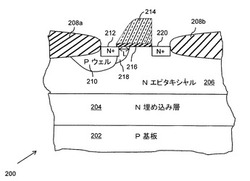

非対称スペーサをゲートとして備えるLDMOSトランジスタ

【課題】本発明は、横方向拡散金属酸化物半導体(LDMOS)トランジスタと、これを製造する方法を提供する。

【解決手段】LDMOSトランジスタはp型基板上に形成されたn型エピタキシャル層と、LDMOSトランジスタのゲートとして機能する非対称導体スペーサとを備える。LDMOSトランジスタはまた、非対称導体スペーサの両側のソース領域及びドレイン領域と、イオン注入を非対称導体スペーサに行うことで形成されたチャネル領域とを備える。非対称導体スペーサの高さはソース領域からドレイン領域に向かって増加する。チャネル領域は、基本的に完全に非対称導体スペーサの下に存在し、従来技術のLDMOSトランジスタのチャネル領域の長さよりも短い長さを有する。本発明のLDMOSトランジスタはまた、当該トランジスタの活性領域を囲むフィールド酸化物層と、非対称導体スペーサをn型エピタキシャル層から絶縁する薄い誘電体層とを備える。

(もっと読む)

リフトオフ装置およびリフトオフ処理方法

【課題】シリコン基板からの被覆物の除去処理を短時間化できる上、バリ発生のない高品質なパターン生成を行うことができるようにする。

【解決手段】フォトレジストに対して溶解性がない純水200中にシリコン基板100を浸漬させた状態で、ホーン型超音波発生器20から純水200を介してシリコン基板100に対して強力な超音波を照射することにより、金属膜の殆ど全てとフォトレジストの一部とを金属疲労の原理により、バリの発生もなく短時間で除去することができようにするとともに、金属膜を除去した後、フォトレジストに対して溶解性のあるIPAを用いることによって、残ったフォトレジストを完全に除去する。

(もっと読む)

半導体発光素子および半導体発光素子の製造方法

【課題】2つの電極の構造を共通にして構成の簡易化を図るとともに、各電極の接合性を向上させつつ、半導体発光素子の電気的特性の低下を抑制する。

【解決手段】半導体発光素子1は、n型半導体層140、発光層150、p型半導体層160、透明電極170、透明電極170に形成されるp側電極300、n型半導体層140に形成されるn側電極400を備える。p側電極300は、透明電極170に積層されるp側接合層310およびp側ボンディングパッド電極320を備え、n側電極400は、n型半導体層140に積層されるn側接合層410およびn側ボンディングパッド電極420を備える。p側接合層310およびn側接合層410はTaNとPtとの混在層で構成され、p側ボンディングパッド電極320およびn側ボンディングパッド電極420はPtとAuとの積層構造で構成される。

(もっと読む)

薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法

【課題】ソース−ドレイン間等の電圧−電流特性を改善することができる薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法を提供する。

【解決手段】薄膜トランジスタ100は、半導体膜119と、半導体膜119の上方に形成されたソース電極層140と、半導体膜119の上方に形成されたドレイン電極層142と、ソース電極層140とドレイン電極層142との間、かつ、半導体膜119の上方に形成されたチャネル保護膜113と、を備える薄膜トランジスタであって、ソース電極層140とドレイン電極層142の少なくとも何れか一方は、チャネル保護膜113と接し、その上面がチャネル保護膜113の上面を超えない接触領域を有して、チャネル保護膜113の上面と重なっていない。

(もっと読む)

自己整列グラフェン・トランジスタ

【課題】自己整列グラフェン・トランジスタを作製するスキームを提供する。

【解決手段】グラフェン電界効果トランジスタは、ゲート・スタックであってシード層とシード層の上に形成されたゲート酸化物とゲート酸化物の上に形成されたゲート金属とを含む該ゲート・スタック、絶縁層、およびシード層と絶縁層との間に転写されたグラフェン・シート、を含む。

(もっと読む)

半導体装置の製造方法

【課題】n型SiC領域とp型SiC領域との両方と接触可能であり、かつ酸化による接触抵抗の増加を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、炭化珪素からなるn−SiC層12を準備する工程と、n−SiC層12の主表面上にソースコンタクト電極16を形成する工程とを備えるMOSFET1の製造方法である。ソースコンタクト電極16を形成する工程は、ソースコンタクト電極16となるべき導電体層をn−SiC層12の主表面上に形成する工程と、導電体層をソースコンタクト電極16とするため熱処理する工程とを含む。熱処理する工程の後、ソースコンタクト電極16の表面を酸素含有雰囲気に曝露するときのソースコンタクト電極16の温度を100℃以下にする。ソースコンタクト電極16を形成する工程の後、表面電極パッド27を形成する工程の前に、上記ソースコンタクト電極16の一方の主面上に形成された高抵抗層を除去する工程を含むことがより好ましい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリセス構造を採用してノーマリーオフ動作を可能とするも、バラツキの小さい安定した閾値を有し、十分な高耐圧を実現する信頼性の高い化合物半導体装置を実現する。

【解決手段】電子走行層3と電子供給層4との間にi−AlNからなる中間層5を形成し、キャップ構造7上のゲート電極の形成予定部位に中間層5をエッチングストッパとして用いて開口11aを形成した後、中間層5の開口11aに位置整合する部位に熱リン酸を用いたウェットエッチングにより開口11bを形成して、開口11a,11bからなる開口11をゲート絶縁膜12を介して下部が埋め込み、上部がキャップ構造7上方に突出するゲート電極13を形成する。

(もっと読む)

半導体発光装置の製造方法

【課題】

半導体膜をパターニングする際に行われるウェットエッチングに対して十分な耐性を有するマスクを形成することにより、半導体膜のパターニングを適切に行うことができる半導体発光装置の製造方法を提供する。

【解決手段】

成長用基板の上に半導体膜を形成する。半導体膜の表面である−C面に凹凸を形成する。銀または銀を90%以上含む合金からなり、半導体膜の凹凸面の一部を覆う金属膜を形成する。金属膜から露出した半導体膜の少なくとも一部をウェットエッチングにより除去する。半導体膜の凹凸の深さ寸法は、前記金属膜の厚さよりも大きく設定する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のテーパ形状の傾斜度を緩やかにすることができるようにして、ゲート電極の破損が起こらないようにしながら、確実にさらなる微細化を実現した下部電極を形成できるようにする。

【解決手段】ソース電極2及びドレイン電極3を有する半導体領域1上に絶縁膜4を形成し、絶縁膜4上に複数のレジスト層5,6,7を含む積層レジスト8を形成し、積層レジスト8の最下層以外のレジスト層6,7に開口9を形成し、最下層のレジスト層5にリフロー用開口10を形成し、熱処理を施してリフロー用開口10に露出している最下層のレジスト層5の一部PTcをリフローさせ、リフローさせることによって最下層のレジスト層5の表面に形成された傾斜面11に連なるように最下層のレジスト層5に第1ゲート下部開口12Aを形成し、開口9、傾斜面11及び第1ゲート下部開口12Aの形状に応じた形状を持つゲート電極13を形成する。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧を向上できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1の絶縁層13と第2の絶縁層14と電極層とFP電極17とを備えている。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成されている。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成されている。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成されている。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成されている。第1の絶縁層13の厚みH13は、第2の絶縁層14の厚みH14よりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応答特性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1および第2の絶縁層13、14と電極層とFP電極17とを備える。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成される。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成される。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成される。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成される。第1の絶縁層13は、第2の絶縁層14を構成する材料の誘電率よりも小さい誘電率を有する材料を含む。

(もっと読む)

半導体素子およびその製造方法

【課題】ウェットエッチングにより形成される配線の線幅のばらつきが抑えられた半導体素子を提供する。

【解決手段】半導体素子の製造方法は、半導体層14上に電極11を形成する工程と、半導体層14上に、電極11に達する配線接続孔12aを有し、配線接続孔12aの周りに凹部12bが形成された層間絶縁膜12を形成する工程と、層間絶縁膜12上から配線材料18を堆積する工程であって、層間絶縁膜12の凹部12bに対応して配線材料18に凹部18aが形成される工程と、配線材料18上に、電極11に配線接続孔12aを介して接続される配線13を形成するためのレジスト膜19を、配線材料18に形成された凹部18aを覆うように形成する工程と、レジスト膜19をマスクとしてウェットエッチングを行い、配線材料18を選択的に除去して配線13を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、Au配線との密着性が強く、より高い熱的安定性を有するバリアメタル層を実現し、更なる特性向上、歩留まり向上を実現する。

【解決手段】半導体装置を、Al層8を含む電極9,10と、Au配線12と、Al層8とAu配線12との間に設けられ、Al層8の側から順に第1Ta層14、第1TaN層15、第1Pt層16を積層した構造を有するバリアメタル層11とを備えるものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極からチャネル層までの距離のばらつきが低減されたHEMT半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、リセスエッチング工程後に酸化膜形成工程を行う。リセスエッチングを行った後に、HEMT構造基板の加熱や過酸化水素への浸漬によって、強制的に酸化膜6’’及び7’’を形成する。このような酸化膜6’’及び7’’は、面内均一性に優れ、かつ、ある厚さで安定するため、大気中に暴露してもそれ以上酸化は進まない。酸化膜6’’及び7’’は、例えば、濃度3%の過酸化水素水にHEMT構造基板を3分間浸漬させることや、120℃のホットプレート上で2分間HEMT構造基板を加熱させることにより形成することができる。

(もっと読む)

電界効果型トランジスタ

【課題】チャネル領域を構成する有機半導体材料層と良好なオーミック・コンタクトを形成することができるソース/ドレイン電極を備えた電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、ゲート電極12と、ゲート絶縁層13と、ソース/ドレイン電極21と、チャネル領域15を構成する有機半導体材料層14とを備え、ソース/ドレイン電極21は、金属から成る導体部22、及び、導体部22を少なくとも部分的に被覆し、不純物がドーピングされた有機導電材料層23から成り、有機導電材料層23を介して、チャネル領域15と導体部22との間の電気的接続が形成される。

(もっと読む)

半導体発光素子、その製造方法、ランプ、電子機器及び機械装置

【課題】金属反射層の構成材料の拡散を防止することが可能な電極を備えた半導体発光素子、その製造方法、ランプ、電子機器及び機械装置を提供することを目的とする。

【解決手段】基板101と、基板101上にn型半導体層104と発光層105とp型半導体層106とがこの順序で積層されてなる積層半導体層20と、p型半導体層106に接合された一方の電極111と、n型半導体層104に接合された他方の電極108と、を具備する半導体発光素子であって、一方の電極111または他方の電極108のいずれか一方または両方が、第1の拡散防止層51と金属反射層52と第2の拡散防止層53がこの順序で積層されてなる構造を有し、かつ、第1の拡散防止層51がIn、Zn、Al、Ga、Ti、Bi、Mg、W、Ce、Sn、Niのいずれかの金属を含む酸化物からなる半導体発光素子1を用いることにより、上記課題を解決できる。

(もっと読む)

リフトオフ法を用いたパターン形成方法

【課題】本発明は、リフトオフ法を用いたパターン形成方法を実施したとしても、導電性パターンのエッジ付近にバリが発生することがない、リフトオフ法を用いたパターン形成方法を提供する。

【解決手段】本発明では、まず、導電性パターン6のエッジ部が位置するウエハ基板1の表面内に、溝2を形成する。次に、溝2が露出する開口部3aを有するレジスト3を、ウエハ基板1上に形成する。次に、開口部3aから露出するウエハ基板1上とレジスト3上とに、導電性膜5を形成する。そして、レジスト3を除去することにより、ウエハ基板1上に導電性パターン6を形成する。

(もっと読む)

161 - 180 / 591

[ Back to top ]