Fターム[4M104DD68]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | リフトオフ (591)

Fターム[4M104DD68]に分類される特許

201 - 220 / 591

金属薄膜の製造方法および半導体装置の製造方法

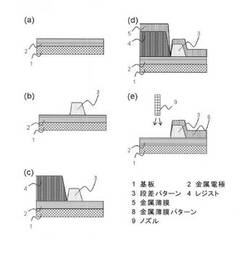

【課題】金属薄膜パターンの端部におけるバリ発生を確実に防止できる金属薄膜の製造方法および半導体装置の製造方法を提供する。

【解決手段】本発明は、所定パターンの金属薄膜パターン8を形成するための方法であって、下地の上に、前記パターンのエッジに対応する位置近傍に壁面を有する段差パターン3を形成する工程と、段差パターン3を含む下地全体にレジスト4を塗布する工程と、塗布したレジスト4に対して、前記パターンの反転パターンとなるようにパターニングを施す工程と、レジスト4および段差パターン3を含む下地全体に金属薄膜5を形成する工程と、溶剤を塗布して、レジスト4および該レジスト4上に位置する金属薄膜5を除去する工程とを含む。

(もっと読む)

電子デバイスの製造方法

【課題】可撓性を有する電子デバイスを、素子の劣化を防いで簡易に且つ短時間で製造することができる電子デバイスの製造方法を提供する。

【解決手段】支持基板12上に、特定の刺激によって発泡する発泡材を含む剥離層14を形成する工程と、前記剥離層上に電子デバイスを構成する素子を含む構造体11を形成する工程と、前記剥離層に前記特定の刺激を加えることにより該剥離層に含まれる前記発泡材を発泡させ、該剥離層を介して前記構造体を前記支持基板から剥離させる工程と、を有する電子デバイス10の製造方法。好ましくは、発泡材として熱膨張性マイクロカプセル15を用いる。

(もっと読む)

半導体素子

【課題】 従来のダイオードでは、微小な電圧領域では、十分な検波特性が得られない。

【解決手段】 電子及び正孔が、ダイレクトトンネル現象により透過可能な厚さの空乏層を挟んでp型半導体層及びn型半導体層が相互に接合されている。n型半導体層とp型半導体層との間に、両者のエネルギバンドがフラットになるフラットバンド電圧を印加した状態で、n型半導体層の禁制帯とp型半導体層の禁制帯とが部分的に重なる。電圧無印加時の平衡状態で、空乏層に連続するエネルギバンドの曲がり部よりも空乏層から離れた領域において、p型半導体層の価電子帯上端の電子のエネルギレベルが、n型半導体層の伝導帯下端の電子のエネルギレベルと同等か、またはそれよりも高い。

(もっと読む)

薄膜トランジスタおよび該薄膜トランジスタの製造方法

【課題】低温で簡便なプロセスにより形成可能で、移動度、on/off比に優れ、立ち上がり電圧のマイナス側へのシフト、S値劣化、素子間の性能バラツキを改良した、安定性の高い薄膜トランジスタ、および該薄膜トランジスタの製造方法を提供する。

【解決手段】基板106上にゲート電極104、ゲート絶縁層105、ソース電極102、ドレイン電極103、及び半導体層101を有する薄膜トランジスタにおいて、半導体層101が塗布によって形成された酸化物半導体からなり、フッ素化合物含有層107がゲート電極104と半導体層101との間に設けられる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】NチャネルMOSFETとPチャネルMOSFETを備える半導体装置において、PチャネルMOSFETの閾値電圧のばらつきを抑制し、製造歩留まりを上げる。

【解決手段】半導体基板103の上にゲート絶縁膜110A、110Bを形成した後、PチャネルMOSFET形成領域107に形成されたゲート絶縁膜110Bを第一マスク111で覆う。次に、NチャネルMOSFET形成領域106およびPチャネルMOSFET形成領域107に第一金属層112を形成し、PチャネルMOSFET形成領域107から第一金属層112および第一マスク111を除去することにより、PチャネルMOSFET形成領域107に形成されたゲート絶縁膜110Bを露出させる。その後、NチャネルMOSFET形成領域106およびPチャネルMOSFET形成領域に107ゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】少ない工程数で製造可能であり、かつゲート電極付近の電界集中を緩和させる。

【解決手段】下地11上に第1及び第2絶縁膜13及び15を順次形成し、第2絶縁膜に表面から第1開口パターン、及び第1絶縁膜を露出させ、かつ第1開口パターンよりも開口端の第1方向に沿った長さが短い第2開口パターンを形成し、第1開口パターンを厚み方向に沿って拡大することによって第1開口部19、第1及び第2開口パターンからの露出面から第1絶縁膜を部分的に除去することによって、第1開口部から連続し、かつ第1開口部19よりも開口端の第1方向に沿った長さが短い第2開口部21、及び第2開口部から連続した、下地面を露出させ、かつ第2開口部よりも開口端の第1方向に沿った長さが短い第3開口部23を形成し、第1〜第3開口部を含む電極形成用開口部17を埋め込むとともに、電極形成用開口部周辺の第2絶縁膜の表面を被覆する電極を形成する。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域AA上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、窒化物系化合物半導体層12上に配置され、それぞれゲート電極24、ソース電極20およびドレイン電極22に接続されたゲート端子電極GE1〜GE3、ソース端子電極SE1〜SE4およびドレイン端子電極DEと、ソース端子電極が配置される側の基板の端面に配置され、ソース端子電極と接続された端面電極SC1〜SC4と、端面電極上に配置され、ダイボンディングで使用する半田層がソース端子電極SE1〜SE4に到達するのを防止する突起電極34とを備える半導体装置およびその製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明によれば、SiCを用いた微細化可能で、超低オン抵抗、かつ信頼性にも優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】炭化珪素基板と、その第1の主面の第1導電型の第1の炭化珪素層と、この表面の第2導電型の第1の炭化珪素領域と、この表面の第1導電型の第2の炭化珪素領域と、その下部の第2導電型の第3の炭化珪素領域と、第2の炭化珪素領域を貫通し、第3の炭化珪素領域に達するトレンチと、ゲート絶縁膜と、ゲート電極と、ゲート電極を被覆する層間絶縁膜と、トレンチ側面の第2の炭化珪素領域上および層間絶縁膜上に形成されたNi、Ti、Ta、MoおよびWからなる群から選択される金属元素を含有する第1の電極と、トレンチ底部の第3の炭化珪素領域上および第1の電極上に形成されたAlを含有する第2の電極と、第2の電極上の第1の主電極と、炭化珪素基板の第2の主面に形成された第2の主電極と、を有する半導体装置。

(もっと読む)

電極の形成方法及び発光素子の製造方法ならびに半導体素子及び発光素子

【課題】蒸着の回数などの工程数増加によるコストも抑えることができ、また電極のめくれ、ハガレの不良の発生を防ぐことを考慮しつつ、LEDランプ組立工程でのワイヤーボンド部のワイヤーと電極と間の圧着部分の密着強度の強い電極の形成方法を提供する。

【解決手段】少なくとも、n型半導体結晶と発光層とp型半導体結晶とがこの順で形成された半導体結晶にオーミック電極を形成する方法であって、半導体結晶のp型半導体結晶の表面上に、少なくとも、第一金属層としてAuを蒸着させ、第一金属層上に第二金属層としてAuBe合金材料とAuの混合物を蒸着させてAuBe合金を形成し、第二金属層上に第三金属層としてAuを蒸着させ、その後熱処理を行ってオーミック電極を形成することを特徴とする電極の形成方法。

(もっと読む)

リフトオフ方法及び薄膜トランジスタの製造方法

【課題】歩留まりの低下を防止して、製造工程の簡素化を図ることが可能になるとともに、製造コストの低減を図ることができる表示装置及びその製造方法を提供することを目的とする。

【解決手段】半導体ナノワイヤ3とリフトオフレジスト12と金属膜13とが形成された基板1を、気体のマイクロバブルが混合された液体により構成された剥離液に浸漬させることにより、リフトオフレジスト12とともにリフトオフレジスト12上の金属膜13を剥離して、基板2上に金属膜13からなる所定のパターンを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容易にノーマリオフ特性を向上させることができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、一方の主面5aの一部に凹部16が形成された窒化物系半導体層3〜5と、一方の主面5aに設けられたソース電極7と、凹部16を挟みソース電極7とは反対側であって、一方の主面5aに設けられたドレイン電極8と、一方の主面5aの凹部16を挟み両側に形成され、凹部16側の壁面17が傾斜した絶縁層6と、凹部16の底面16a上及び側面16b上並びに絶縁層6の凹部16側の壁面17上に設けられたゲート電極10とを備えている。絶縁層6の壁面17の傾斜角βは、凹部16の側面16bの傾斜角αよりも大きい。

(もっと読む)

薄膜トランジスタアレイの製造方法及び表示装置

【課題】ソース電極とドレイン電極を均一且つ効率的に製造でき、薄膜トランジスタの半導体特性を低下させない薄膜トランジスタアレイ及びその製造方法を提供する。

【解決手段】基板1上にスキャンライン2を形成する工程と、外部接続用開口部11以外の領域に絶縁層2を形成する工程と、塗布型電極材料を全面に塗布、焼成して塗布電極層を形成した後にエッチングして少なくともソース電極4s及びドレイン電極4dを形成する工程と、ソース電極4s及びドレイン電極4dとを跨ぐ半導体層5を形成する工程と、封止層6を、外部接続用開口部11に露出しているスキャンライン2a上には少なくとも形成しないようにして形成する工程と、封止層6上に表示電極層8を形成した後にエッチングして表示電極8を形成する工程とを有する。この場合において、表示電極形成時のエッチングにより、外部接続用開口部11に露出しているスキャンライン2a上に残った余分な塗布電極層を除去する。

(もっと読む)

電界効果トランジスタ、および、その製造方法

【課題】従来よりもゲート寸法が縮小され、高周波性能の高い電界効果トランジスタを、均一なゲート寸法でかつ低コストで提供すること。

【解決手段】ゲート電極を形成するための開口部を設ける工程において、投影露光装置を用いて、レジストを露光して前記開口部を作成する際に、露光されるレジストにおいて、該露光により形成される半導体基板上での開口部の幅が、レチクルおよび露光装置の縮小比によって規定されるウエハー上での光束寸法よりも小さな幅として形成されるように、ソース電極およびドレイン電極の厚さを、それぞれ所定の値に設定する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながら、高いドレイン電流を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたソース電極5s、ドレイン電極5d及びゲート電極5gと、が設けられている。更に、ソース電極5sとゲート電極5gとの間の化合物半導体積層構造2上に形成され、シリコンを含む第1の保護膜6と、ドレイン電極5dとゲート電極5gと間の化合物半導体積層構造2上に形成され、第1の保護膜6より多くシリコンを含む第2の保護膜7と、が設けられている。

(もっと読む)

透明導電膜のパターニング方法及び該方法による透明導電パターン膜

【課題】

透明導電膜の微細パターニングを可能とするリフトオフ法によるパターニング方法、及び該パターニング方法を用いて形成された透明導電パターン膜を提供する。

【解決手段】

基材上に有機溶媒可溶性でかつ水不溶性のフォトレジストパターンを形成するパターンレジスト形成工程、前記フォトレジストパターンが形成された基材上の全面に導電性酸化物微粒子と無機バインダーと溶媒とからなる透明導電膜形成用塗布液を塗布、乾燥、硬化して導電性酸化物微粒子と無機バインダーマトリックスを主成分とする透明導電膜を形成する透明導電膜形成工程、前記フォトレジストパターンを有機溶媒で溶解除去による現像をすることでフォトレジストパターン上に形成された透明導電膜を除去して透明導電パターン膜を得る透明導電膜パターニング工程を具備し、前記透明導電膜形成用塗布液の溶媒は、水又は水−アルコール混合溶液を主成分とすることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】窒化物半導体層を有する半導体装置を低コストで製造する。

【解決手段】基板上に第1の窒化物半導体の犠牲層を形成する犠牲層形成工程と、前記犠牲層上に第2の窒化物半導体層を形成し、前記第2の窒化物半導体層上に窒化物半導体層を積層した積層窒化物半導体層を形成する積層半導体形成工程と、前記犠牲層の表面が露出するまで、前記第2の窒化物半導体層及び前記積層窒化物半導体層をエッチングすることによりトレンチを形成し、前記トレンチ及び前記積層窒化物半導体層表面に接続電極を形成する接続電極形成工程と、前記接続電極の形成された前記基板を電解液に浸漬させ、前記電解液に対し前記接続電極に電位を印加し、前記犠牲層を除去し前記基板を剥離する犠牲層除去工程とを有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

紫外光発光ダイオード装置及びその製造方法

本発明は、UVLED装置及びその製造方法を提供する。この装置は、基板(1)上に下から上への順で設けられたAlN核層(2、3)、真性AlGaNエピタキシャル層(4)、n−型AlGaNバリア層(5)、活性領域(6)、第1のp−型AlGaNバリア層(7)、第2のp−型AlGaNバリア層(8)、及びp−型GaNキャップ層(9)を含備える。p−型GaNキャップ層には、発生した光を発するためのウインド領域(10、W、A)をエッチングしている。 (もっと読む)

化合物半導体装置及びその製造方法

【課題】大きなドレイン電圧が印加された場合のドレインリーク電流を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層3と、電子走行層3上方に形成され、AlGaNを含む電子供給層4及び5と、電子供給層4及び5上に形成され、InAlNを含むショットキーバリア層6と、が設けられている。ショットキーバリア層6を構成する結晶の格子定数は、電子供給層4及び5を構成する結晶の格子定数よりも大きく、ショットキーバリア層6を構成する材料のバンドギャップは、電子供給層4及び5を構成する材料のバンドギャップよりも大きい。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

201 - 220 / 591

[ Back to top ]