Fターム[4M104DD68]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | リフトオフ (591)

Fターム[4M104DD68]に分類される特許

141 - 160 / 591

半導体発光装置

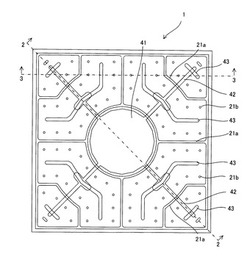

【課題】局所的な電流集中を防止して均一な発光分布を得ることができる半導体発光装置を提供する。

【解決手段】半導体発光装置は、支持基板と、支持基板上に設けられた光反射性を有する反射電極と、反射電極上に設けられた発光層を含むAlGaInP系半導体膜と、半導体膜上に設けられた表面電極と、を含む。表面電極は、半導体膜上に分散配置された複数の電極片からなるオーミック電極を含む。反射電極は、オーミック電極を構成する電極片の各々を挟んだ両側において電極片に沿うように設けられた線状のライン電極および複数の島状のドット電極からなる。ライン電極とドット電極との距離をa、オーミック電極とドット電極の水平距離をb、互いに隣接するドット電極間の距離をcとしたときに、b>a且つ0.8(a2+2ab)1/2<c<2.4(a2+2ab)1/2を満たすように表面電極および反射電極が配設される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

窒化物半導体素子および窒化物半導体素子のパッド電極の製造方法

【課題】p型窒化物半導体層上の透光性電極とn型窒化物半導体層との両方に好適に接続可能な構造のパッド電極を備える窒化物半導体素子を提供する。

【解決手段】窒化物半導体素子10は、基板1上に、n型窒化物半導体層2、活性層3、p型窒化物半導体層4を積層してなり、n型、p型窒化物半導体層2,4にそれぞれ電気的に接続するn側パッド電極7n、p側電極5をさらに備える。p側電極5は、p型窒化物半導体層4上に形成された導電性酸化物からなる透光性電極6と、透光性電極6上の一部の領域に形成されたp側パッド電極7pとからなる。そして、n側パッド電極7nおよびp側パッド電極7pは、n型窒化物半導体層2および透光性電極6のそれぞれに接触する側から、Cr層71a、Pt層71b、Ru層72、Au層73を積層してなり、Cr層71aの厚さは1nm以上9nm未満であることを特徴とする。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

III族窒化物系半導体素子

【課題】III族窒化物系半導体領域の表面がc面から傾斜している場合に、該半導体層上に設けられる電極と該半導体領域との接触抵抗を小さく抑えることが可能なIII族窒化物系半導体素子を提供する。

【解決手段】III族窒化物系半導体素子は、III族窒化物結晶からなる非極性表面13aを有する半導体領域13と、半導体領域13の非極性表面13aに設けられた金属電極17とを備え、非極性表面13aは半極性及び無極性のいずれかであり、半導体領域13にはp型ドーパントが添加されており、半導体領域13のIII族窒化物結晶と金属電極17との間に、金属電極17の金属と半導体領域13のIII族窒化物とが相互拡散して成る遷移層19を有する。

(もっと読む)

窒化物半導体装置

【課題】パワートランジスタに適用可能なノーマリオフ型の窒化物半導体装置に生じる電流コラプスを抑制できるようにする。

【解決手段】窒化物半導体装置は、サファイアからなる基板11と、該基板11の上に形成されたGaNからなるチャネル層13と、該チャネル層13の上に形成され、該チャネル層13よりもバンドギャップエネルギーが大きいAlGaNからなるバリア層14と、該バリア層14の上に形成され、p型AlGaN層15及びp型GaN層16を含むp型窒化物半導体層と、該p型窒化物半導体層の上に形成されたゲート電極19と、該ゲート電極19の両側方の領域にそれぞれ形成されたソース電極17及びドレイン電極18とを有している。p型窒化物半導体層は、ゲート電極19の下側部分の厚さが該ゲート電極19の側方部分の厚さよりも大きい。

(もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

窒化物半導体装置

【課題】高電圧印加時にフィールドプレート構造端に集中する電界強度を緩和し、高耐圧で信頼性の高い窒化物半導体装置を提供する。

【解決手段】フィールドプレート構造を備えた窒化物半導体装置において、ゲート電極18に、オフ制御の制御電圧を印加するとき、フィールドプレート構造の傾斜面部直下の窒化物半導体層中13にはキャリアが存在しないようにする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

パターン形成方法、及び半導体装置の製造方法

【課題】下地の性能を犠牲にすることなく、リフトオフ層が下地から剥離することを防止できるパターン形成方法、及び半導体装置の製造方法を提供すること。

【解決手段】本発明にかかるパターン形成方法は、基板上にカバー絶縁膜22を形成し、第1のレジストパターン104をマスクとして、金属膜パターン形成領域を取り囲むようカバー絶縁膜22に凹部103を形成する工程と、凹部103内に入り込むよう、カバー絶縁膜22上にリフトオフ層となる第2のレジストパターン25を形成する工程と、第2のレジストパターン25をマスクとして、金属膜パターン形成領域のカバー絶縁膜22に開口部を形成する工程と、第2のレジストパターン25の上から基板表面に金属膜を成膜し、第2のレジストパターン25とともに第2のレジストパターン25上の金属膜を除去して金属膜パターンを形成する工程とを備えるものである。

(もっと読む)

化合物半導体装置の製造方法

【課題】高い信頼性を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体層1上に、高融点金属を含む第1の導電膜3を形成する。第1の熱処理を行うことにより、第1の導電膜3と窒化物半導体層1とを反応させて高融点金属の窒化物層4を形成すると共に、窒化物半導体層1の表面に窒素空孔を生じさせる。第1の導電膜2上に、Alを含有する第2の導電膜3を形成する。第2の熱処理を行うことにより、第2の導電膜3中のAl原子を窒化物半導体層1の表面まで拡散させる。

(もっと読む)

窒化物系ダイオード

【課題】高耐圧でかつ低オン電圧動作が可能な窒化物系ダイオードを提供する。

【解決手段】窒化物系ダイオード10は、シリコン基板11の(111)面上に形成されたバッファ層12と、アンドープのGaNからなるチャネル層13と、チャネル13層上に形成されたアンドープのAlGaNからなる電子供給層14と、電子供給層14上に形成されたカソード電極15およびアノード電極16とを備える。窒化物系ダイオード10はさらに、電子供給層14を、チャネル層13に達する深さまで部分的に除去したメサ18を備え、メサ18の一方の側面部18aにアノード電極16が接触している。アノード電極16がメサ18の側面部18aに接触することで、アノード電極16と2次元電子ガス層17とが電気的に接続されている。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の上昇を抑制しつつ閾値電圧を大きくできる電界効果トランジスタを提供する。

【解決手段】キャリア走行層13である第1窒化物半導体層13と、第1窒化物半導体層13の上に設けられた、第1窒化物半導体層よりもバンドギャップエネルギーの大きい第2窒化物半導体層14と、第2窒化物半導体層14の上に順に設けられた、InGaN16層と、p型窒化物半導体層18と、ゲート電極22とを備える電界効果トランジスタであって、InGaN層16は、ゲート電極22直下の表面に第1の凹部19を有する。これにより、オン抵抗を一定に抑えつつ、閾値電圧を大きくすることができ、ノーマリオフ型のトランジスタが実現できる。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

窒化物系化合物半導体装置、及びその製造方法

【課題】オーミック電極のオーミックコンタクト抵抗を確実に低減させる。

【解決手段】各オーミック電極3、4は、GaNキャップ層26表面のリセス28周辺部位に接触する第1電極51と、第1電極51に接触して、リセス28を介して2次元電子ガス層27に及ぶ第2電極52とを有している。第1電極51は、リセス28の開口部を囲む環状のものである。第2電極52は、第1電極51に重なる頭部52a、及びリセス28内に形成された柱状部52bからなる。第1及び第2電極51、52を第1及び第2温度でそれぞれ熱処理しているので、第1及び第2電極51、52のオーミックコンタクト抵抗を共に低減させ、各オーミック電極3、4そのもののオーミックコンタクト抵抗を低減させることができる。

(もっと読む)

半導体装置

【課題】GaN電子走行層、AlGaN電子供給層、およびGaNキャップ層が順次積層された半導体装置において、高周波数動作および高出力動作を実現することが可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に順次積層されたGaN電子走行層12、AlGaN電子供給層14、およびGaNキャップ層16と、GaNキャップ層16上に形成されたゲート電極18と、ゲート電極18の両側であって、AlGaN電子供給層14上に形成されたソース電極20およびドレイン電極22と、ゲート電極18とソース電極20との間のGaNキャップ層16に形成された第1の凹部30と、を具備し、第1の凹部30が有する底面32下におけるGaNキャップ層16の厚さは、ゲート電極18下におけるGaNキャップ層16の厚さに比べて薄い半導体装置である。

(もっと読む)

非対称スペーサをゲートとして備えるLDMOSトランジスタ

【課題】本発明は、横方向拡散金属酸化物半導体(LDMOS)トランジスタと、これを製造する方法を提供する。

【解決手段】LDMOSトランジスタはp型基板上に形成されたn型エピタキシャル層と、LDMOSトランジスタのゲートとして機能する非対称導体スペーサとを備える。LDMOSトランジスタはまた、非対称導体スペーサの両側のソース領域及びドレイン領域と、イオン注入を非対称導体スペーサに行うことで形成されたチャネル領域とを備える。非対称導体スペーサの高さはソース領域からドレイン領域に向かって増加する。チャネル領域は、基本的に完全に非対称導体スペーサの下に存在し、従来技術のLDMOSトランジスタのチャネル領域の長さよりも短い長さを有する。本発明のLDMOSトランジスタはまた、当該トランジスタの活性領域を囲むフィールド酸化物層と、非対称導体スペーサをn型エピタキシャル層から絶縁する薄い誘電体層とを備える。

(もっと読む)

141 - 160 / 591

[ Back to top ]