Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

401 - 420 / 542

半導体装置の製造方法

【課題】ゲートリーク電流の発生や短絡等のような特性の劣化が抑制された半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、位相シフタを備える露光用マスクを用いてレジスト膜を露光現像することにより、前記レジスト膜をパターニングする工程と、第2レジスト膜118をマスクとし第2の膜(シリコン酸化膜108)をエッチングストッパとして第3の膜(多結晶シリコン膜)を選択的にドライエッチングし、第3の膜を第1のパターンに加工する工程と、前記第2の膜をエッチングストッパとして第3の膜(多結晶シリコン膜110a)をさらにドライエッチングし、前記第3の膜の一部を除去して前記第3の膜を第2のパターンに加工する工程と、前記第2のパターンに加工された第3の膜(多結晶シリコン膜110b)をマスクとして用いる工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】導電体と電気的に接続される配線パターンを備えた半導体装置の製造方法に関し、接続孔の形状ばらつきを抑制すると共に、製造コストを低減することのできる半導体装置の製造方法を提供する。

【解決手段】第1の開口部を有するレジスト膜24をマスクとする異方性ドライエッチングにより、絶縁膜13に凹部を形成し、その後、第1の開口部の側壁を形成するレジスト膜24を後退させて、第1の開口部よりも直径の大きい第2の開口部27を形成し、続いて、第2の開口部27が形成されたレジスト膜24をマスクとする異方性ドライエッチングにより、拡散層が露出するまで絶縁膜13をエッチングして、接続孔を形成する。

(もっと読む)

表示装置とその製造方法

【課題】TFT基板に形成する薄膜トランジスタのゲート絶縁膜を高誘電率材料を用いた厚膜とし、かつ十分なイオンをドーピングする。

【解決手段】膜厚が厚い高誘電率材料からなるゲート絶縁膜3にコンタクトホール7aを形成した後でイオンドーピングしてn+領域7を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、トランジスタ特性のばらつきを抑制することができ、また電気特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100の表面部分において選択的に形成された溝140と、溝140を埋め込むように形成され、酸素のシリコンに対する比率が2以下になるように形成されたシリコン酸化膜170を少なくとも1つ含む複数の膜160、170とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】Pチャネル電界効果トランジスタとNチャネル電界効果トランジスタとを有し、これらの電界効果トランジスタの高性能化を図り易い半導体装置の製造方法を得ること。

【解決手段】形成しようとする電界効果トランジスタ毎に、ゲート絶縁膜11,21とポリシリコン電極63a,63bとキャップ膜65a,65bとがこの順で積層された積層体を半導体基板10上に形成した後、各ポリシリコン電極の線幅方向両側面に直接、またはオフセットスペーサ膜15,25を介してサイドウォールスペーサ17,27を形成し、各キャップ膜の上面を含む平面に上面が位置する層間絶縁膜73aを形成してからこれらのキャップ膜を除去して各ポリシリコン電極の上面を露出させ、その上に第1金属層75aまたは第2金属層79を形成した後に該金属層によりその下のポリシリコン電極全体をシリサイド化して、互いに異なる金属のシリサイドからなるゲート電極を形成する。

(もっと読む)

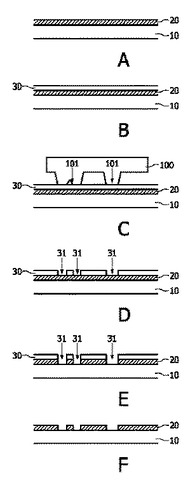

多層構造の形成方法

基板に電気化学エッチングまたは電気めっきを施すことにより多層構造を形成する方法。基板上にシード層を形成し、その上に主電極を形成する。主電極は、基板から複数の電気化学セルを形成するためのパターン層を有する。電圧が印加され、シード層がエッチングされて、またはシード層に材料がめっきされて形成された構造(8)の間に誘電体(9)が堆積される。誘電体層は下層構造を露出するために平坦化され、別の構造層が第1の構造層上に形成される。または、誘電体層は2層の厚さで形成され、下層構造の上端部を選択的に露出するために選択的にエッチングされる。また、複数の構造層を1工程で形成しても良い。 (もっと読む)

半導体集積回路装置の製造方法

【課題】ポリメタル(高融点金属膜/バリア層/多結晶シリコン膜)を使用するゲート加工プロセスにおいて、ゲートパターニング後のライト酸化処理時に金属膜が酸化されるのを防止すると共に、ゲート側壁端部における酸化膜形成の再現性および酸化膜厚の均一性を制御可能とする。

【解決手段】ゲート酸化膜を形成した半導体ウエハ1A上にポリメタル構造のゲート電極を形成した後、水素と、触媒作用によって水素および酸素から生成した水蒸気とを含み、かつ実質的に水素ラジカルを含まず、水蒸気の分圧が水素の分圧よりも低いガス雰囲気中で多結晶シリコン膜を選択的に熱酸化する工程とを有し、上記熱酸化工程は、酸化炉100とこの酸化炉100に接続された触媒方式のガス生成装置140に酸素および水素を導入し、ガス生成装置140から酸化炉100に水素と水蒸気を導入して行い、ガス生成装置140への水素の導入を開始した後に酸素の導入を開始する。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】仕事関数の調整された複数ゲート電極を形成するための製造方法を提供する。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイスは、第1のパラメータを有する少なくとも2つの第1のゲート電極120を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極120を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極膜とマスク材との界面での剥がれを防止する半導体装置およびその製造方法を提供すること。

【解決手段】本発明の一形態の半導体装置は、半導体基板(1)と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極膜(10)と、前記ゲート電極膜上に形成された絶縁膜(5)と、を備え、前記絶縁膜を構成するシリコンである第一の元素と第二の元素との組成比が膜厚方向に連続的または不連続に変化している。

(もっと読む)

半導体装置の製造方法。

【課題】半導体装置の生産性および製品の歩留まりが向上する半導体装置の製造方法を提供する。

【解決手段】本発明によれば、フォトマスクとして、マスクパターンを分割して得られる第1矩形パターン104aを有する第1フォトマスク106、および前記マスクパターンを分割して得られる第2矩形パターン104bを有する第2フォトマスク108を用いて半導体装置を製造する。半導体装置を製造する際には、第1フォトマスク106を用いて、半導体基板上の犠牲膜を第1矩形パターン104aに加工する第1の工程、第2フォトマスク108を用いて、前記犠牲膜を第2矩形パターン104bに加工する第2の工程、および第1の矩形パターン104aおよび第2の矩形パターン104bに加工された前記犠牲膜をマスクとして、半導体基板上に形成された膜をエッチングする第3の工程、を含む。

(もっと読む)

薄膜トランジスタ基板とその製造方法、並びにこれを有する液晶表示パネル及び電界発光表示パネル

【課題】自然酸化を防止して電気的な特性を向上させた薄膜トランジスタ基板とその製造方法、並びにこれを有する液晶表示パネル及び電界発光表示パネルを提供する。

【解決手段】薄膜トランジスタは、ゲート電極、アクティブ層、ソース電極、ドレイン電極、及びバッファ層を含む。ゲート電極はベース基板上に形成される。アクティブ層はゲート電極をカバーするようにゲート電極の上部に形成される。ソース電極及びドレイン電極はアクティブ層の上部に所定の間隔で離隔されて形成される。バッファ層は、アクティブ層とソース電極及びドレイン電極との間にそれぞれ形成され、厚さによって連続的に変動する含有量比を有する複数の物質からなる。ソース電極及びドレイン電極とアクティブ層との間にバッファ層が形成されることによって、酸化による接触抵抗が増加することを防止することができ、薄膜トランジスタの電気的な特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】高精度なパターン形成を行なうことが可能となる半導体装置の製造方法を提供する。

【解決手段】基板1の主表面上に絶縁膜7を形成する。絶縁膜7上に導電膜8を形成し、該導電膜8上に下層レジスト膜9、中間層10、反射防止膜11および上層レジスト膜を形成する。この上層レジスト膜の高さを検出することで露光時の焦点位置を検出する。露光時の焦点位置を検出するに際し、焦点検出光を上層レジスト膜に照射する。焦点位置を検出した後、上層レジスト膜を露光、現像し、レジストパターン12aを形成する。レジストパターン12aをマスクとして中間層10と反射防止膜11をパターニングし、下層レジスト膜9を現像する。これらのパターンをマスクとして導電膜8をエッチングし、ゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ポリメタル構造のゲート電極の形成に際して、バーズピーク酸化層を適度な膜厚に形成しつつ、バーズピーク酸化層の端部の尖りを抑制できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板11の表面にゲート絶縁膜15aを形成する工程と、ゲート絶縁膜上に、ポリシリコン層16及びタングステン層17を順次に堆積する工程と、ポリシリコン層16及びタングステン層17をパターニングする工程と、水及び水素を含む酸化性雰囲気中でポリシリコン層16を酸化する熱酸化工程とをこの順に有する。熱酸化工程は、基板表面温度を850℃以上とし、水分濃度が7%以上で20%以下の雰囲気下で行う。

(もっと読む)

半導体装置

【課題】微細化に伴う浮遊ゲート(FG)電極間の浮遊容量の増加を抑制できる不揮発性メモリセルを実現すること。

【解決手段】チャネル幅方向において、FG電極幅は、メモリセル高さ方向に変化し、かつ、FG電極底面よりも上の領域とFG電極上面よりも下の領域の間で最小となり、チャネル幅方向において、素子分離絶縁膜上面が半導体基板表面よりも高くかつ、FG電極上面よりも低く、チャネル幅方向において、素子分離絶縁膜上面とFG電極とが接する位置から下方に向かって、FG電極は幅が増加する部分を有し、チャネル幅方向において、電極間絶縁膜は素子分離絶縁膜よりも上の部分のFG電極側面上にも設けられ、チャネル幅方向において、制御ゲート電極は隣接する二つのFG電極間が埋め込まれるように、FG電極側面上の電極間絶縁膜上にも設けられ、チャネル長方向において、隣接する二つのメモリセルのFG電極は層間絶縁膜を介して対向している。

(もっと読む)

半導体装置およびその製造方法

【課題】ニッケルシリサイドのパターニングを精度よく行なうことのできる半導体装置の製造方法と半導体装置を提供する。

【解決手段】半導体基板1の主表面に絶縁膜、ポリシリコン膜およびニッケル層が形成される。ランプアニール処理を施すことにより、ニッケルシリサイド層が形成され、未反応のニッケル層が除去されて、ニッケルシリサイド層上にハードマスク9が形成される。ハードマスク9をマスクとして、NH3とCOとを含むガスを用いた異方性のプラズマエッチングと、Cl2ガスを用いた異方性のプラズマエッチングとを交互に行なうことによって、ゲート電極となるニッケルシリサイド層8aおよびポリシリコン膜5aが形成される。その後、ソース・ドレイン領域が形成され、そのソース・ドレイン領域にニッケルシリサイド層がそれぞれ形成される。

(もっと読む)

ゲートに近接したコンタクト・ホールを有する半導体トランジスタ

【課題】 デバイス密度を増加させるために、S/Dコンタクト・ホールが、トランジスタ構造体のゲートに近接して形成されるが、ゲートから電気的に絶縁された、トランジスタ構造体(及びその製造方法)を提供すること。

【解決手段】 構造体、及びその製造方法である。この構造体は、(a)第1のS/D領域と第2のS/D領域との間に配置されたチャネル領域と、(b)チャネル領域上のゲート誘電体領域と、(c)ゲート誘電体領域上にあり、かつ、ゲート誘電体領域によりチャネル領域から電気的に絶縁されたゲート領域と、(d)ゲート領域上の保護アンブレラ領域であって、保護アンブレラ領域は第1の誘電体材料を含み、ゲート領域が完全に保護アンブレラ領域の影の中にある、保護アンブレラ領域と、(e)(i)第2のS/D領域の真上にあり、これと電気的に接続され、かつ、(ii)保護アンブレラ領域のエッジと位置合わせされた充填されたコンタクト・ホールであって、コンタクト・ホールは、第1の誘電体材料とは異なる第2の誘電体材料を含む層間誘電体(ILD)層によってゲート領域から物理的に分離された充填されたコンタクト・ホールと、を含む。

(もっと読む)

パターン形成方法、薄膜トランジスタ、及び電子機器

【課題】 より緻密でかつ密着性の良い拡散防止層を形成し、拡散防止層を構成する金属元素が他の層に拡散することを防止したパターン形成方法、薄膜トランジスタ、及び電子機器を提供する。

【解決手段】 基板P上に隔壁30を形成する隔壁形成工程と、隔壁30に囲まれたパターン形成領域に導電層80を形成する導電層形成工程と、導電層80を含む隔壁30上に、無電解めっき法により拡散防止材料82aを配置する拡散防止材料配置工程と、拡散防止材料82a上に無機材料からなるマスクパターン36を形成するマスクパターン形成工程と、マスクパターン36を用いて拡散防止材料82aをパターニングし、導電層80上に拡散防止層82を形成する拡散防止層形成工程とを有する。

(もっと読む)

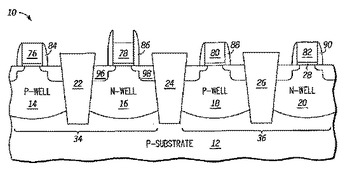

低減されたゲートドーピングを用いる半導体構造体及び同構造体を形成する方法

半導体構造体10は記憶領域34と論理領域36とを有する基板12を含む。第一のp型デバイスは記憶領域34に形成され、第二のp型デバイスは論理領域36に形成される。第一のp型デバイスの半導体ゲートの少なくとも一部は第二のp型デバイスの半導体ゲートの少なくとも一部よりもより低いp型ドーパント濃度を有する。第一及び第二のp型デバイスの半導体ゲートの各々は、ゼロではないp型ドーパント濃度を有する。  (もっと読む)

(もっと読む)

構造の作製方法

金層(20)が金酸化物マスク(30)でパターニングされる。前記マスクは、酸によってパターニングされ、好適にはマイクロコンタクトプリントによってパターニングされる。金酸化物マスク(30)は、金層(20)用のアルカリエッチング溶液中で安定である。金酸化物マスク(30)は、再曝露可能な金パッド(20)を形成するように維持されて良い。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】シリコン窒化膜が半導体基板に近接しないようにした半導体集積回路装置と、コンタクトホールの加工を容易にする半導体集積回路装置の製造方法を提供する。

【解決手段】素子分離領域4に囲まれたシリコン基板21上に、シリコン窒化膜をエッチングストッパーとして用いた自己整合コンタクトプロセスによって形成されたコンタクトホールに埋め込まれ、拡散層2,3に電気的に接続されたコンタクトプラグ33を有する半導体集積回路装置であって、前記拡散層2、3の露出面に選択エピタキシャル成長により形成された、各ゲート絶縁膜22の前記拡散層側端部と接するシリコン層28を形成し、各ゲート電極22と前記シリコン層28との間にシリコン酸窒化膜またはシリコン酸化膜からなる絶縁膜27’が前記ゲート絶縁膜22に接して埋め込まれており、シリコン窒化膜26,29’,32が絶縁膜27’によりシリコン基板21と隔離されている。

(もっと読む)

401 - 420 / 542

[ Back to top ]