Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

321 - 340 / 542

半導体装置の製造方法

【課題】エッチングプロセスのゆらぎによるばらつきを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、第1の材料膜を介して第2の材料膜を形成する膜形成工程と、前記第2の材料膜を所定のパターンにするパターン化工程と、所定のパターンにされた前記第2の材料膜の幅をエッチングにより細めるスリミング工程と、前記第1の材料膜をエッチングして、幅を細めた前記第2の材料膜のパターンを前記第1の材料膜に転写する第1の材料膜エッチング工程と、エッチングされた前記第1の材料膜の幅を測定する測定工程と、測定した前記第1の材料膜の幅に基づき、前記第1の材料膜の幅を所定の幅にする寸法調整工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】良好な電気的特性を備える薄膜半導体装置及びその製造方法を提供する。

【解決手段】薄膜半導体装置10は、基板11と、第1絶縁層(アンダーコート層)12と、第1導電層13と、第2絶縁層14と、半導体層15と、チャネル領域16と、ソース領域17と、ドレイン領域18と、ゲート絶縁膜19と、層間絶縁膜20と、ゲート電極21と、ソース電極22と、ドレイン電極23と、バイアス電極24と、を備える。バイアス電極24と第1導電層13によって半導体層15の基板側の界面にバイアス電圧を印加することによりオフ電流の低減や閾値電圧などの不安定性を抑止することができ、薄膜半導体装置10は良好な電気的特性を備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】導電層上に形成された光触媒反応層を除去する工程を経ることなく、導電性を有し、かつ濡れ性の高い領域を簡便に形成する方法を提案する。

【解決手段】光触媒導電層上に光触媒反応層を形成し、該光触媒導電層に紫外光を照射することにより、紫外光が照射された領域の光触媒導電層表面に導電性を有し、かつ該光触媒反応層に比べて濡れ性の高い領域を形成する。なお、ここで、該光触媒導電層として抵抗率が1×10−2Ωcm以下で光触媒性を有する層を用いることができる。

(もっと読む)

半導体装置の製造方法

【課題】素子構造部にダメージを与えずに側壁スペーサ膜等を除去し、高集積化された高性能な半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】被処理基体上にGeCOHまたはGeCHからなる第1の薄膜を形成すると、この第1の薄膜の一部を除去する工程と、第1の薄膜の除去された部位を介して被処理基体に所定の処理を施す処理工程と、第1の薄膜を除去する工程とを備えたことを特徴とする。GeCOHまたはGeCHからなる側壁スペーサ膜30を用い、ソース、ドレイン領域形成処理を行った後、これを除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】接合リークの増大を抑制できるとともに、狭いゲート電極間におけるコンタクトの不良の発生、および層間絶縁膜の埋め込み不良の発生を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】まず、ゲート電極4をマスクとしたイオン注入によりLDD領域5が形成される。ゲート電極4の側面に第1のサイドウォール7が形成された後、これらをマスクとしてソース・ドレイン領域8が形成される。ソース・ドレイン領域8上にシリサイド領域を形成する前に、第1のサイドウォール7の側面に第2のサイドウォール10が形成される。ソース・ドレイン領域8にシリサイド領域11が形成された後、第2のサイドウォール10が除去される。これにより、第1のサイドウォール7とシリサイド領域11との間のソース・ドレイン領域8に非シリサイド領域12が設けられる。

(もっと読む)

半導体素子の製造方法

【課題】特に60nm以下の半導体素子の品質と歩留まりを向上する半導体素子の製造方法の提供。

【解決手段】半導体基板200上にフローティングゲート、誘電体膜、コントロールゲート用導電膜、タングステンシリサイド膜、第1シリコン酸化窒化膜、ハードマスク膜、第2シリコン酸化窒化膜、有機下部反射防止膜を形成し、その有機下部反射防止膜から逆手順で上記各膜を除去し、誘電体膜を除去することでフローティングゲートの側面にスペーサ224を形成し、フローティングゲートを除去する。エッチング工程においてエッチング選択比を第一、第二の2段階を経て第1導電膜を除去すれば、60nm以下の素子において70nmの素子を用いたゲートエッチング技術をそのまま利用した場合でも、高いアスペクト比でゲートラインの側面がアタックを受けない。第1導電膜の除去工程時にスペーサ224はフィールド領域の境界面にあるアクティブ領域を保護する。

(もっと読む)

半導体装置

【課題】少なくともシリコン層と、高融点金属を含む金属層と、シリコン層と金属層との間に形成された、高融点金属のシリサイド層とを有する多層構造の配線を備える半導体装置において、シリコン層表面の状態の影響を受けにくく、均一な膜質を有するシリサイド層を形成する。

【解決手段】半導体装置10は、ゲート絶縁膜12上に順次に積層された、多結晶シリコン(poly-Si)層13、タングステン・シリサイド(WSi)層14、タングステン・ナイトライド(WN)層15、及び、タングステン(W)層16を有する多層構造のゲート電極17を備える。WSi層14が、poly-Si層13に接する第1部分14aと、第1部分14aを覆って形成され第1部分14aよりもタングステンの含有量が多い第2部分14bとを有する。

(もっと読む)

集積半導体構造の製造方法

【課題】 記憶装置のセルアレイ及び周辺部品を大量に、同時に、かつ安全に形成できる確実な製造プロセスを提供することにある。

【解決手段】 本発明は、集積半導体構造の製造方法、及びそれに対応する半導体構造を提供する。本方法は、周辺回路を周辺装置領域に形成するステップであって、周辺回路は、半導体基板に少なくとも部分的に形成され、かつ第1の高温処理ステップで形成される第1のゲート誘電体を有する周辺トランジスタを備えるステップと、複数のメモリセルを一つのメモリセル領域に形成するステップであって、各メモリセルは、半導体基板に少なくとも部分的に形成され、第2の高温処理ステップで形成される第2のゲート誘電体を有し、かつ金属ゲート導体を有するアクセストランジスタを備えるステップとを備え、第1及び第2の高温処理ステップが金属ゲート導体を形成するステップよりも前に実行される。

(もっと読む)

YBがドープされたポリシリコンゲートのドライエッチング方法

【課題】本発明は、従来の反応性イオンエッチングの間、揮発性の化合物を生成しない元素、例えばイットリビウム(Yb)が注入されたポリシリコンゲートをエッチングすることを目的とする。

【解決手段】本発明は、従来の反応性イオンエッチングを用いて、揮発性の化合物を形成しない元素を含むスタックをパターニングする方法に関する。より詳細には、上記元素はイットリビウム(Yb)等のランタニド元素であり、上記パターニングは、例えばイットリビウム等のランタニド元素がドープされたシリコン及び/又はゲルマニウム含有構造(例えばゲート)である(例えばYbドープゲート)。当該シリコン及び/又はゲルマニウム含有構造がゲート電極である場合、ゲート電極の仕事関数をモデリングするため、上記シリコン及び/又はゲルマニウムにランタニド元素(例えばYb)をドープする。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド形成ストレスで発生する欠陥による微小リークを低減する。

【解決手段】 単結晶Si基板101にゲート酸化膜102を介してゲート電極103が設けられ、ゲート電極103の両側部に側壁絶縁膜105が設けられ、素子分離領域としてLOCOS酸化膜104が設けられている。ソース・ドレイン領域108は側壁絶縁膜105とLOCOS酸化膜104との間の領域に形成されている。さらに、側壁絶縁膜105の傾斜側曲面上にSi基板101に接しない状態に庇状の扇形絶縁膜106が形成され、LOCOS酸化膜104の傾斜側曲面上にSi基板101に接しない状態に扇形絶縁膜107が形成されている。ソース・ドレイン領域108上において、扇形絶縁膜106下方と扇形絶縁膜107下方を除く領域にシリサイド層109が形成されている。つまり、シリサイド層109がソース・ドレイン領域108より狭い範囲で形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 ゲート電極側壁酸化時においてタングステンシリサイド膜の側壁に形成されるシリコン酸化膜が多結晶シリコン膜の側壁に形成されるシリコン酸化膜よりも膨らんだ形状となることを、工程数を増やすことなく防止する。

【解決手段】 圧力4乃至10mmTorr、RFソースパワー200乃至400W、バイアスパワー100乃至200W、CF4/Cl2/N2の混合ガス条件下で、CF4ガスの流量を1乃至50sccm、Cl2ガスの流量を100乃至150sccm、N2ガスの流量を7sccm以下としてタングステンシリサイド膜6のエッチングを行い、予めタングステンシリサイド膜6を括れ形状に加工することで、ゲート電極側壁酸化時にタングステンシリサイド膜6の方が第1の多結晶シリコン膜3及び第2の多結晶シリコン膜5より多く酸化しても、所望のゲート電極形状を得ることができる。

(もっと読む)

画像表示装置とその製造方法

【課題】イオン注入とホトリソグラフィーの工程数を削減できる構造をもつ薄膜トランジスタとすることで、製造にかかる時間を短縮した画像表示装置を提供する。

【解決手段】ゲート電極GTを薄い下層金属GMBと上層金属GMTの積層構造とし、保持容量Cst部分の上層電極を下層金属GMBのみとする。そして、保持容量Cstの下部電極用インプラを、薄い下層金属GMBを通過させて、ソース・ドレインのインプラと同時に行う。PMOSTFTのゲート電極も下層金属GMBのみとし、ソース・ドレインのインプラと閾値調整インプラを同じレジストを利用して行う。薄膜トランジスタと保持容量をこのような構造としたことで、ホト工程とイオン注入工程が各々1工程削減でき、より短時間で、より廉価に画像表示装置のためのアクティブ・マトリクス基板が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】コーナーラウンディング現象を抑制できるゲート電極構造を備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101に形成された素子分離領域102と、素子分離領域102に囲まれた活性領域103a、103bと、素子分離領域102及び活性領域103a、103b上に形成され、素子分離領域102上に活性領域103a、103b上に比べてゲート長方向のパターン幅が大きい第1の領域を有する第1のゲート電極105とを備える。第1のゲート電極105における第1の領域は、膜厚が活性領域103a、103b上の膜厚と異なる部分を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高速動作可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】p型半導体基板11上にゲート絶縁膜21を介して形成されたゲート電極24と、ゲート電極24側面の延長面Aの両側に跨り、半導体基板11内に埋め込まれたp型不純物元素領域33と、p型不純物元素領域33の一部と重畳し、且つゲート電極24端部から外方に延在するn型のソース・ドレイン領域31とを具備している。そして、p型不純物元素領域33とソース・ドレイン領域35との重畳部分における特定深さのp型不純物元素の濃度を、特定深さに対応する重畳部分以外のp型不純物元素領域33部分におけるp型不純物元素の濃度より低くしている。

(もっと読む)

半導体装置の製造方法

【課題】パターンの疎密差に起因したエッチング加工の差を低減する。

【解決手段】メモリセル領域および周辺回路領域の各トランジスタのゲート電極G、GPは、シリコン基板1に、ゲート絶縁膜4、多結晶シリコン膜5、電極間絶縁膜6、多結晶シリコン膜7を順次積層して構成される。ゲート加工時には、その上部にハードマスクとしてシリコン窒化膜8を積層し、ドライエッチングで、上記の各層をエッチングして掘り下げる。このとき、多結晶シリコン膜7、5をエッチングする場合に、半導体基板の温度を50℃以上にし、メインガスとして臭化水素(HBr)ガスを、添加ガスとしてフルオロメタン系ガスであるフッ化メチル(CH3F)、フッ化メチレン(CH2F2)、3フッ化メタン(CHF3)、4フッ化炭素(CF4)の4種類のガスのいずれかを用いることで疎密差に起因したエッチング加工の差を低減する。

(もっと読む)

リセスゲート及びその製造方法

【課題】バルブ型リセスパターンのボールパターン内に残留するボイドの大きさを小さくすることができる半導体素子のリセスゲート及びその製造方法を提供すること。

【解決手段】リセスゲートは、第1直径を有する第1ボールパターン部25A及び第2直径を有する第2ボールパターン部27からなり、第1ボールパターン部25Aが基板21の表面側に位置するバルブ型リセスパターン100を有する基板21と、バルブ型リセスパターン100の内面及び基板21の表面に形成されたゲート絶縁膜28と、ゲート絶縁膜28上に形成され、バルブ型リセスパターン100内に埋め込まれた導電膜29とを備える。バルブ型リセスパターン100が、断面形状及び直径が異なる第1と第2のボールパターン部25A、27からなるひょうたん形であるので、導電層(例えば、ポリシリコン)内に残留するボイドの大きさを小さくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】 微細化された半導体デバイスにおいては、側面酸化時にゲート電極のポリシリコン膜やゲート絶縁膜が酸化されゲート絶縁膜厚が部分的に厚くなり、MISFETの電気特性が劣化するという問題がある。

【解決手段】 側面酸化をプラズマ酸化により行う。プラズマ酸化により酸化種の侵入距離を短くし、ポリシリコン膜やゲート絶縁膜の酸化を抑制する。側面酸化時の酸化を抑制することで、ゲート絶縁膜厚の増大を抑える事ができる。ゲート絶縁膜厚の増大を抑制することで安定した電気特性を有するMISFETを備えた半導体装置が得られる。

(もっと読む)

セルフアラインダブルパターニング法を使用したパッドパターンの形成方法、それによって形成されたパッドパターンレイアウト、及びセルフアラインダブルパターニング法を使用したコンタクトホールの形成方法

【課題】フォトリソグラフィ工程での解像限界を克服し微細ピッチのパターンを実現可能なパターン形成のためのセルフアラインパターニング方法を提供する。

【解決手段】この方法は、第1膜を形成し、第1膜上に複数の第1ハードマスクパターンを形成し、第1ハードマスクパターンの上面及び側壁を覆う犠牲膜23を、第1ハードマスクパターンの側壁上に形成された犠牲膜23の相互対向する部分の間にギャップを残存させて形成するステップと、ギャップ内に第2ハードマスクパターン24aを形成し、第2ハードマスクパターン24aをマスクとして犠牲膜23をエッチングし第1ハードマスクパターンを露出させるステップと、第2ハードマスクパターン24aと露出された第1ハードマスクパターンとを使用し導電膜を露出させるステップと、第1ハードマスクパターンと第2ハードマスクパターンとを使用し露出された第1膜をエッチングするステップと、を含む。

(もっと読む)

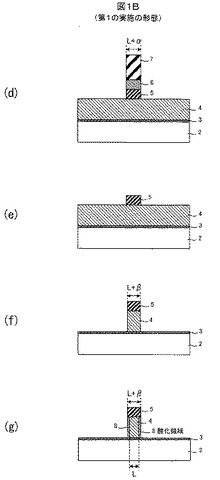

半導体装置の製造方法

【課題】半導体装置のゲートパターンの寸法精度を高める。

【解決手段】被加工膜に所定のパターンを形成する際に、被加工膜上に、第1の膜、第2の膜、および第3の膜がこの順で積層された積層ハードマスク膜を形成し(S100)、微細パターン用レジスト膜を用いて第2の膜をエッチングストッパとして第3の膜に細幅ラインパターンを形成し(S102)、微細パターン用レジスト膜を除去する(S104)。つづいて、再度レジスト膜を用いた露光を行い(S106〜S110)、第2の膜、第1の膜および被加工膜を順次選択的にドライエッチングして被加工膜を所定のパターンに形成する(S112)。その後、被加工膜上に残った第1の膜を除去する(S114)。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明は、PチャネルMOSFETのゲート電極に所定値以上の仕事関数を有するメタルを用いた場合であっても、適正なしきい値電圧を有する半導体装置及び当該半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、NチャネルMOSFET及びPチャネルMOSFETを含む半導体装置であって、前記PチャネルMOSFETのゲート電極は、第1の濃度の酸素を含有する第1の導電性膜110aと、前記第1の濃度より高い第2の濃度の酸素を含有する第2の導電性膜110bと、前記第2の濃度より低い第3の濃度の酸素を含有する第3の導電性膜110cと、を含む積層構造を有することを特徴とするものである。

(もっと読む)

321 - 340 / 542

[ Back to top ]