Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

261 - 280 / 542

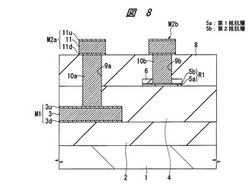

半導体装置およびその製造方法

【課題】寄生容量が低く、かつ、熱処理による抵抗値の変動が小さい抵抗素子を有する半導体装置を得ることのできる技術を提供する。

【解決手段】スパッタリングターゲット材料としてタンタルを用い、スパッタリングガスとしてアルゴンと窒素との混合ガスを用いた反応性直流スパッタリング法により、窒化タンタル膜からなる厚さ20nm、窒素濃度30原子%未満の第1抵抗層5a、及び窒化タンタル膜からなる厚さ5nm、窒素濃度30原子%以上の第2抵抗層5bを順次形成した後、第1及び第2抵抗層5a,5bを加工して抵抗素子R1を形成する。窒素濃度が30原子%以上の上部領域を設けることにより、配線工程において熱負荷が与えられても抵抗素子R1の抵抗変動率を1%未満に抑えることができる。

(もっと読む)

微細パターンの形成方法

【課題】 犠牲膜を、強度を有しながらも容易に除去できるものとし、解像限界以下の幅を持つ下地膜のパターンを再現性良く安定して形成できる微細パターンの形成方法を提供すること。

【解決手段】 薄膜2上に、この薄膜2とは異なる膜からなり、かつ、SiBNからなる犠牲膜3を形成し、犠牲膜3を、フォトリソグラフィ技術を用いて、所定の間隔を持つパターンに加工し、加工された犠牲膜3の側壁上に、犠牲膜3及び薄膜2とは異なる膜からなる側壁スペーサ5´を形成し、加工された犠牲膜3を除去し、側壁スペーサ5´をマスクに用いて、薄膜2を加工する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の配置間隔を小さくしても所望のゲート電極のパターンを安定して形成することができ、特性・信頼性の劣化を防ぐことができる半導体装置の製造方法を得る。

【解決手段】半導体基板11上に複数の凹部14を形成する。複数の凹部14の内壁を覆うように半導体基板11上に絶縁膜15を形成する。絶縁膜15上にレジスト16を形成し、露光及び現像によりレジスト16に、複数の凹部14上において、対応する凹部14よりも幅が狭い複数の開口13をそれぞれ形成する。レジスト16をマスクとして絶縁膜15を異方性エッチングして凹部14の底面の一部を露出させる。露出した凹部14の底面及び絶縁膜15上にWSiN膜21及びAu膜22(導体膜)を形成する。複数の凹部14以外の領域においてWSiN膜21及びAu膜22を除去して、それぞれの凹部14内に残されたWSiN膜21及びAu膜22によりゲート電極23を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

パターン形成方法

【課題】幅の異なるパターンを同時に容易に形成することができるパターン形成方法を提供する。

【解決手段】被加工膜1上に複数のライン状のパターンを形成する工程と、複数のライン状のパターンの各側壁に側壁膜を形成する工程と、被加工膜1上、及び複数のライン状のパターンの各側壁に形成された側壁膜間に、複数のライン状のパターンと主元素が同一の材料である材料膜を堆積する工程と、材料膜をエッチングし、側壁膜間でライン状のパターンとして孤立させると共に、被加工膜1上でライン状のパターンより幅の広いパターンを形成する工程と、材料膜をエッチングした後、側壁膜を除去する工程とを備える。

(もっと読む)

自己整合型有機薄膜トランジスタ及びその製造方法

本発明は、自己整合型有機薄膜トランジスタ及びその製造方法に関するものである。本発明によれば、基板上にパターニングされた第1導電膜としてゲート電極を形成し、ゲート電極を覆うように基板上にゲート絶縁膜を形成した後、ゲート絶縁膜上に第2導電膜を形成する。次いで、基板の下部側でゲート電極をマスクとして用いて、第2導電膜に紫外線を照射する紫外線背面露光を遂行した後、第2導電膜を現像することで、ゲート電極と自己整合され、ゲート電極と重畳しないソース/ドレイン電極を形成する。次いで、ソース/ドレイン電極の間及び上部に有機半導体膜を形成する。本発明は、リール・トゥ・リール工程を用いて、有機薄膜トランジスタを製造することができ、製造工程が単純になる。  (もっと読む)

(もっと読む)

半導体デバイス、および半導体デバイスを含む電子システムの製造中に、対称なフォトマスクを用いて対称もしくは非対称な機構を選択的に形成するための方法

半導体デバイスの製造中に材料をパターン化するための方法は、どの工程が選ばれるかによって、対称なフォトマスクを用いて非対称な機構もしくは対称な機構のいずれかを選択的に形成する。製造される、結果として得られる機構は、パターン化材料の周囲に形成されるスペーサーを用いる。基材を除去するために一つの特定のエッチングが使用される場合、対称な機構が得られる。基材を除去するために二つの特定のエッチングが使用される場合、非対称な機構が得られる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】トリミングを用いず、プロセスの大幅な変更や工程数を大きく増加させずに、高精度に微細化してゲート電極または配線を形成できる半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10のチャネル形成領域上にゲート絶縁膜12を形成し、その上層に第1導電層20を形成し、第1導電層にゲート電極のパターンに対応し第1の幅20wを有する第1凹部20tを形成し、その内壁を被覆して、第1の幅より狭い第2の幅31wの第2凹部31tを有する第2導電層31を形成し、第2凹部を埋め込んでマスク層32を形成し、第1凹部の外部における第2導電層及びマスク層を除去し、第1凹部に残されたマスク層をマスクとして第2導電層及び第1導電層をパターン加工してゲート電極Gを形成し、ゲート電極Gの両側部における半導体基板中にソース・ドレイン領域13を形成する。

(もっと読む)

表示装置の製造方法

【課題】フォト工程の低減を図った表示装置の製造方法。

【解決手段】第1導電型TFTと第2導電型TFTの各形成領域に、半導体層、第1絶縁膜、ゲート電極が形成され、前記半導体層のチャネル領域の各外側に第1導電型不純物領域が形成されている基板上に第2絶縁膜を形成し、前記第1導電型TFTの形成領域において当該ゲート電極を露出させることなく、前記第2導電型TFTの形成領域において当該ゲート電極のうち半導体層と交差する各辺の一部を露出させるようにして、ドレインおよびソースの各電極の接続用のコンタクトホールを形成し、多層導電層によって、前記第1導電型TFTの形成領域における前記各コンタクトホール、前記第2導電型TFTの形成領域において前記各コンタクトホールのゲート電極の一部を被うようにして、ドレインおよびソースの各電極を形成し、第2導電型不純物をドープして、半導体層に第2導電型不純物領域を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】フィン型活性領域の断面形状が台形状である半導体装置において、パンチスルーの発生を防止する。

【解決手段】テーパー状の側面を有するフィン型活性領域13と、フィン型活性領域13の側面の一部を覆う側面被覆部14s及び上面の一部を覆う上面被覆部14tを有するゲート電極14と、フィン型活性領域13内に形成されたソース領域及びドレイン領域とを備え、ゲート電極14の側面被覆部14sの少なくとも一部は、上部よりも下部の方が幅が広くなっている。これにより、ゲート電極14による電界制御性が高められることから、パンチスルーの発生を防止することが可能となる。

(もっと読む)

パターニング方法、およびTFTの製造方法

【課題】複数の層にそれぞれ異なるパターンを与えること。

【解決手段】パターニング方法が、第1の層と第2の層とを有した多層構造のうちの前記第1の層に、浅い部分と深い部分とを有した凹パターンが与えられるように、少なくとも2つの異なる高さの部分を有したエンボスツールを用いて前記第1の層にエンボス処理を施す工程(a)と、前記深い部分の底部で、前記第2の層の下地表面が露出するように、前記第1の層を介して前記第2の層をエッチングする工程(b)と、前記浅い部分の底部で前記第2の層の表面が露出するように、前記第1の層をエッチングする工程(c)と、を包含している。

(もっと読む)

半導体装置

【課題】銅めっきをアンテナに用いた、集積回路とアンテナが一体形成された半導体装置において、銅の拡散による回路素子の電気特性への悪影響を防止し、また、集積回路とアンテナが一体形成された半導体装置において、アンテナと集積回路の接続不良に伴う半導体装置の不良を防止する装置を提供する。

【解決手段】半導体装置によると、同一の基板102上に集積回路100とアンテナ101とが一体形成された半導体装置において、銅めっき層108をアンテナ101の導体に用いた場合に、アンテナ101の下地層107に所定の金属の窒化膜を用いているので銅の回路素子への拡散を防ぎ、銅の拡散による回路素子の電気特性への悪影響を低減できる。また、アンテナの下地層の金属の窒化物の一つにニッケルの窒化物を用いることで、アンテナと集積回路の接続不良を低減することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の積層ゲート電極間に形成される電極間絶縁膜のアスペクト比が高く電極間絶縁膜内にシームが生じたとしても当該シーム内に不要成分を侵入させることなくデバイス不良を防止できるようにする。

【解決手段】シリコン酸化膜8上で且つ多結晶シリコン層6の側面位置にシリコン窒化膜14を形成した後、多結晶シリコン層6上のシリコン窒化膜12を除去している。このため、多結晶シリコン層6の上面をウェットエッチング処理して清浄化するときにシリコン酸化膜8の中央上部にシーム8aが形成されていたとしても、当該シーム8a上を覆うようにシリコン窒化膜14がキャップ絶縁膜として形成されているため、シーム8aを拡大させることなく多結晶シリコン層6の上面を清浄化することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、パターン形成時のパターン不良発生を防止してライン・アンド・スペースが的確に形成される半導体装置を提供することを目的とする。

【解決手段】複数のトランジスタを有する少なくとも2個のトランジスタブロックと、前記複数のトランジスタにそれぞれ接続された複数のゲートと、を有し、前記複数のゲートは、概略U字型の開ループ形状を有し、前記トランジスタブロック内に配置される前記複数のゲートは、隣接する2個のトランジスタブロック間で、それぞれ前記開ループ形状の開口部が対向して対称的に配置されることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】いわゆる側壁残しプロセスを適用して微細なパターンを備える半導体装置を効率良く、かつ、容易に製造することができる半導体装置の製造方法を提供する。

【解決手段】被処理基板1上に被加工層2およびマスク層を挟んで設けられた感光性部材からなる層に第1のパターンをパターニングする。第1のパターンをマスクとしてマスク層をエッチングしてマスク層に第1のパターンを転写する。第1のパターンが転写されたマスク層をエッチングして第1のパターンを縮小させた第2のパターン7aを形成する。第2のパターン7aの側壁部を囲んで側壁パターン8a,8bを設けた後に第2のパターン7aの少なくとも一部を除去する。側壁パターン8a,8bをマスクとして被加工層2をエッチングして被加工層2に側壁パターン8a,8bを転写する。

(もっと読む)

半導体装置の作製方法

【課題】作製コスト及び作製時間が低減された、信頼性の高い半導体装置を作製すること。

【解決手段】島状半導体膜を覆って絶縁膜を形成し、絶縁膜上に第1のゲート電極を形成し、第1のゲート電極をマスクとして絶縁膜をエッチングし第1のゲート電極と同じ幅のゲート絶縁膜を形成し、第1のゲート電極をマスクとして島状半導体膜に不純物元素を第1の濃度で添加し、金属膜を形成後加熱処理によりゲート絶縁膜に覆われていない領域にシリサイド領域を形成し、第1のゲート電極をエッチングし第1のゲート電極より幅の小さい第2のゲート電極を形成し、ゲート絶縁膜及び第2のゲート電極をマスクとして、島状半導体中に不純物元素を第1の濃度より小さい第2の濃度で添加し、島状半導体膜中に低濃度不純物領域、チャネル形成領域、及び高濃度不純物領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが互いに異なる複数種類のMISトランジスタを内蔵する半導体集積回路装置において、信頼度の高いゲート絶縁膜を形成すると同時に、MISトランジスタの製造を容易とする。

【解決手段】シリコン酸化膜9を半導体基板1の表面に形成した後、実効膜厚が薄いゲート絶縁膜が形成される領域のシリコン酸化膜9をフッ酸水溶液を用いて除去し、その後半導体基板1上に高誘電率絶縁膜10を形成することにより、高誘電率絶縁膜10とシリコン酸化膜9との積層膜からなるゲート絶縁膜12、および高誘電率絶縁膜10からなるゲート絶縁膜11の2種類のゲート絶縁膜を半導体基板1上に形成する。

(もっと読む)

フォトレジスト組成物およびこれを用いた薄膜トランジスタ基板の製造方法

【課題】優れた耐熱性および接着性を有するフォトレジスト組成物を提供することを目的とする。

【解決手段】本発明のフォトレジスト組成物は、第1のバインダー樹脂、第2のバインダー樹脂、光酸発生剤、架橋剤、および溶媒を含む。該フォトレジスト組成物は、フォトレジストパターンの耐熱性および接着性に優れるので、薄膜トランジスタ基板の開口率が増大し、表示品質を改善することができる。よって、該フォトレジスト組成物は、薄膜トランジスタ基板を製造するための4マスク工程に好適に用いられうる。

(もっと読む)

ナノワイヤトランジスタおよびその製造方法

【課題】ナノワイヤトランジスタ(NWT)の製造において、凹状ストリンガを除去する方法を提供する。

【解決手段】

本方法は、軸の外部表面が基板表面に接している円筒状のナノ構造体を準備する。ナノ構造体は、絶縁性半導体コアを含んでいる。導電性薄膜が、ナノ構造体上に堆積され、ゲートストラップ、またはゲートとゲートストラップとの組み合わせとして機能する。ハードマスク絶縁体が、導電性薄膜上に堆積され、ハードマスクの選択領域が異方性プラズマエッチングされる。結果として、ナノ構造体の円筒状部分を実質的に囲む導電性薄膜ゲート電極が形成される。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】微細パターンの形成工程を削減でき、量産時の製造コスト低減に有効な半導体素子の微細パターン形成方法を提供する。

【解決手段】半導体基板100上に、図1Eまでの工程の第1補助パターン(108)、下部反射防止パターン(BARC; 106a)、第2補助パターン(112a)をエッチングマスクとしてハードマスク膜(104)をエッチングして所要のラインとスペーサを有するハードマスクパターン(104c)を形成する(図1F参照)。その後、第1補助パターン(108)などを除去し、ハードマスクパターン(104c)からなる微細パターンを形成する。続く図1Gの工程でハードマスクパターン(104c)をエッチングマスクとしてエッチング対象膜(102)をエッチングしてエッチング対象パターン(102a)を形成してからハードマスクパターン(104c)を除去する。第1,第2補助パターン(108,112a)の形成工程のみで微細パターンを形成することで、所要の臨界寸法(CD)を有する微細パターンを形成でき、工程を削減する。

(もっと読む)

261 - 280 / 542

[ Back to top ]