Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

181 - 200 / 542

グラフェンナノデバイスの製造

【課題】 グラフェンナノデバイスの製造を提供する。

【解決手段】 ナノスケールのグラフェン構造製造技術が提供される。マスクとして有用な酸化物ナノワイヤが、グラフェン層上に形成され、次にイオンビームエッチングが実施される。ナノスケールグラフェン構造は、イオンビームエッチング後、残った酸化物ナノワイヤを除去することにより製造される。

(もっと読む)

半導体装置の製造方法

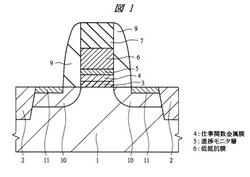

【課題】仕事関数金属膜と低抵抗膜とで構成されたゲート電極をプラズマエッチングする際に、膜質に応じたエッチングステップの切り替えの遅延を防ぐ。

【解決手段】低抵抗膜6中であって、仕事関数金属膜4との界面の近傍に、プラズマ発光モニタに感度のある、窒素を含む進捗モニタ層5を設けることで、エッチング中のプラズマ発光の変化を検知し、エッチングの進捗をモニタすることでエッチングステップ切り替えの遅延を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】 デュアルメタルゲート構造およびデュアルHigh−k構造などのデュアル仕事関数構造の形成プロセスにおける素子分離膜の削れを防止することができる半導体装置の製造方法を提供する。

【解決手段】 第2ゲート電極用金属層10Aおよび第2キャップ層9を、第1ハードマスク8の一端部を被うように形成する。これによって、第1ハードマスク8を除去する段階では、STI膜2上のゲート絶縁膜用絶縁膜5が露出しないので、第1ハードマスク8を除去するためのエッチング液でSTI膜2上のゲート絶縁膜用絶縁膜5が除去されることを防止することができる。したがって、STI膜2が削られることを防止することができる。

(もっと読む)

液晶表示装置用アレイ基板製造用のエッチングテープ

【課題】本発明は液晶表示装置用アレイ基板製造用のエッチングテープを提供する。

【解決手段】本発明のエッチングテープは、ベースシート及びベースシート上にゲルタイプのエッチング物質が塗布されて形成されたエッチング物質層を含む。このエッチングテープは、透明絶縁基板上にゲート電極、ストレージキャパシターの第1電極、ゲート配線を形成する段階、ゲート絶縁膜、アクティブ層、オーミック接触層、ソース電極及びドレーン電極を形成し、誘電体層及びストレージキャパシターの第2電極を形成し、データ配線を形成する段階、画素電極を形成し、ゲートパッド電極を形成し、データパッド電極を形成する段階、保護層を形成する段階及びゲートパッド電極上に形成された保護層とデータパッド電極上に形成された保護層をエッチングすることでコンタクトホールを形成する段階を含む液晶表示装置用アレイ基板の製造方法に利用される。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】微細なラインアンドスペースパターンを含むパターンを形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工材上に、第1の芯材、および前記第1の芯材下に位置し、前記第1の芯材よりも幅の大きい第2の芯材を形成する工程と、前記第1および第2の芯材の側面を覆うように被覆膜を形成する工程と、前記被覆膜を前記第1および第2の芯材の側面に位置する部分を残して除去し、側壁マスクに加工する工程と、前記側壁マスクをマスクとして前記第1および第2の芯材にエッチングを施し、前記第1の芯材、および前記第2の芯材の前記側壁マスクに上面を覆われていない部分を除去して、前記側壁マスク、および前記側壁マスクの直下に残った前記第2の芯材を含むエッチングマスクを形成する工程と、前記エッチングマスクをマスクとして前記被加工材にエッチングを施し、前記被加工材をパターン加工する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極間にエアギャップを制御良く形成する。

【解決手段】本発明の半導体装置の製造方法では、半導体基板2上のゲート絶縁膜3上に浮遊ゲート電極用の多結晶シリコン層4を形成するときに、多結晶シリコン層4の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、この多結晶シリコン層4上に形成したゲート間絶縁膜5上に制御ゲート電極用の多結晶シリコン層9を形成するときに、多結晶シリコン層9の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、複数のゲート電極の側面が露出した状態で熱酸化処理を行なった後、エッチングすることにより、多結晶シリコン層4、9の各側面に凹部11、12を形成し、複数のゲート電極間に絶縁膜7を埋め込み、埋め込まれた絶縁膜7の中にエアギャップ8を形成する。

(もっと読む)

キャパシタ及び薄膜トランジスタを有する基板、これを具備した平板ディスプレイ装置及び該キャパシタ及び薄膜トランジスタを有する基板の製造方法

【課題】製造工程を単純化させて製造コストを低減できるキャパシタ及び薄膜トランジスタを有する基板、これを具備した平板ディスプレイ装置及び該キャパシタ及び薄膜トランジスタを有する基板の製造方法を提供する。

【解決手段】(i)同一層に配された、半導体層、及びドーピングされた半導体層から形成されて導電性を有する第1キャパシタ電極、(ii)半導体層及び第1キャパシタ電極を覆う絶縁膜、(iii)絶縁膜上に配された、前記半導体層の一部領域に対応するゲート電極、及び第1キャパシタ電極に対応する第2キャパシタ電極を具備し、ゲート電極の厚さは、第2キャパシタ電極の厚さより厚いことを特徴とするキャパシタ及び薄膜トランジスタを有する基板、これを具備した平板ディスプレイ装置及び該キャパシタ及び薄膜トランジスタを有する基板の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】膜パターンが倒れないように半導体装置を製造する方法を提供する。

【解決手段】半導体装置の製造方法は、基板上にSiO2膜の膜パターンを形成する工程と、SiO2膜の膜パターンを両側面から挟むように複数のSi膜の膜パターンを形成する工程と、SiO2膜の膜パターンの上面と、複数のSi膜の膜パターンの上面と露出した側面とを被覆するようにレジスト膜を形成する工程と、SiO2膜の膜パターンの上面が露出するまでレジスト膜の一部を除去する工程と、レジスト膜が除去された後に、露出したSiO2膜の膜パターンをウェット処理により除去する工程と、SiO2膜の膜パターンが除去された後に、レジスト膜の残部をドライ処理により除去する工程と、を備える。

(もっと読む)

2重ハードマスク層を使用したCMOSイメージセンサの製造方法

論理領域でシリサイドを形成し、画素領域へのイオンの注入を容易にでき、同時に、ハードマスク層を除去するための処理を実行することなしにハードマスク層を薄い厚さで保持できるCMOSイメージセンサの製造方法が開示されている。ゲートパターンの形成時に限界寸法が容易に制御され、ゲートフォトレジストパターンの限界寸法の均一性が向上する。その方法には、画素領域および論理領域が規定された基板上にゲート導電層を形成するステップと、画素領域のハードマスクパターンの厚さが論理領域のハードマスクパターンの厚さより厚いような様式でゲート導電層上にハードマスクパターンを形成するステップと、ハードマスクパターンをエッチングバリアとして使用してゲート導電層をエッチングすることにより、画素領域および論理領域にゲートパターンを形成するステップと、論理領域に残るハードマスクパターンを除去するステップと、論理領域にシリサイドを形成するステップとが含まれる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】簡易な製造工程で、ライン幅とスペース幅をシュリンクした複数のパターンを精度よく形成する。

【解決手段】ゲート電極を構成する多結晶シリコン膜7上に、下地材としてシリコン窒化膜8が積層され、その上面にシュリンクパターンを形成するための非晶質シリコン膜12aが分離形成される。非晶質シリコン膜12aは、フォトリソグラフィ処理でWaの3倍の幅寸法45nmでパターニングされるが、スリミング技術で30nmに形成した上で、熱酸化により表層をシリコン酸化膜15に変質させ、これによって寸法がWaである15nmに形成される。シリコン酸化膜15の上面に非晶質シリコン膜16を形成してスペーサ加工を行うことで側壁部に非晶質シリコン膜16aを残存させる。この後、シリコン酸化膜15を弗酸処理で剥離するとラインアンドスペースが15nmのシュリンクパターンを形成できる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極をパターニングするときに、選択ゲートトランジスタのゲート電極脇のシリコン基板が掘られることを防止する製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板2のメモリセル部上および選択ゲート部上に電極材膜6を形成する工程と、電極材膜6およびハードマスク材膜7、8のうちのセル部に対応する部分を覆う第1のマスク材膜を作成する工程と、選択ゲート部のハードマスク材膜7、8および第1のマスク材膜をマスクとして選択ゲート部の電極材膜6を加工する工程と、電極材膜6、ハードマスク材膜7、8等のうちの選択ゲート部に対応する部分を覆う第2のマスク材膜11を作成する工程と、メモリセル部のハードマスク材膜7、8および第2のマスク材膜11をマスクとして電極材膜6、ブロック膜5およびシリコン窒化膜4を加工する工程とを備えてなる。

(もっと読む)

半導体装置の製造方法

【課題】高い精度で安定的にパターンを形成することができる、半導体装置の製造方法を提供する。

【解決手段】被加工膜PS上に、第1無機材料からなる第1無機膜HUと、第2無機材料からなりかつ第1無機膜HUと被加工膜PSとの間に位置する第2無機膜HDとが形成される。第1無機膜HU上の第1フォトレジストマスクR1をマスクとして用いて第1無機膜HUがエッチングされる。第2無機膜HD上に第2フォトレジストマスクR2が形成される。第2フォトレジストマスクR2および第1無機膜HUをマスクとして用いて第2無機膜HDがエッチングされる。第2無機膜HDをマスクとして用いて被加工膜PSがエッチングされる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板を不必要に露出させることなく、半導体装置の信頼性を向上できる技術を提供する。

【解決手段】半導体基板1S上にゲート電極G1とゲート電極G2を形成した後、nチャネル型MISFET形成領域を酸化シリコン膜で覆う一方、pチャネル型MISFET形成領域を露出する。続いて、半導体基板1Sの全面に例えば酸化アルミニウム膜よりなる元素供給膜7を形成した後、熱処理を実施する。これにより、ゲート電極G2直下の第1絶縁膜にアルミニウムを拡散させて高濃度HfAlO膜8aと低濃度HfAlO膜8bを形成する。その後、元素供給膜として例えば酸化マグネシウム膜を使用してゲート電極G1直下の第1絶縁膜にマグネシウムを拡散させて高濃度HfMgO膜と低濃度HfMgO膜を形成する。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

半導体デバイスの製造方法、製造装置、コンピュータプログラム、及びコンピュータ可読記憶媒体

【課題】寸法を制御すべき部位の寸法調整を可能とする半導体デバイスの製造方法、この方法に好適な半導体デバイスの製造装置を提供する。

【解決手段】開示される半導体デバイスの製造方法は、寸法を制御すべき部位の寸法を測定する寸法測定工程S8;寸法測定工程S8において得られた測定値が基準値よりも大きいか否かを判定する判定工程S9、S11;および判定工程S9、S11において測定値が基準値よりも大きいと判定された場合に部位を縮小する第1の工程と、判定工程において測定値が基準値よりも小さいと判定された場合に部位を増大する第2の工程とのいずれかを行う寸法調整工程;を含む。

(もっと読む)

金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFT

【課題】生産性が向上し、かつ寸法精度が良い金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFTを提供すること。

【解決手段】本発明にかかる金属配線の製造方法では、まず、主成分金属に、主成分金属より酸化物の生成エネルギーが低い添加金属が添加された第2の金属膜30を成膜する。そして、第2の金属膜30を酸化させて金属酸化物を形成し、第2の金属膜30の表面に酸化層32を形成する。次に、酸化層32上にフォトレジスト31を形成して、第1のドライエッチング条件により、酸化層32をエッチングする。そして、第1のドライエッチング条件の場合と比較して、主成分金属の金属酸化物に対する選択比が高い第2のドライエッチング条件により、下層の第2の金属膜30をエッチングする。

(もっと読む)

半導体装置、および、その製造方法

【課題】広帯域での利得、および、低い歪み特性を実現する。

【解決手段】第1のフィンF1における閾値電圧Vthと、第2のフィンF2a,F2bにおける閾値電圧Vthと、第3のフィンF3a,F3bにおける閾値電圧Vthとのそれぞれが互いに異なるように、finFET100を形成する。

(もっと読む)

半導体装置製造方法およびパターン寸法設定プログラム

【課題】側壁プロセスを用いた場合において、被処理層に最終的に形成されるパターン寸法の面内ばらつきを抑制することができる半導体装置製造方法および最適寸法設定プログラムを提供する。

【解決手段】本発明は、側壁プロセスにおけるパターン変換工程においてそれぞれ形成される各パターンの面内寸法ばらつき量から面内寸法ばらつき量の合計量を求め、該求めた面内寸法ばらつき量の合計量から、面内寸法ばらつき量が少なくなるような各パターンの仕上がり寸法を設定するため、側壁プロセスを用いた場合において、被処理層に最終的に形成されるパターン寸法の面内ばらつきを抑制することができるという効果を奏する。

(もっと読む)

半導体素子製造方法および半導体素子

【課題】チャネルが上・下方向に形成されるピラーパターンの転倒現象を防止する半導体素子製造方法を提供する。

【解決手段】導電膜33Bをパターニングして複数の開放領域を形成するステップと、各々の開放領域の側壁にゲート絶縁膜41を形成するステップと、各々の開放領域内にピラーパターン42を形成するステップと、ピラーパターン42間の導電膜33Bをエッチングし、ピラーパターン各々を覆うゲート電極33Bを形成するステップを含む。ピラーパターン42を基板31のエッチングでない成長によって形成し、成長はあらかじめ形成された開放領域を埋め込む形態を取るためピラーパターン42の転倒現象を防止することができ、ひいては半導体素子の信頼性および安全性を向上させる。

(もっと読む)

181 - 200 / 542

[ Back to top ]