Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

301 - 320 / 542

半導体装置の製造方法

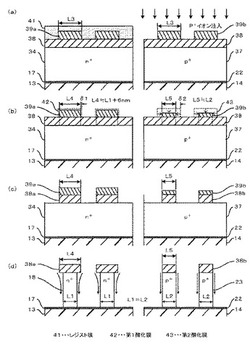

【課題】p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板11の第1領域13、第2領域、14にn型、p型ゲート電極膜34、37を形成する工程と、ゲート電極膜34、37上に第1保護膜38および第2保護膜39を形成する工程と、第2保護膜39に、ゲート電極サイズL1、L2より大きいサイズL3のゲート電極パターンを形成する工程と、第2保護膜39bに選択的に燐イオンを注入し、熱酸化速度が第2保護膜39aより大きくなるようにする工程と、第2保護膜39a、39bを熱酸化し、生成した第1および第2酸化膜42、43を選択的にエッチングして、ゲート電極パターンをスリム化する工程と、スリム化された第2保護膜39a、39bを用いてサイズL1、L2のゲート電極18、23を形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】第1および第2のトランジスタ形成領域の各々にゲートを有するトランジスタを備えた半導体装置の製造方法であって、半導体基板の表面がエッチングされて不均一な凹部が生じることを防ぐことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板SB上に絶縁膜ILが堆積される。第2のトランジスタ形成領域R2において金属膜MGが形成される。シリコン膜SGおよびハードマスク膜HMが堆積される。ゲートの平面パターンを有するハードマスク膜HMとシリコン膜SGとの積層膜パターンMPが形成される。第1のトランジスタ形成領域R1が被覆されるように第1のレジスト膜PRiが形成される。第2のトランジスタ形成領域R2において金属膜MGが積層膜パターンMPのハードマスク膜HMをマスクとしてパターニングされる。

(もっと読む)

ディープサブミクロントランジスタ技術用のhigh−k/金属ゲートスタックをパッシベートするためのFベースのゲートエッチングの使用

【課題】プレーナ装置またはマルチゲート装置(MuGFET)のHfベースの誘電体ゲートスタックに、フッ素を導入し、負バイアス温度安定性および正バイアス温度安定性(NBTIおよびPBTI)を大幅に改良する、新規で、効果的で、費用対効果の高い方法を提供する。

【解決手段】新規な方法は、フッ素を導入するためにSF6ベースの金属エッチング化学反応を用い、これにより標準プロセスフローの熱量の後に、界面の優秀なHパッシベーションが得られる。この方法の優位点は、この方法がFを導入するための金属ゲートエッチングを用いて、追加の注入や処理が不要であることである。新たな方法を用いた大幅なBTIの改良に加えて、MuGFET装置において、より良いVthの制御性と増加した駆動電流を得ることができる。

(もっと読む)

半導体素子の製造方法

【課題】ゲートパターンを形成するとき、セル領域のCDは一定に維持しつつ、周辺領域のCDのみ選択的に縮小することができる半導体素子の製造方法を提供すること。

【解決手段】セル領域と周辺領域を有する基板上にゲート用導電物質層を形成するステップと、該ゲート用導電物質層上にハードマスクパターンを形成するステップと、前記セル領域のハードマスクパターンを備える全体構造上に前記周辺領域を露出させるマスクパターンを形成するステップと、前記周辺領域のハードマスクパターンをトリミングするステップと、前記マスクパターンを除去するステップと、前記ハードマスクパターンを用いて前記ゲート用導電物質層をエッチングしてゲートパターンを形成するステップとを含む。

(もっと読む)

多重拡散防止膜を備える半導体素子の製造方法

【課題】ゲートスタックのシート抵抗及びコンタクト抵抗が小さいながらも、不純物の外部拡散を効果的に抑制することのできる拡散防止膜を備える半導体素子の製造方法を提供すること。

【解決手段】本発明に係る半導体素子の製造方法は、第1導電層(21)上に、少なくとも第1金属膜(22A)および窒素含有の金属シリサイド膜(22C)を含む積層構造で拡散防止膜を形成するステップと、該拡散防止膜上に第2導電層(23)を形成するステップとを含む。

(もっと読む)

半導体素子の製造方法

【課題】曲率半径の大きいプロファイルを有するリセスチャンネル構造を効果的に形成することができる半導体素子の製造方法を提供する。

【解決手段】半導体基板310にリセス領域を画成するハードマスク層パターンを形成し、ハードマスク層パターンを食刻マスクに半導体基板を選択食刻してリセスチャンネル構造340を形成し、ハードマスク層パターンを除去してリセスチャンネル構造340を含む半導体基板310を露出し、リセスチャンネル構造を埋め込むゲート電極364を形成する。選択食刻工程は食刻条件が異なる第1の異方性食刻と第2の等方性食刻からなる二段階のプラズマ食刻方法で行なう。

(もっと読む)

半導体装置の製造方法

【課題】 シリサイド膜を有する半導体装置の製造方法に関し、少ない工程数でマスクを形成でき、シリサイド反応の際に半導体素子の性能低下を招く危険性の低いシリサイド作り分け方法を提供する。

【解決手段】 少なくとも一部に露出したシリコン表面を有する半導体基板を準備する工程と、前記半導体基板上に、前記露出したシリコン表面を覆って高融点金属の窒化膜を形成する工程と、少なくとも前記シリコン表面上の窒化膜の一部を選択的に除去し、前記シリコン表面の一部を露出すると共に前記シリコン表面の他の部分を覆う窒化膜パターンを形成する工程と、前記窒化膜パターンを覆って半導体基板上に高融点金属膜を形成する工程と、熱処理を行って、前記シリコン表面の一部とその上の高融点金属膜との間でシリサイド反応を生じさせる工程と、未反応の高融点金属膜およびその下の窒化膜パターンを除去する工程とを含む。

(もっと読む)

エッチング方法

【課題】パターニングが微細であっても、低コストでLWRを低減できるエッチング方法を実現する。

【解決手段】本発明のエッチング方法は、反射防止膜5をエッチングする工程において、エッチングガスとしてHBrガスを用いるので、レジストパターン6aにおけるトリミングの進行が抑制される。したがって、レジストパターン6aはあまり細くならずに、LWRが低減され、パターン4a・5aおよびゲート電極パターン3aの凹凸が従来に比べ改善される。さらに、パターン5a上に新たに膜を形成する工程が不要となるので、コストを抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の上に形成された構造体の配置密度や大きさに不均一性があっても、半導体基板を保護しながら所望の構造体を選択的にエッチングすることができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、(A)シリコン基板10に複数のゲート電極15を形成する工程と、(B)シリコン基板10の全面に、複数のゲート電極15を被覆する有機反射防止膜16を形成する工程と、(C)複数のゲート電極15のうち加工対象であるゲート電極15の上方に開口を有するレジスト17を形成する工程と、(D)前記開口の内側においてシリコン基板10が有機反射防止膜16で被覆された状態を維持しながらレジスト17をマスクとして有機反射防止膜16をエッチングし、加工対象であるゲート電極15を露出させる工程と、(E)前記開口の内側において有機反射防止膜16を残存させながら、加工対象であるゲート電極15をエッチングする工程と、(F)レジスト17と有機反射防止膜16とを除去する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】プラズマエッチング装置を構成する石英部品の寿命を向上させることのできる技術を提供する。

【解決手段】図5はプラズマエッチング装置の上部電極の周囲を絶縁するシールドリングのエッチングガスによる消耗度を示すグラフである。図5の横軸は同心円状をしたシールドリングの内周部からの距離aを示しており、縦軸はシールドリングの肉厚bを示している。実線(1)は、シールドリングの材料として石英だけを用いた場合の例を示しており、実線(2)は、シールドリングの材料として石英にアルミニウムと希土類金属を添加した場合を示している。実線(1)と実線(2)はそれぞれ300時間の稼動時間を経過した後の状態を示している。破線(3)は使用前のシールドリングを示している。

(もっと読む)

半導体装置の作製方法

【課題】レジストを使用することなく、薄膜加工を簡単な工程で精度良く行う方法を提案する。また、低コストで半導体装置を作製する方法を提案する。

【解決手段】基板上に第1の層を形成し、第1の層上に剥離層を形成し、剥離層側から剥離層に選択的にレーザビームを照射して一部の剥離層の付着力を低減させる。次に、付着力が低減された剥離層を除去し、残存した剥離層をマスクとして第1の層を選択的にエッチングする。また、基板上に剥離層を形成し、少なくとも剥離層に選択的に第1のレーザビームを照射して一部の剥離層の付着力を低減させる。次に、付着力が低減された剥離層を除去する。次に、残存した剥離層上に第1の層を形成し、残存した剥離層に第2のレーザビームを照射して残存した剥離層の付着力を低減させ、残存した剥離層及び当該剥離層に接する第1の層を除去する。

(もっと読む)

珪化コバルトを含んだトランジスタゲート、そのトランジスタゲートを含んだ半導体装置構造、前駆構造、および製造方法

珪化コバルトを含んだ導電性要素を持つトランジスタゲートを製造するための方法であって、高温工程(迫り上げ式ソースドレイン領域の作成など)が完了する後までに、トランジスタゲートの側壁スペーサー同士のあいだにて、犠牲材料を仮置きとして用いることを含む。加えて、珪化コバルトをその導電性要素内に有するトランジスタゲートを具えた半導体装置(DRAM装置およびNANDフラッシュメモリ装置など)も開示しており、同様に、迫り上げ式ソースドレイン領域および珪化コバルトをそのトランジスタゲート内に持つトランジスタも開示する。側壁スペーサー同士の上部のあいだに犠牲材料もしくは空隙を持つトランジスタゲートを含んだ、中途半導体装置構造についても開示をしている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】FUSIゲートCMOSトランジスタにおいて、不純物層上シリサイド膜の高抵抗化及び浅接合破壊を共に抑制する。

【解決手段】半導体装置の製造方法は、基板50上に、シリコンからなるゲート電極7及び基板50におけるゲート電極7の両側に位置する不純物層10を備えるトランジスタを形成する工程と、少なくとも不純物層10を覆う第1の金属膜14を形成する工程と、第1の金属膜14を覆い且つゲート電極7に開口を有する絶縁膜16を形成する工程と、ゲート電極7上を含む絶縁膜16上に第2の金属膜17を形成する工程と、第1の金属膜14及び第2の金属膜17に対して熱処理を行なうことにより、不純物層10の上部と、ゲート電極7とを同時にシリサイド化する工程とを備える。

(もっと読む)

完全かつ均一にシリサイド化されたゲート構造体及びそれを形成する方法

【課題】 完全かつ均一にシリサイド化されたMOSゲート構造体を提供すること。

【解決手段】 完全かつ均一にシリサイド化されたゲート導体が、サブリソグラフィの、限界寸法以下の、ナノメートル・スケールの開口部を有するシリサイド・ゲート導体を深く「穿孔」することによって生成される。次に、シリサイド形成金属(例えば、コバルト、タングステン等)がポリシリコン・ゲートの上に堆積され、それらを覆い、穿孔部を充填する。アニール・ステップによって、ポリシリコンをシリサイドに変換する。深い穿孔部のために、シリサイド形成金属と接触しているポリシリコンの表面積は、通常のシリサイド化技術と比べて著しく増加し、ポリシリコン・ゲートを均一なシリサイド組成に完全に変換させる。穿孔部を形成するためのエッチング「テンプレート」として用いられる規則的なサブリソグラフィのナノメートル・スケールのパターンを形成するために、自己組織化型ジブロック・コポリマーが用いられる。

(もっと読む)

半導体装置の作製方法およびレーザ加工装置

【課題】半導体装置の製造工程において、フォトレジストを用いたリソグラフィー工程を簡略化する半導体装置の製造技術を提供して、製造コストを低減し、スループットを向上させる。

【解決手段】基板上に第1材料層、第2材料層を順次積層して被照射体を形成する。当該被照射体に、第1材料層に吸収される第1のレーザビームと、第2材料層に吸収される第2のレーザビームを重畳するように照射し、該重畳するようにレーザビームが照射された領域の一部或いは全部をアブレーションさせ、開口を形成する。

(もっと読む)

ナノチューブを利用した電界効果トランジスタ及びその製造方法

【課題】導電性ナノチューブをゲートとする製作が容易な高集積度のトランジスタ及びその製造方法を提供する。

【解決手段】本発明によるトランジスタは、ナノチューブをゲートとして利用し、製造方法は、ナノチューブをチャンネルパターン時にマスクとして利用する。これにより、50nm以下の線幅を有するトランジスタが得られる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】DRAM素子の微細化を進めた場合における、周辺回路側のトランジスタの短チャネル効果を抑制すると共に、コンタクト抵抗を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1の表面に形成されたMOSトランジスタTr2と、MOSトランジスタTr2のソース108A及びドレイン108Bにそれぞれ接続されるコンタクトプラグ11Aとを具備してなり、コンタクトプラグ11Aが、ソース108A及びドレイン108B上に形成されて不純物が拡散されたエピタキシャル成長層を含んでなることを特徴とする半導体装置を採用する。

(もっと読む)

半導体デバイスのクリティカルディメンジョンを縮小する方法、及び、部分的に作製される縮小クリティカルディメンジョンを有する半導体デバイス

ターゲット層上に加工を形成する方法。加工は、マスクとして使用されるレジスト層の部分のクリティカルディメンジョンと比較して、3倍或いは4倍縮小されたクリティカルディメンジョンを有する。中間層は、ターゲット層上に堆積され、レジスト層は中間層上に形成される。レジスト層をパターン化した後、第一のスペーサは、レジスト層の残っている部分のサイドウォール上に形成され、中間層の一部をマスキングする。第二のスペーサは、中間層の一部のサイドウォール上に形成される。中間層の一部を除去した後、第二のスペーサは、ターゲット層上に加工を形成するため、マスクとして使用される。部分的に作製される集積回路デバイスもまた開示される。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 不純物を添加後の拡散層に対して高温長時間の熱処理を施すことなく、メモリセルの拡散層に対して高温長時間の熱処理を施すことにより、メモリセルにおいては、ワード線抵抗の低抵抗化・リフレッシュ特性の向上等のDRAMに必要な性能を満足しつつ、周辺回路のトランジスタにおいては、ロジックデバイス並みの特性を有する半導体記憶装置及びその製造方法を提供する。

【解決手段】 周辺回路の形成に先立って、メモリセルの電極を形成すると共に、メモリセルの第1のコンタクトを形成する。形成した電極及び第1のコンタクトの上にマスク層を形成する。拡散層上に周辺回路を形成する。形成したマスク層を貫通して第1のコンタクトに接続する第2のコンタクトを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】接合リークの増大を抑制できるとともに、狭いゲート電極間におけるコンタクトの不良の発生、および層間絶縁膜の埋め込み不良の発生を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】まず、ゲート電極4をマスクとしたイオン注入によりLDD領域5が形成される。ゲート電極4の側面に第1のサイドウォール7が形成された後、これらをマスクとしてソース・ドレイン領域8が形成される。ソース・ドレイン領域8上にシリサイド領域を形成する前に、第1のサイドウォール7の側面に第2のサイドウォール10が形成される。ソース・ドレイン領域8にシリサイド領域11が形成された後、第2のサイドウォール10が除去される。これにより、第1のサイドウォール7とシリサイド領域11との間のソース・ドレイン領域8に非シリサイド領域12が設けられる。

(もっと読む)

301 - 320 / 542

[ Back to top ]