Fターム[4M104EE03]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極下 (1,572) | ゲート絶縁膜 (1,401)

Fターム[4M104EE03]に分類される特許

141 - 160 / 1,401

半導体装置

【課題】スイッチング損失を低減した半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、ベース層と、ベース層上に設けられた第2導電形半導体層と、第2導電形半導体層の表面からベース層側に向けて延び、ベース層には達しない複数の第1のトレンチの内壁に設けられた第1の絶縁膜と、第1の絶縁膜を介して第1のトレンチ内に設けられると共に第2導電形半導体層の表面に接する第1の電極とを備えている。第2導電形半導体層は、第1のトレンチで挟まれた第1の第2導電形領域と、第1の第2導電形領域とベース層との間および第1のトレンチの底部とベース層との間に設けられ、第1の第2導電形領域よりも第2導電形不純物量が少ない第2の第2導電形領域とを有する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置を提案することを課題とする。

【解決手段】基板上に形成されたゲート電極と、ゲート電極上に形成された酸素過剰のSiOX膜と、SiOX膜上に形成された酸化物半導体膜と、を有する半導体装置。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

電子装置とその作製方法およびスパッタリングターゲット

【課題】絶縁性酸化物の量産性を高めこと、また、そのような絶縁性酸化物を用いた半導体装置に安定した電気的特性を付与すること、信頼性の高い半導体装置を作製する。

【解決手段】亜鉛のように400〜700℃で加熱した際にガリウムよりも揮発しやすい材料を酸化ガリウムに添加したターゲットを用いて、DCスパッタリング、パルスDCスパッタリング等の大きな基板に適用できる量産性の高いスパッタリング方法で成膜し、これを400〜700℃で加熱することにより、添加された材料を膜の表面近傍に偏析させる。膜のその他の部分は添加された材料の濃度が低下し、十分な絶縁性を呈するため、半導体装置のゲート絶縁物等に利用できる。

(もっと読む)

薄膜トランジスタの製造方法および薄膜トランジスタ

【課題】UV露光でも電気的絶縁性が損なわれず、表面濡れ性の変化を利用して印刷法でソース・ドレイン電極のパターニングが可能なゲート絶縁層を有する薄膜トランジスタの製造方法を提供する。

【解決手段】基板7上にゲート電極42およびゲート絶縁層2が順次形成され、該ゲート絶縁層が形成されたゲート電極上に適宜の間隔でソース電極5aおよびドレイン電極5bが対向配置され、該間隔を含む領域に半導体層6が形成された薄膜トランジスタを、活性水素基と反応可能なメラミン誘導体および活性水素基を有する樹脂を含有する溶液を塗布・焼成し、紫外線照射で表面濡れ性が可変のゲート絶縁層を形成し、紫外線照射で該ゲート絶縁層の露光部位を親水性域に変え、親水性域に電極材料含有溶液を印刷法で塗布・乾燥し、ソース電極及びドレイン電極を形成して薄膜トランジスタを形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 複合酸化物の単結晶をチャンネルに用いたFETに電界効果のみで1013cm-2以上の高濃度のキャリアを注入することと、キャリアの移動度が室温でも10cm2/Vsに達するほどに理想的なチャンネルとの界面を得ることを共に可能にするゲート絶縁膜を有する電界効果トランジスタ及びその製造方法を提供することを目的とする。

【解決手段】 チャンネル層を構成するペロブスカイト構造の複合酸化物単結晶基板と、該複合酸化物単結晶基板上にパラキシリレンのポリマー膜及び酸化タンタルがこの順に積層された積層構造からなるゲート絶縁膜とを有する電界効果トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にhigh−k膜を使用したMIS構造の半導体装置において、互いに異なる仕事関数を有する複数の同一導電型トランジスタを設けることを可能にする。

【解決手段】同じ導電型の第1のMISトランジスタ及び第2のMISトランジスタが同じ半導体基板50上に設けられている。第1のMISトランジスタにおけるゲート絶縁膜52aの界面層2Aの厚さは、第2のMISトランジスタにおけるゲート絶縁膜52bの界面層2bの厚さよりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11上に、ダミーゲート電極及びダミーコンタクトプラグの側面を覆う層間絶縁膜16を形成後、ダミーゲート電極、ダミーコンタクトプラグを選択的に除去して、ゲート電極形成用溝17及びコンタクト孔18を同時に形成し、次いで、ゲート電極形成用溝17内、コンタクト孔18内、及び層間絶縁膜16の上面を覆う高誘電率絶縁膜42を成膜し、次いで、斜めイオン注入法により、ゲート電極形成用溝17の下部17Aに形成された高誘電率絶縁膜42にイオン注入しないように、高誘電率絶縁膜42を介して、半導体基板に不純物拡散領域15を形成し、次いで、イオン注入された高誘電率絶縁膜42を選択的に除去することで、ゲート電極形成用溝の下部にゲート絶縁膜を形成し、かつコンタクト孔から不純物拡散領域15の上面を露出させる。

(もっと読む)

トレンチゲート型トランジスタの製造方法

【課題】トレンチゲート型トランジスタの製造方法において、ゲート容量の低減、結晶欠陥の発生の抑止、及びゲート耐圧の向上を図る。

【解決手段】N−型半導体層12の表面にトレンチ14を形成し、該表面とトレンチ14内に、熱酸化によりシリコン酸化膜15Aを形成し、これを覆うホトレジスト補強膜16、及びホトレジスト補強膜16を覆うホトレジスト層R2を形成する。そしてホトレジスト層R2及びホトレジスト補強膜16をエッチバックしてトレンチ14内にのみに残す。このホトレジスト層R2及びホトレジスト補強膜16をマスクとして、トレンチ14の側壁の上方のシリコン酸化膜15Aをエッチングして除去する。上記マスクを除去した後、熱酸化により、トレンチ14の側壁の上方にシリコン酸化膜15Aより薄いシリコン酸化膜15Bを形成する。その後、シリコン酸化膜15A,15B上にゲート電極18を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜にハフニウムを含む絶縁膜を使用したMISFETを有する半導体装置において、MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】本発明では、nチャネル型コア用トランジスタQ1のゲート絶縁膜と、pチャネル型コア用トランジスタQ2のゲート絶縁膜の構成を相違させている。具体的に、nチャネル型コア用トランジスタQ1では、ゲート絶縁膜に酸化シリコン膜SO1とHfZrSiON膜HK1の積層膜を使用している。一方、pチャネル型コア用トランジスタQ2では、ゲート絶縁膜に酸化シリコン膜SO1とHfSiON膜HK2の積層膜を使用している。

(もっと読む)

成膜方法、半導体装置及びその製造方法、並びに基板処理装置

【課題】真空装置を使用せずに、トランジスタ等の半導体装置に適用できるMOS構造の積層膜を形成する。

【解決手段】成膜方法は、半導体膜3を有する基板に、ポリシラン溶液を塗布し、半導体膜3上にポリシラン膜5を形成する工程(STEP1)と、ポリシラン膜5上に、金属塩溶液を塗布し、金属イオン含有膜7を形成することにより、ポリシラン膜5をポリシロキサン膜5Aへ、金属イオン含有膜7を金属微粒子含有膜7Aへ、それぞれ改質する工程(STEP2)を備え、MOS構造の積層膜100を形成する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置及びその製造方法

【課題】生産性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、シリコン基板101と、同一のシリコン基板101上に設けられたN型トランジスタ200およびP型トランジスタ202と、を備え、N型トランジスタ200およびP型トランジスタ202は、Hfを含む高誘電率ゲート絶縁膜108と、高誘電率ゲート絶縁膜108上に設けられたTiN膜110と、を有しており、N型トランジスタ200は、シリコン基板101と高誘電率ゲート絶縁膜108との間に、La添加SiO2膜109aを有しており、P型トランジスタ202は、高誘電率ゲート絶縁膜108とTiN膜110の間に、N型トランジスタ200と同じ仕事関数調整用元素を含有するLa添加SiO2膜109bを有する。

(もっと読む)

有機薄膜トランジスタ及びこれを備えた平板表示装置

【課題】有機薄膜トランジスタ及びこれを備えた平板表示装置を提供する。

【解決手段】基板の一面上に形成されるソース/ドレイン電極及び有機半導体層と、ソース/ドレイン電極及び有機半導体層と絶縁されるゲート電極と、ソース/ドレイン電極と前記ゲート電極との間に一層以上のゲート絶縁層と、を備え、ソース/ドレイン電極と前記ゲート電極との交差領域のうち少なくとも一部でのゲート絶縁層の厚さは、有機半導体層のチャンネル領域とゲート電極との交差領域のうち少なくとも一部でのゲート絶縁層の厚さ以上とした。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

有機薄膜トランジスタ及びその製造方法

【課題】大気雰囲気下であっても酸化されにくく、機能的にも劣化しにくい電荷注入層を備えた有機薄膜トランジスタを提供する。

【解決手段】ゲート電極20Aと、第1のソース/ドレイン電極60Aと、第2のソース/ドレイン電極60Bと、前記第1および第2のソース/ドレイン電極と前記ゲート電極との間に設けられる有機半導体層40と、前記第1および第2のソース/ドレイン電極と前記有機半導体層の間において、前記第1および第2のソース/ドレイン電極に接して配置される電荷注入層50とを備える有機薄膜トランジスタ10において、前記電荷注入層は、電荷注入特性を有するイオン性ポリマーを含有する、有機薄膜トランジスタ。

(もっと読む)

半導体装置およびその制御方法

【課題】リカバリ損失の低減が図れ、かつ、ノイズによるセルフターンオンが生じ難い構造の半導体装置を提供する。

【解決手段】ゲート電極8を深さの異なる第1、第2ゲート電極8a、8bを備えたダブルゲート構造とする。このような構造では、第1、第2ゲート電極8a、8bのうちの第1ゲート電極8aのみをオンさせることで、p型ベース領域3に対して反転層を形成しながらも、その反転層がn-型ドリフト層2とn+型不純物領域4とを繋ぐ深さまでは形成されないようにすることができる。この第1ゲート電極8aを過剰キャリア注入抑制ゲートとして機能させる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

電子デバイス及びその製造方法、並びに、半導体装置及びその製造方法

【課題】従来よりも低い温度での形成が可能である絶縁層を備えた電子デバイスを提供する。

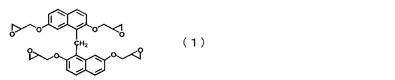

【解決手段】電子デバイスは、(A)制御電極12、(B)第1電極14及び第2電極14、並びに、(C)第1電極14と第2電極14との間であって、絶縁層13を介して制御電極12と対向して設けられた、有機半導体材料層15から成る能動層16を備えて成り、少なくとも能動層12と接触する絶縁層13の部分は、下記の式(1)にて示される材料を硬化して成る層から構成されている。 (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜とメタルゲート電極を有するCMISFETを備えた半導体装置において、nチャネル型MISFETおよびpチャネル型MISFETのしきい値電圧の上昇を防ぐことができる技術を提供する。

【解決手段】CMISFETのしきい値を調整する目的で、高誘電率ゲート絶縁膜であるHf含有絶縁膜5に希土類元素またはアルミニウムを導入する際に、酸素をほとんど含まないランタン膜からなるしきい値調整層8bおよび酸素をほとんど含まないアルミニウム膜からなるしきい値調整層8aをnMIS形成領域1BおよびpMIS形成領域1AのHf含有絶縁膜5上にそれぞれ形成する。これにより、しきい値調整層8aおよびしきい値調整層8bからHf含有絶縁膜5および半導体基板1の主面に酸素が拡散することを防ぐ。

(もっと読む)

141 - 160 / 1,401

[ Back to top ]