Fターム[4M104EE03]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極下 (1,572) | ゲート絶縁膜 (1,401)

Fターム[4M104EE03]に分類される特許

101 - 120 / 1,401

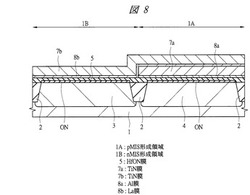

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

フローティングゲート半導体メモリデバイスおよびそのようなデバイスの製造方法

【課題】NANDフラッシュメモリデバイスを電気的、物理的に小型化し、良好なデータ保持と電気的特性を備えたフローティングゲートデバイスを提供する。

【解決手段】フローティングゲートメモリデバイスの製造方法に関し、ベース基板100、埋め込み絶縁層、および単結晶半導体上部層から形成される、半導体−オン−絶縁体基板が提供される。トレンチが基板中に形成され、フローティングゲートとして働く単結晶上部部分を有する高層フィン型構造111−114を形成する。埋め込み絶縁層の一部は、フローティングゲートデバイスのトンネル酸化物層101’として働く。ゲート誘電体層160は、熱酸化により単結晶上部部分の側壁の上に形成され、薄い膜厚のゲート誘電体層を可能にする。

(もっと読む)

半導体装置

【課題】p型SiC領域と金属との低抵抗コンタクトの実現を可能とする半導体装置を提供する。

【解決手段】実施形態の半導体装置は、導電性材料を用いた電極240と、導電型がp型の炭化珪素(SiC)半導体部220と、を備えており、かかるp型のSiC半導体部220は、前記第1の電極240に接続され、マグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)、及びバリウム(Ba)のうちの少なくとも1種類の元素が前記電極との界面部に面密度がピークになるように含有されたことを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜を有する窒化物半導体を低コストで製造する。

【解決手段】基板10の上方に形成された半導体層22,23,24と、前記半導体層の一部を酸化することにより形成された絶縁膜30と、前記絶縁膜上に形成された電極41と、を有し、前記絶縁膜は、酸化ガリウムを含むもの、または、酸化ガリウム及び酸化インジウムを含むものにより形成されているものであることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

半導体装置およびその製造方法

【課題】より良質なゲート電極を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、ドレイン層と、前記ドレイン層の上に設けられたドリフト領域と、前記ドリフト領域の上に設けられたベース領域と、前記ベース領域の表面に選択的に設けられたソース領域と、前記ソース領域から前記ベース領域を貫通し、前記ドリフト領域に到達するトレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、前記ドレイン層に接続された第1主電極と、前記ソース領域および前記ベース領域に接続された第2主電極と、を備える。前記ゲート電極は、第1導電層と、前記第1導電層と前記ゲート絶縁膜との間に介在する第2導電層と、を含み、前記第2導電層の不純物濃度は、前記第1導電層の不純物濃度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

薄膜トランジスタ用ゲート絶縁膜および該絶縁膜を備えた薄膜トランジスタ素子

【課題】低温条件下かつ溶液塗布プロセスにより形成可能であり、薄膜トランジスタにおける電気特性であるヒステリシス、On/Off比が良好な薄膜トランジスタ用ゲート絶縁膜及び該絶縁膜を備えた薄膜トランジスタを提供する。

【解決手段】必須成分として(A)アルケニル基を有する化合物、(B)SiH基を有する化合物、(C)ヒドロシリル化触媒を含有する硬化性組成物を低温条件下によるポストベイクしたゲート絶縁膜を用いることにより、良好なトランジスタ特性が発現する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

101 - 120 / 1,401

[ Back to top ]