Fターム[4M104EE03]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極下 (1,572) | ゲート絶縁膜 (1,401)

Fターム[4M104EE03]に分類される特許

201 - 220 / 1,401

薄膜トランジスタ及びその製造方法

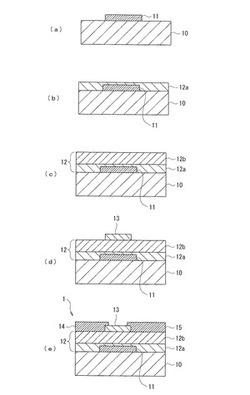

【課題】基板の表面粗度によらず膜表面が平坦であり、信頼性が高く、製造コストを低減させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】可撓性のプラスチック基板10上に、ゲート電極11、ゲート絶縁層12、半導体活性層13、ソース電極14、及びドレイン電極15を順次形成するボトムゲート型薄膜トランジスタ1の製造方法である。ゲート絶縁層12は、プラスチック基板10上に下部層12aと該下部層12a上に積層された少なくとも一層以上の上部層12bとがこの順で形成されてなり、下部層12aは、炭素含有酸化シリコンを含む材料からなり、下部層12aの炭素濃度が、15atm%以上40atm%以下となるように真空紫外光CVD法により形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

ナノワイヤトランジスタ及びその製造方法

【課題】動作不良や動作速度の低下の発生を従来よりも抑制できるナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】窒素が導入されたニッケルからなるニッケル層28をナノワイヤ5の周辺に形成して熱処理することにより、ナノワイヤ5に形成されたソース15及びドレイン16をシリサイド化させつつ、窒素によりゲート電極被覆領域ER1までシリサイド化されることを抑制できることから、従来よりもゲート電極被覆領域ER1にチャネル17を確保でき、かくして動作不良や動作速度の低下の発生を従来よりも抑制できる。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ゲート電極が金属窒化膜により構成されるMOSFETにおいて、電流駆動能力の向上を図る。

【解決手段】基板10に、素子形成領域20を分離する素子分離領域50を設ける。次に素子形成領域20上にゲート絶縁膜100を形成する。その後ゲート絶縁膜100上に金属窒化膜により構成される下部ゲート電極膜200を形成する。さらに下部ゲート電極膜200を熱処理する。そして下部ゲート電極膜200上に上部ゲート電極膜220を形成する。

(もっと読む)

金属窒化膜、該金属窒化膜を用いた半導体装置、および半導体装置の製造方法

【課題】所望の実効仕事関数(例えば、高い実効仕事関数)を実現し、かつ、EOTが変化しない、またはEOTの変化を低減した金属窒化膜、金属窒化膜を用いた半導体装置、および半導体装置の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る金属窒化膜は、TiとAlとNを含有し、該金属窒化膜のTiとAlとNのモル比率(N/(Ti+Al+N))が0.53以上であり、かつ、上記金属窒化物層のTiとAlとNのモル比率(Ti/(Ti+Al+N))が0.32以下であり、かつ上記金属窒化物層のTiとAlとNのモル比率(Al/(Ti+Al+N))が0.15以下である。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

トランジスタおよびその製造方法

【課題】高い電流駆動力と高いカットオフ特性を備えたトランジスタおよびその製造方法を提供する。

【解決手段】本発明の一態様に係るトランジスタ100は、導体領域10aと表面に原子が結合した半導体領域10bとを有し、チャネルとして機能するグラフェン膜10と、グラフェン膜10上にゲート絶縁膜11を介して形成されたゲート電極12と、を有し、導体領域10aと半導体領域10bが形成するショットキー接合のトンネル電流をスイッチング動作に用いる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

有機薄膜トランジスタの製造方法、有機薄膜トランジスタレイの製造方法及び表示装置の製造方法

【課題】有機薄膜トランジスタを高い歩留まりで製造する製造方法を提供する。

【解決手段】基板上又は基板上における絶縁膜上にソース電極及びドレイン電極を形成する電極形成工程と、有機半導体インクが供給された際、前記ソース電極及び前記ドレイン電極上における前記有機半導体インクの接触角を前記基板上又は前記絶縁膜上における接触角よりも高くする電極処理工程と、形成された前記ソース電極及び前記ドレイン電極の間に前記有機半導体インクを供給することにより有機半導体層を形成する半導体層形成工程と、を有し、前記ソース電極と前記ドレイン電極とにより形成されるチャネルのチャネル幅をW、前記有機半導体インクが供給される際の液滴の液滴径をφ、前記液滴が供給される位置の誤差である着弾位置誤差幅をXとした場合、W>φ+Xを満たしていることを特徴とする有機薄膜トランジスタの製造方法を提供することにより上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値電圧が低く、かつ、ゲート絶縁膜のリーク電流を抑制可能な半導体装置およびその製造方法を提供する。

【解決手段】メタルゲート電極103,203の材料として、Ta3N5を含むTaxNy膜18,38を用いる。TaxNy膜18,38中には多くの窒素が含まれており、その窒素の一部がゲート絶縁膜102,202中に拡散することにより、TiNに比べてフラットバンド電圧Vfbが高くなり、NMOSFET100およびPMOSFET200の閾値電圧Vthを低くすることができる。また、TaxNy膜18,38中の窒素がHfSiON膜17,37中に拡散することにより、ゲート絶縁膜の絶縁性を高くすることができ、ゲートリーク電流Jgを抑制できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】絶縁性が高く、かつ均一な膜厚を有するゲート絶縁膜を効率よく形成することができる電界効果型トランジスタの製造方法、及び該電界効果型トランジスタの製造方法により製造され、安定した特性を有する高性能な電界効果型トランジスタの提供。

【解決手段】前記第一の基材上にゲート電極を形成するゲート電極形成工程と、第二の基材上にゲート絶縁膜形成用樹脂溶液を塗布し、ゲート絶縁膜を形成する塗布工程と、前記ゲート絶縁膜表面の流動性が消失するまで乾燥する乾燥工程と、前記ゲート電極と、前記ゲート絶縁膜表面とを接触させて接触体を形成する接触工程と、前記接触体に対し、ゲート絶縁膜形成用樹脂のガラス転移温度以上の熱を加える加熱工程と、前記接触体から前記第二の基材を剥離し、第一の基材上にゲート絶縁膜を形成する剥離工程とを少なくとも含む電界効果型トランジスタの製造方法である。

(もっと読む)

IGZO系アモルファス酸化物薄膜の製造方法及びそれを用いた電界効果型トランジスタの製造方法

【課題】導電体領域から絶縁体領域までの範囲内で所望の電気抵抗値有し、且つ、電気的ストレスに対して安定性の良好なIGZO系アモルファス酸化物薄膜を製造する

【解決手段】IGZO系アモルファス酸化物薄膜を基板上にスパッタ成膜し、その後アニール処理してIGZO系アモルファス酸化物薄膜を製造する方法であって、成膜装置内の水分量とアニール処理の温度の組み合わせを変化させて、導電体領域から絶縁体領域の範囲内の任意の電気抵抗値を有するアモルファス酸化物薄膜を製造する。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】メモリ混載ロジックデバイスのRAM領域の閾値電圧のばらつきを低減する。

【解決手段】本発明の半導体装置は、ロジック領域101と、RAM領域102とが設けられたシリコン基板1と、ロジック領域101に形成されたNMOSトランジスタ20と、RAM領域102に形成されたNMOSトランジスタ40と、を備える。NMOSトランジスタ20、40は、ゲート絶縁膜5とメタルゲート電極6との順でシリコン基板1上に積層された積層構造を有する。NMOSトランジスタ20は、シリコン基板1とメタルゲート電極6との間に、構成元素として、ランタン、イッテルビウム、マグネシウム、ストロンチウム及びエルビウムからなる群から選択される元素を含む、キャップメタル4を有する。NMOSトランジスタ40には、キャップメタル4が形成されていない。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

201 - 220 / 1,401

[ Back to top ]