Fターム[4M104FF30]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクト面の位置、配置 (799) | ダイレクトコンタクト (46)

Fターム[4M104FF30]に分類される特許

21 - 40 / 46

半導体装置およびその製造方法

【課題】開口径の異なるコンタクトが混在することによる歩留りの低下を抑えることが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板11に形成された所定パターンの活性領域12と、半導体基板11上の所定位置に形成されたゲート電極14と、半導体基板11上に形成された層間膜16aと、中央部において幅が極小となる開口形状を有し、層間膜16aを貫通して活性領域12およびゲート電極14と接続されるシェアードコンタクト17を備える

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造の小型化に対応しやすく、製造が容易な3次元構造のゲート絶縁膜を有する半導体装置の提供を課題とする。

【解決手段】本発明の半導体装置は、半導体基板に3次元構造のゲート絶縁膜が形成され、ゲート絶縁膜に接するゲート電極が半導体基板上に突出形成され、ゲート絶縁膜の周囲の半導体基板に該半導体基板の拡散層領域を介してソース電極およびドレイン電極が形成され、ゲート電極周囲の半導体基板上面が、半導体基板上に突出形成されたゲート電極の側面を覆う保護絶縁膜で覆われ、この保護絶縁膜の上に層間絶縁膜が積層されてなる。

(もっと読む)

窒化物半導体装置

【課題】 耐圧が高く、且つオン電圧の低い、III−V族窒化物半導体装置を提供する。

【解決手段】 半絶縁性または絶縁性基板上に積層した窒化物半導体からなる第1および第2の窒化物半導体層と、第2の窒化物半導体層よりも低い温度で成膜した第3の窒化物半導体層と、凹部内に露出する第1の窒化物半導体層上にショットキー接合するショットキーバリア高さの低い第1アノード電極と、第1アノード電極に接続し、第3の窒化物半導体層にショットキー接合する第1アノード電極と同一あるいは異なる金属からなり、ショットキーバリア高さの高い第2アノード電極と、第1、第2あるいは第3の窒化物半導体層にオーミック接合するカソード電極とを備える。

(もっと読む)

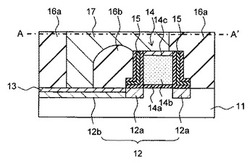

半導体装置

【課題】SRAMやフラッシュメモリ等のメモリやロジックに用いられる、コンタクトや配線をできるだけ省略し、構造を簡略化することによって半導体装置の高集積化を図り、かつ、生産性を向上させるMOS型半導体装置を提供する。

【解決手段】MOS型半導体装置10では、半導体基板11と、半導体基板11にウェル領域12を備え、かつ、ゲート15とソース13/ドレイン14とを有し、ソース13の上部を形成するソース電極133が、ソース13を形成する拡散領域131を通過して、ウェル領域12又はボディ領域111に貫通していて、かつ、ドレイン14の上部を形成するドレイン電極は、ウェル領域12又はボディ領域111を貫通していない。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクト領域での過剰なエッチングを防止する。

【解決手段】DSLで使用するSiNライナをシェアードコンタクト領域において順次に堆積させて積層体として残す。

(もっと読む)

実質的に均一なパターン密度で形成された回路を有する半導体デバイス

半導体デバイスは、導電層から形成された少なくとも3つの導電配線(202、204、206)に結合された少なくとも1つのトランジスタ(T1)を有する第1の回路部分(200A)を含む。3つの導電配線のうちの1つ(204)は前記少なくとも1つのトランジスタの制御端子を形成する。また、第2の回路部分(200B)は、少なくとも2つのトランジスタ(T3−T6)を含む。該少なくとも2つのトランジスタの各々は、同一の導電層から形成された導電配線(234、236、238、240)によって形成された制御端子を有する。第1の回路部分の前記3つの導電配線は、第2の回路部分の導電配線群と同一のピッチパターンを有する。  (もっと読む)

(もっと読む)

不揮発性メモリのウェルピックアップ構造を製造する方法

【課題】 不揮発性メモリのウェルピックアップ構造を製造する方法を提供する。

【解決手段】 第1の導電型のウェル、デバイス分離構造及びダミーメモリ列を備える基板を提供する。ダミーメモリ列の各々は、第2の導電型のソース領域及び第2の導電型のドレイン領域を備える。基板の上に、開口を有する第1の層間絶縁層が形成され、その開口は、2つの隣接する第2の導電型のドレイン領域と、2つの隣接する第2の導電型のドレイン領域の間のデバイス分離構造とを露出させる。開口によって露出されたデバイス分離構造の一部が除去された後、開口によって露出された基板に第1の導電型のウェル延長ドープ領域が形成される。開口に、ウェルピックアップ導電層が形成される。基板の上に、ウェルピックアップ導電層を電気的に接続するダミービット線が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】PN接合の太陽電池効果による配線の腐食及び再堆積を抑制する。

【解決手段】半導体装置は、Pウェル103上に形成されたN型不純物拡散層106とNウェル104上に形成されたP型不純物拡散層108とを電気的に接続するシェアードコンタクト111を備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】例えば全体の製造コストを低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置200は、半導体基板110と、ポリシリコン層30と、サイドスペーサ40と、第1シリサイド層262と、第2シリサイド層263と、金属膜261とを備える。半導体基板110は、拡散層14を有する。ポリシリコン層30は、半導体基板110の上において、拡散層14の付近に形成されている。サイドスペーサ40は、半導体基板110の上において、拡散層14とポリシリコン層30との間に形成されている。第1シリサイド層262は、拡散層14の上に自己整合的に形成されている。第2シリサイド層263は、ポリシリコン層30の上に自己整合的に形成されている。金属膜261は、第1シリサイド層262と第2シリサイド層263とを接続するように連続して延びている。

(もっと読む)

半導体デバイス

【課題】金属−絶縁物−半導体電界効果トランジスタの製造において、基板材料のバンドギャップの中間付近の仕事関数を有し、フッ素による問題を除去し、ボロンのしみ込みを防ぎ、また、複雑かつ余計な工程段階を使用することのない、ゲート電極を形成する。

【解決手段】金属半導体窒化ゲート電極(40、70)が、半導体デバイス(60)において使用するために形成される。ゲート電極(40、70)は、スパッタデポジション、低圧化学蒸着(LPCVD)またはプラズマエンハンスト化学蒸着(PECVD)により形成できる。その材料は、シリコン含有化合物の類をエッチングし、従来のハロゲン基エッチング化学物質にエッチングされる。金属半導体窒化ゲート電極(40、70)は、比較的安定であり、従来のゲート電極よりも比較的薄く形成できる。また、基板(12)の物質のバンドギャップの中間付近の仕事関数を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】エクステンション領域がゲート電極の下側に広がることがなく且つシェアードコンタクトを形成する際に接合リーク電流が発生するおそれがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10における素子分離領域11に囲まれた部分に形成された活性領域12と、活性領域12の上に形成されたゲート絶縁膜21A及び第1のゲート電極膜22Aを有する第1のゲート構造23Aと、第1のゲート構造23Aの側面上に形成され、第1のゲート構造23Aよりも高さが低い第1のオフセットスペーサ24Aと、第1のゲート構造23Aの側面上に、第1のオフセットスペーサ24Aの側面及び上端面を覆うように形成された第1のサイドウォール25Aとを備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】MISトランジスタを有する半導体装置の歩留りを向上することが可能な技術を提供する。

【解決手段】半導体層80における半導体基板1の上面1a上には、MISトランジスタのゲート構造4cが形成されている。また、半導体層80における半導体層8の上面8a内にはソース・ドレイン領域9が形成されている。半導体層80上には、ゲート構造4cを覆って層間絶縁膜20が形成されている。層間絶縁膜20内には、ゲート構造4cに含まれるゲート電極6の上面6aと、半導体層8の上面8aとの両方に接続されたコンタクトプラグ23が形成されている。そして、半導体層8の上面8aは、活性領域100cにおける半導体基板1の上面1aよりも上方に位置している。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

半導体装置およびその製造方法

【課題】ポリメタルゲート構造を有し、且つソース・ドレイン領域上にコンタクト用の金属シリサイド層を有しながら、簡便なプロセスで製造可能な半導体装置を提供する。

【解決手段】シリコン基板と、素子分離絶縁膜と、活性領域と、ゲート絶縁膜を介して設けられたゲート電極と、ゲート電極両側の活性領域に設けられた拡散層と、層間絶縁膜と、層間絶縁膜に形成された開孔に充填されたプラグを有する半導体装置であって、素子分離絶縁膜に囲まれたコンタクト形成用領域と、このコンタクト形成用領域に形成された導電層をさらに有し、ゲート電極は、コンタクト形成用領域の一部に重なるように延在し、この重なり部分で前記導電層と接続され、前記プラグは、コンタクト形成用領域の他の部分で前記導電層に接触し、この導電層を介してゲート電極と電気的に接続されている半導体装置。

(もっと読む)

半導体装置とその製造方法

【課題】MISトランジスタを有する半導体装置において、微細化及び製造歩留りの向上を実現する。

【解決手段】半導体装置は、基板101上にゲート絶縁膜103を介して形成されたゲート電極117と、基板101におけるゲート電極117の両側に形成されたソース領域及びドレイン領域107bとを有するMISトランジスタを備え、ゲート電極117は金属シリサイドからなり、ソース領域及びドレイン領域107bの少なくとも一方の上に、金属シリサイドからなる第1のコンタクト電極116を備える。

(もっと読む)

炭素含有膜エッチング方法及びこれを利用した半導体素子の製造方法

【課題】炭素含有膜エッチング方法及びこれを利用した半導体素子の製造方法を提供する。

【解決手段】炭素含有膜上に炭素含有膜の上面を一部露出させるマスクパターンを形成し、マスクパターンをエッチングマスクとして利用して、O2、及びSi含有ガスからなる混合ガスのプラズマによって炭素含有膜を異方性エッチングする炭素含有膜エッチング方法である。これにより、高密度セルアレイ領域で互いに隣接した2個のコンタクトホールの間隔が数十nmまたはそれ以下のレベルに小さくなっても、コンタクトホールが互いに良好に分離して隣接した単位セル間の短絡が防止される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を微細化するとともに、ゲート電極と不純物拡散領域とを接続する共通コンタクトにおける電流リークを抑制する。

【解決手段】半導体装置100は、第1のゲート電極108と、第4のソース・ドレイン領域114bと、これらを電気的に接続する共通コンタクト112と、を含む。ゲート長方向の断面において、第1のゲート電極108と第4のソース・ドレイン領域114bとが離間して設けられるとともにこれらの間の半導体基板160表面全面に素子分離絶縁膜102が形成され、第1のゲート電極108と第4のソース・ドレイン領域114bとの間の距離が、ゲート長方向の他の断面における第1のゲート電極108側壁に形成されたサイドウォールの幅と実質的に等しい。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域の微細化が図れ、且つ、隣接する活性領域間を自己整合的に接続できる半導体装置及びその製造方法を提供する。

【解決手段】第1の活性領域R10と第2の活性領域R20との間に形成されている溝型素子分離領域2のうち、ゲート電極4abの両側に位置する領域の一方側に凹部2Aが形成されている。この凹部2Aは、ソース・ドレイン領域6aとソース・ドレイン領域6bに挟まれている。そして、絶縁性サイドウォール5abの側方下に位置する溝型素子分離領域2に設けられた凹部2Aの側壁上にはシリサイド層7dがサイドウォール形状に形成されている。このシリサイド層7dは、シリサイド層7a及びシリサイド層7bと一体的に形成されている。これにより、ソース・ドレイン領域6aとソース・ドレイン領域6bは、シリサイド層7a,7b,7dを介して電気的に接続されている。

(もっと読む)

半導体装置

【課題】 電流密度の部分的な集中を防止して、より小面積でより大電流を駆動可能にする。

【解決手段】 複数の半導体素子を並列に接続する第1配線16及び第2配線17を、複数の配線層により構成する。各配線層は、第1配線16及び第2配線17を交互に且つ平行に形成してなる。隣接する配線層間では、上下の配線が互いに交差するように形成されると共に、第1配線16の交差部及び第2配線17の交差部でそれぞれ第1配線16同士及び第2配線17同士が層間接続部165,166,175,176によって接続されている。

(もっと読む)

ワイドバンド半導体のオーミック接続形成方法

【課題】ワイドバンドギャップ半導体材料からなる基板へのオーミック接続形成方法を提供する。

【解決手段】基板10への遷移金属群金属12の堆積、基板10と堆積金属12の間で固相化学反応を起こし、基板10中に基板10とは異なる変質特性を有する変質層14、および珪化物18とナノ結晶グラファイト層16からなる副生物を形成する基板10の高温でのアニール、一もしくはそれ以上の固相化学反応の副生物を基板10の表面から除去するための基板10の選択的エッチング、オーミック接続を形成するための基板10上の変質層14を覆う遷移群金属からなる金属膜20の堆積、を含んでいる。変質層14は、金属膜20の堆積後に高温のアニールを必要とせずに、オーミック接続の形成を可能とする。

(もっと読む)

21 - 40 / 46

[ Back to top ]