Fターム[4M104FF32]の内容

Fターム[4M104FF32]に分類される特許

61 - 80 / 230

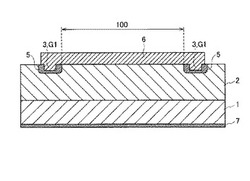

異種材料接合型ダイオード及びその製造方法

【課題】電流電圧特性を維持しつつ、アノード電極6の剥離に対する機械的強度を向上させる。

【解決手段】異種材料接合型ダイオードは、半導体基体1と、半導体基体1の上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主表面に接合された、ドリフト領域2とは異なる種類の材料からなるアノード電極6と、半導体基体1に接続されたカソード電極7とを備える。ドリフト領域2とアノード電極6との接合によりダイオードが形成されている。アノード電極6の主表面のうち、ドリフト領域2に接している側の主表面に、嵌合構造(3、G1)が形成されている。

(もっと読む)

半導体装置

【課題】小数キャリアの注入量により少数キャリアを引き抜くための時間を適宜設定可能な構成とし、重金属拡散等の技術を利用することなく、低VF特性と、短Trr、低Qrrを、デバイスの使用目的及び態様等に応じて最適化する。

【解決手段】半導体基板31の上に形成された低不純物濃度の第1導電型である第1半導体層32と、第2導電型であるガードリング33と、第2導電型である複数の島状の第3半導体層35と、第1半導体層32の上面の一部の領域に形成された第1のバリアメタル45と、第1半導体層32及び複数の第3半導体層35の上に形成された第1のバリアメタル42の第1のバリアハイト41より高い第2バリアメタル43、45を備えている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】熱処理装置のメンテナンス頻度を低減できると共に、電極表面荒れを防止しつつオーミックコンタクトの低抵抗化を図る炭化珪素半導体装置の製造方法を提供する。

【解決手段】P型SiC層10上に電極材料としてのAl−Ti合金11を堆積し、その上にTiNの保護膜12を形成する。その後、Alの融点を超える温度の熱処理を行い、Al−Ti合金11をP型SiC層10と反応させて合金化し、電極とP型SiC層10とのオーミックコンタクトを得る。保護膜12により、上記熱処理においてAl−Ti合金11からのAlの蒸発・飛散が防止される。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】ワイドバンドギャップ半導体デバイスにおいて、金属/ワイドバンドギャップ半導体界面を有する装置の逆方向電圧印加時のリーク電流の増加や、オン抵抗の増加を抑制する。

【解決手段】第1導電型の高濃度ワイドバンドギャップ半導体基板と、半導体基板上に形成された第1導電型の低濃度のワイドバンドギャップ半導体堆積膜と、半導体堆積膜上に形成され、半導体堆積膜との間でショットキー界面領域を構成する金属膜8と、該第1導電型の低濃度のワイドバンドギャップ半導体堆積膜の金属膜周辺部に対応する領域に形成された第2導電型の領域4,5とを含み、該第1導電型の低濃度のワイドバンドギャップ半導体堆積膜における該ショットキー界面領域は、第2導電型の領域に囲まれて複数個の周期的な島領域を構成する。

(もっと読む)

半導体装置の製造方法

【課題】非酸化雰囲気下でなくても、良好なオーミック電極を形成可能な技術を提供する。

【解決手段】オーミック電極を有する半導体装置の製造方法であって、半導体基板50上に金属層30eを形成する工程と、金属層30e上に透過膜30fを形成する工程と、透過膜30fを通して金属層30eに電磁波を照射して、金属層30eを加熱する工程と、透過膜30fを除去する工程を有する。

(もっと読む)

エピタキシャルシリコン成長方法

【課題】低抵抗高耐圧のトランジスタとダイオードを提供する。

【解決手段】直方体の細溝20の底部を半導体エピタキシャル成長物で充填する場合に、細溝20の側面に{100}面を露出させる。細溝20内の各面から等速度でエピタキシャル成長し、ボイドの無い充填物22が得られる。充填物22の濃度や幅等を最適値に設定することで、充填物22内部が完全に空乏化するときには、ドレイン層12の充填物22間に位置する部分も完全に空乏化し、ドレイン層12内に広がった空乏層中の電界強度を一定にすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン以外の半導体で形成される半導体素子で使用可能なTEGを有する半導体装置およびその製造方法を提供する。

【解決手段】SBD部2aと、SBD部2aの電気特性を測定するためのTEG部3aと、を備えた半導体装置1aであって、SBD部2aは、n型のSiCドリフト層8と、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第1のショットキー電極13と、を有し、TEG部3aは、SiCドリフト層8の表面9を含む箇所に形成されたp型のイオン注入層18aと、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第2のショットキー電極21aと、第2のショットキー電極21aと電気的に接続され、SiCドリフト層8とは接触しないようにイオン注入層18a上に形成された電極パッド22と、を有する

(もっと読む)

少数キャリアの注入が抑制される炭化シリコン接合障壁ショットキーダイオード

【課題】接合障壁ショットキー(JBS)構造内のビルトインPiNダイオードの電流伝導を阻止する。

【解決手段】接合障壁ショットキー(JBS)一体構造が提供される。ダイオードのドリフト領域内に配置された炭化シリコン接合障壁領域を含む炭化シリコンショットキーダイオード、およびこの炭化シリコンショットキーダイオードを製造する方法も提供される。この接合障壁領域は、ダイオードのドリフト領域内にあって第1のドーピング濃度を有する第1の炭化シリコン領域と、ドリフト領域内にあって、第1の炭化シリコン領域とショットキーダイオードのショットキーコンタクトとの間に配置された第2の炭化シリコン領域とを含む。第2の領域は、第1の炭化シリコン領域およびショットキーコンタクトと接触する。第2の炭化シリコン領域は、第1のドーピング濃度よりも低い第2のドーピング濃度を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電気特性の耐圧のバラツキを抑制し、ESD耐量が高く、逆方向漏れ電流の少ない半導体装置を提供する。

【解決手段】本発明の半導体装置の製造方法は、ショットキーバリアを構成する第2導電型半導体層を形成する工程が、低濃度第1導電型半導体層の形成領域に矩形の開口をもつように、マスクパターンを形成し、前記矩形の長手方向に対して水平であって、前記矩形の短手方向に対して所定角をもつように、斜めイオン注入を行うことで、前記低濃度第1導電型半導体層内で前記第2導電型半導体層の短手方向底部が揃うように不純物を注入する工程を含む。

(もっと読む)

半導体整流装置

【課題】十分なサージ電流耐性を有し、かつ、信頼性の向上するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】第1導電型の第1のワイドバンドギャップ半導体領域16と、第1の半導体領域に挟まれて形成される第2導電型の第2のワイドバンドギャップ半導体領域18とを備えている。また、少なくとも一部が第2の半導体領域に接続され、第1の半導体領域に挟まれて形成され、第2の半導体領域より幅の狭い、複数の第2導電型の第3のワイドバンドギャップ半導体領域32を備えている。ここで、第3の半導体領域の長手方向を第1導電型の半導体層の表面に投影した方向が、第1導電型の半導体層の表面から裏面に向かう方向に対し、90±30度の角度を有している。また、第3の半導体領域の間隔が、第1導電型のワイドバンドギャップ半導体層の厚さをdとする場合に2d×tan18°以上である。

(もっと読む)

半導体装置、および、その製造方法

【課題】逆バイアス時の所望の耐圧を得つつ、周辺耐圧構造部の面積を小さくし、さらにより高破壊耐量にすることが可能な半導体装置を提供する。

【解決手段】半導体装置100は、第1導電型の半導体層と、半導体層上面の活性領域に第1の方向に延びて形成された複数の第2のトレンチと、複数の第2のトレンチに埋め込まれた、第2導電型の半導体からなる柱状の複数の埋込層と、活性領域を囲むように半導体層に形成されたリング状の第1のトレンチと、第1のトレンチの内面に形成された第1の絶縁膜と、第1のトレンチの内部に第1の絶縁膜を介して充填された導電性材料からなる導電性材料層と、少なくとも半導体層上面の活性領域に配置され、半導体層とはショットキー接合を形成し且つ前記複数の埋込層とはオーミック接合を形成する第1の電極膜と、半導体層下面に配置された第2の電極膜と、を備え、第1の電極膜と導電性材料層とは、同電位に設定され、逆バイアス時において、埋込層および半導体層の導電性材料層に囲まれた部分が空乏化する。

(もっと読む)

半導体装置およびその制御方法

【課題】リカバリ損失の低減が図れ、かつ、ノイズによるセルフターンオンが生じ難い構造の半導体装置を提供する。

【解決手段】ゲート電極8を深さの異なる第1、第2ゲート電極8a、8bを備えたダブルゲート構造とする。このような構造では、第1、第2ゲート電極8a、8bのうちの第1ゲート電極8aのみをオンさせることで、p型ベース領域3に対して反転層を形成しながらも、その反転層がn-型ドリフト層2とn+型不純物領域4とを繋ぐ深さまでは形成されないようにすることができる。この第1ゲート電極8aを過剰キャリア注入抑制ゲートとして機能させる。

(もっと読む)

半導体装置及びその製造方法

【課題】MPS構造又はJBS構造を有し、低い順方向降下電圧VF及び高い逆方向耐圧VRを両立させることが可能で、さらには、逆回復時間trrが短く、かつ、逆方向リーク電流IRが低い半導体装置を提供する。

【解決手段】n−型半導体層114と、n−型半導体層114の第1主面側表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114の第1主面側表面上におけるp+型拡散領域120が形成されていない領域に形成され、n−型半導体層114との間でショットキー接合を形成するバリアメタル層130と、バリアメタル層130を覆うようにn−型半導体層114の第1主面側全面に形成され、p+型拡散領域120との間でオーミック接合を形成するオーミックメタル層140と、p+型拡散領域120の直下にのみライフタイムキラーが導入された局所ライフタイム制御領域150とを備える半導体装置100。

(もっと読む)

半導体装置及びその製造方法

【課題】MPS構造又はJBS構造を有し、低い順方向降下電圧VF及び高い逆方向耐圧VRを両立させることが可能で、さらには、逆回復時間trrが短く、かつ、逆方向リーク電流IRが低い半導体装置を提供する。

【解決手段】n−型半導体層114と、n−型半導体層114の表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114及びp+型拡散領域120の表面上に形成され、n−型半導体層114との間でショットキー接合を形成し、p+型拡散領域120との間でオーミック接合を形成するバリアメタル層130からなる電極層と、p+型拡散領域120の直下にのみライフタイムキラーが導入された局所ライフタイム制御領域160とを備える半導体装置100。

(もっと読む)

半導体装置

【課題】トレンチゲート構成のパワートランジスタを有する半導体装置のオン抵抗を低減する。

【解決手段】トレンチゲート構成のパワーMIS・FETQにおいて、ソース用の半導体領域3の上面の層間絶縁層12の端部(位置P1)と上記ソース用の半導体領域3の上面の上記ゲート電極9Eから遠い端部(溝16の外周の位置P2)との間の長さをaとし、上記層間絶縁層12と上記ソース用の半導体領域3の上面との重なり部の長さ(位置P1から溝5aの外周の位置P3までの長さ)をbとすると、0≦b≦aとする。これにより、ソースパッドSPとソース用の半導体領域3の上面との接触面積が増大する上、ソースパッドSPとチャネル形成用の半導体領域4との距離を短くすることができるので、トレンチゲート構成のパワーMIS・FETQのオン抵抗を下げることができる。

(もっと読む)

炭化珪素半導体装置

【課題】微細化してもソース領域およびベース領域に繋がるコンタクト領域とソース電極とのコンタクトが十分に取れるようにする。

【解決手段】コンタクトホール12aの長手方向、つまりソース電極11とn+型ソース領域4およびp+型ボディ層5とのコンタクト領域の長手方向とn+型ソース領域4およびp+型ボディ層5の長手方向も直交させる。これにより、n+型ソース領域4やp+型ボディ層5それぞれのソース電極11へのコンタクト幅をコンタクトホール12aの幅分とすることが可能となる。このため、コンタクトを広く取ることが可能となる。これにより、素子を微細化してもn+型ソース領域4やp型ベース領域3に繋がるp+型ボディ層5とソース電極11とのコンタクトが十分に取れるようにすることが可能となる。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ特性を有する低オン抵抗で高耐圧の窒化物半導体素子を提供する。

【解決手段】基板上に設けられた第1導電型の窒化物半導体からなる第1半導体層5と、前記第1半導体層の上に設けられ、前記第1半導体層のシートキャリア濃度と同量のシートキャリア濃度を有する第2導電型の窒化物半導体からなる第2半導体層6と、を備える。前記第2半導体層の上には、前記第2半導体層よりも禁制帯幅が広い窒化物半導体からなる第3半導体層7が設けられる。前記第2半導体層に電気的に接続された第1主電極10と、前記第1主電極と離間して設けられ、前記第2半導体層に電気的に接続された第2主電極20と、をさらに備え、前記第1主電極と前記第2主電極との間において、前記第3半導体層および前記第2半導体層を貫通して前記第1半導体層に達する第1のトレンチの内部に絶縁膜33を介して設けられた制御電極30を備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置がSBDとして良好なショットキー特性を得ることができるようにする。

【解決手段】主面2a側がn型領域12とされると共に当該主面2aにp型領域15を形成してなる炭化珪素基板の主面2aのうち、p型領域15の表面15aのみを荒らす粗面化工程と、前記炭化珪素基板2の主面2aを洗浄液により洗浄する洗浄工程と、一種類の金属材料からなる一体の電極用金属層を、前記n型領域12の表面12a及び前記p型領域15の表面15aの両方に接触させるように、前記主面2aに形成する接続工程とを備える半導体装置の製造方法を提供する。

(もっと読む)

半導体装置およびDC−DCコンバータ

【課題】半導体装置の耐圧を向上させ、より高速のスイッチング動作を可能にする。

【解決手段】第1導電型の半導体層の第1主面側に選択的に設けられた第2導電型のベース領域と、ベース領域内に選択的に設けられた第1導電型の拡散領域と、拡散領域に接触しベース領域を貫通して半導体層にまで到達するトレンチ内に絶縁膜を介して設けられた制御電極と、半導体層の第1主面側から第2主面側の方向に延伸し、ベース領域とは離間して設けられた、少なくとも1つの第2導電型の第1の半導体領域と、隣り合うトレンチ間に、トレンチとは離間して設けられた第2導電型の第2の半導体領域と、拡散領域、半導体層、第1の半導体領域および第2の半導体領域に電気的に接続された第1の主電極と、半導体層の第2主面側に電気的に接続された第2の主電極と、を備え、第2の半導体領域は、ベース領域を貫通して半導体層にまで到達している。

(もっと読む)

61 - 80 / 230

[ Back to top ]