Fターム[4M104FF32]の内容

Fターム[4M104FF32]に分類される特許

81 - 100 / 230

高電圧印加のための改善された終端構造を備えるトレンチDMOSデバイス

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

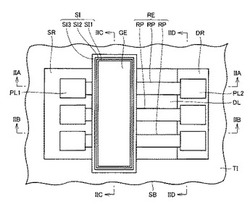

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

ヘテロ接合障壁領域を含む半導体デバイス及びその製造方法

半導体ウエハの処理方法と処理済の半導体ウエハ

【課題】不均質性が存在する半導体ウエハを処理して不均質性の影響を効率的に軽減できる処理技術を提供する。

【解決手段】半導体ウエハの表面を複数区域に分割し、分割された区域ごとに、特性低下要因の平均存在密度を特定する(S12)。分割された区域ごとに、その区域内の平均存在密度に基づいて、予め用意されている複数種類のマスクパターンのなかから1種類のマスクパターンを選択する(S15)。複数種類のマスクパターンは、複数の開口部を備えており、開口部が均一に分布しているとともに、種類によって開口比率が相違するという制約に従っており、平均存在密度が高いほど開口比率が高い種類のマスクパターンを選択する。分割された区域ごとに選択したマスクパターンの開口部から、異種物質を注入する(S21)。

(もっと読む)

半導体装置の製造方法

【課題】炭化ケイ素半導体装置を、表面構造形成工程を前に、裏面構造形成工程を後に実施する製造方法によって製造し、かつ、炭化ケイ素半導体装置の特性を確保する。

【解決手段】表面電極と、裏面電極とを備えた炭化ケイ素半導体装置の製造方法は、表面電極の材料となる表面電極材料層を半導体基板に接して成膜する表面電極材料層の成膜工程と、表面電極材料層をアニール処理する第1アニール工程と、を含む表面構造形成工程と、裏面電極層の材料となる裏面電極材料層を半導体基板に接して成膜する裏面電極材料層の成膜工程と、裏面電極材料層にレーザ照射を行って、裏面電極材料層と半導体基板とをオーミック接合させる第2アニール工程と、を含み、表面構造形成工程の後に行われる裏面構造形成工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーMOSトランジスタのサイズの縮小を図り、ソース・ドレイン間絶縁破壊電圧の低下を防止する。

【解決手段】P+型コンタクト層17をN+型ソース層18の底面の直下のP型ベース層13内に埋め込んで形成する。これによりP型ベース層13の表面にN+型ソース層18と並列にP+型コンタクト層17を形成する必要がなくなりN+型ソース層18の幅を狭くできる。また、N+型ソース層18の底面の直下のP型ベース層13内にP+型コンタクト層17を形成するため、従来に比して、P+型コンタクト層17のN+ソース層18に対する面積占有率を大きくできる。この結果、NPN寄生トランジスタがオンすることを妨げる事ができる。

(もっと読む)

整流素子およびその製造方法

【課題】定常損失を低減しつつ耐圧を向上することのできる整流素子およびその製造方法を提供する。

【解決手段】整流素子10は、ショットキー電極5、3と、カソード電極4との電位差が変化することにより、ショットキー電極5とカソード電極4との間に電流を流す状態と、ショットキー電極5とカソード電極4との間に存在するn-半導体層2を空乏層化することによって電流経路を遮断する状態とを選択可能である。上記ショットキー障壁φBn1が、0.68eV<φBn1<1.05eVという関係を満足し、かつ250℃の温度でもショットキー電極5とn-半導体層2とのショットキー接触を確保できる。上記ショットキー障壁φBn2は、1.06eV<φBn2という関係を満足する。

(もっと読む)

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた高耐圧半導体整流装置を提供する。

【解決手段】第1導電型のワイドバンドギャップ半導体基板と、ワイドバンドギャップ半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが20μm以上の第1導電型のワイドバンドギャップ半導体層と、ワイドバンドギャップ半導体層表面に形成される第1導電型の第1のワイドバンドギャップ半導体領域と、第1のワイドバンドギャップ半導体領域に挟まれて形成される第2導電型の第2のワイドバンドギャップ半導体領域と、第1および第2のワイドバンドギャップ半導体領域上に形成される第1の電極と、ワイドバンドギャップ半導体基板の下面に形成される第2の電極と、を備え、第2のワイドバンドギャップ半導体領域の幅が15μm以上であることを特徴とする半導体整流装置。

(もっと読む)

半導体素子

【課題】第一導電型領域と第二導電型領域とを交互に配置した並列pn層を備える超接合ショットキーバリアダイオードにおいて、表面電界を緩和し、漏れ電流の低減するショットキバリアダイオードを提供する。

【解決手段】半導体基板の第一と第二の主面にそれぞれ設けられた第一5、第二の主電極6と、第一主電極とショットキー接合を形成する第一の第一導電型領域3と、第二の第一導電型領域1aと第二導電型領域1bとを交互に配置した並列pn層1と、第二主電極6がオーミック接触する第一導電型低抵抗層4とを備え、第一の第一導電型領域3と並列pn層1が接し、並列pn1層と第一導電型低抵抗層4が接する半導体素子において、少なくとも第一の第一導電型領域の第一主面側に、内面に絶縁膜8を形成した溝が設けられている。

(もっと読む)

整流素子

【課題】定常損失を低減しつつ耐圧を向上することのできる整流素子を提供する。

【解決手段】ショットキー電極3は、SiCよりなるn-半導体層2とショットキー接触し、かつSiCよりなるp型半導体層5a,5bと電気的に接続している。ショットキー電極3とカソード電極4との電位差が変化することにより、ショットキー電極3とカソード電極4との間に電流を流す状態と、p型半導体層5a,5bに囲まれるn-半導体層2を空乏層化させてショットキー電極3とカソード電極4との間の電流経路を遮断する状態とを選択可能である。n-半導体層2とショットキー電極3との間のショットキー障壁φBn1が、0.68eV<φBn1<1.05eVであり、かつ250℃の温度でも、そのショットキー接触を確保できる。

(もっと読む)

半導体装置

【目的】活性部の端部に形成されたトレンチの電界強度を緩和しながら、少数キャリアを注入させることなく、耐圧の高い半導体装置を提供する。

【解決手段】TMBSダイオードの活性部21と耐圧構造部22において、活性部トレンチ12を取り囲むように端部トレンチ7が設けられ、アノード電極3の外周側の端部である活性端部19は、端部トレンチ7の内部に設けられた導電性のポリシリコン13と接している。端部トレンチ7と離間して端部トレンチ7を取り囲むようにガードトレンチ8が形成されている。またアノード電極3の外周部にアノード電極3とは離間してフィールドプレート9が設けられている。フィールドプレート9は、端部トレンチ7とガードトレンチ8の間のメサ領域18におけるn型ドリフト層2の表面の一部と、ガードトレンチ8の内部に形成されている導電性ポリシリコン13の両方と接している。

(もっと読む)

電子回路用の保護素子

集積半導体構成体を有する保護素子と、この保護素子の製造方法が記載される。この保護素子は、少なくも1つのショットキーダイオード(S)と少なくとも1つのツェナーダイオード(Z)とを有し、電流供給部と電子回路との間に接続される。ここでは前記ショットキーダイオード(S)のアノードが電流供給部と接続されており、前記ショットキーダイオード(S)のカソードが電子回路および前記ツェナーダイオードのカソードと接続されており、該ツェナーダイオードのアノードがアースと接続されている。ショットキーダイオード(S)は、トレンチ・MOS・バリア・ジャンクション・ダイオードまたはトレンチ・MOS・バリア・ショットキーダイオード(TMBSダイオード)またはトレンチ・ジャンクション・バリア・ショットキーダイオード(TJBSダイオード)であり、少なくとも1つのトレンチ・MOS・バリア・ショットキーダイオードと、ツェナーダイオード(Z)のアノードとして用いられるpドープ基板とを有する集積半導体構成体を含む。  (もっと読む)

(もっと読む)

炭化珪素半導体装置

【課題】工程数を増やすことなく特性バラツキを抑えた炭化珪素半導体装置を製造することが困難であるという問題があった。

【解決手段】本発明にかかる炭化珪素半導体装置は、第1導電型の炭化珪素半導体基板であるN型SiC基板1およびN型SiCエピタキシャル層2と、N型SiCエピタキシャル層2の表面に間欠的に形成された複数の凹み部10と、複数の凹み部10の各底面においてN型SiCエピタキシャル層2に形成された、第2導電型の半導体層であるP型領域5と、N型SiCエピタキシャル層2の表面上に選択的に形成されたショットキー電極6とを備え、複数の凹み部10の深さは、すべて等しい。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーボン膜の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化できるようにする。

【解決手段】オーミック電極5を形成するための金属層15の形成前にレーザ光の吸収効果の高いカーボン層14を形成しておき、その上に金属層15を形成してからレーザアニールを行うようにしている。これにより、金属層15を構成する金属がカーボン層14を構成する炭素(C)やn+型基板1を構成するシリコン(Si)または炭素と反応してオーミック電極5が形成されるため、カーボン層14を除去する必要がない。また、レーザアニール時にカーボン層14を用いているため、レーザ光の吸収率を高くすることができ、オーミック電極5のコンタクト抵抗の低抵抗化を十分に行うことが可能となる。したがって、カーボン膜14の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】n型SiC領域とp型SiC領域との両方と接触可能であり、かつ酸化による接触抵抗の増加を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、炭化珪素からなるn−SiC層12を準備する工程と、n−SiC層12の主表面上にソースコンタクト電極16を形成する工程とを備えるMOSFET1の製造方法である。ソースコンタクト電極16を形成する工程は、ソースコンタクト電極16となるべき導電体層をn−SiC層12の主表面上に形成する工程と、導電体層をソースコンタクト電極16とするため熱処理する工程とを含む。熱処理する工程の後、ソースコンタクト電極16の表面を酸素含有雰囲気に曝露するときのソースコンタクト電極16の温度を100℃以下にする。ソースコンタクト電極16を形成する工程の後、表面電極パッド27を形成する工程の前に、上記ソースコンタクト電極16の一方の主面上に形成された高抵抗層を除去する工程を含むことがより好ましい。

(もっと読む)

半導体装置、及びそれを用いた電力変換装置

【課題】電力変換装置に使われている従来のpn接合を使ったフライホイールダイオードは、ライフタイムを短く制御するため順方向電圧が大きく導通損失が大きい。また逆回復時には逆回復電流が大きくスイッチング損失が大きく、電力変換装置の損失が大きいという課題があった。

【解決手段】順方向電流が流れるときには順方向電圧の小さなpnダイオードで電流を流し、逆回復時には逆回復電流が小さなショットキーダイオードで逆回復させる。また、pnダイオードとショットキーダイオードの切り替え手段を持たせる。

【効果】フライホイールダイオードの順方向電圧を下げ、逆回復損失を低減できるので、損失の小さな半導体装置、更には電力変換装置を提供できる。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有する第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置とその製造方法

【課題】 電極と半導体基板の間の順方向特性を改善する技術を提供する。

【解決手段】 半導体装置100は、表面の少なくとも一部に複数の突出部6aが形成されている突出部領域6を有する半導体基板14と、複数の突出部6aの側面6dに形成されている電流方向異方性材料4と、突出部領域6上に形成されている電極2を備える。電流方向異方性材料4は平面方向のキャリア移動度が高いので、電極2と半導体基板14の間の順方向特性を改善することができる。

(もっと読む)

半導体素子の製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

半導体装置および電子機器

【課題】高速動作に適したN型層を用いたN型TFTを液晶容量と、蓄積容量の充電に用いる場合には、リーク電流特性に劣るN型層を蓄積容量に用いることとなり、電荷保持特性が低下するという課題がある。またP型層を用いたP型TFTを液晶容量と、蓄積容量の充電に用いた場合には、P型TFTがN型TFTと比べ移動度が低いことから高速動作が困難となり、TFTによるスイッチング特性が劣化するという課題がある。

【解決手段】N型TFT90をスイッチングに用い、P型電極層41を保持容量として用い、かつP延展部40と、N型ドレイン側延展部1tとを切り離すことなく形成した。P延展部40と、N型ドレイン側延展部1tとの間には段差はなく、コンタクトホール94を形成するためのエッチング工程を均一な層厚を備えた第1層間絶縁層4に対して行うことができ、エッチングむら等による電気抵抗の増加を防止することが可能となる。

(もっと読む)

81 - 100 / 230

[ Back to top ]