Fターム[4M104FF32]の内容

Fターム[4M104FF32]に分類される特許

41 - 60 / 230

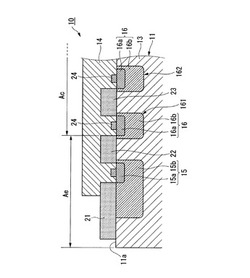

ショットキーバリアダイオード

【課題】ジャンクションバリアショットキー構造をもつダイオードにおいて、ショットキー接合部の逆サージ耐量を改善することが可能なショットキーバリアダイオードを提供する。

【解決手段】ガードリング層15に隣接した第二半導体層161と、この第二半導体層161に隣接する第二半導体層162との間に跨るように、基板11の中心領域Acにおいて第三絶縁層23が形成されている。即ち、第二半導体層161と第二半導体層162との間で、基板11の一面(一方の主面)11aに露呈された第一半導体層13を覆うように第三絶縁層23が形成される。これによって、第三絶縁層23は、第二半導体層161と第二半導体層162との間で基板11の一面11aに露呈された第一半導体層13と、金属層14との間を電気的に絶縁する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】SiC半導体装置において、不純物添加工程や表面保護膜形成におけるプロセス条件のばらつきがあっても、簡便に逆方向耐圧に大きな影響を与えないターミネーション構造(接合終端構造)を提供する。

【解決手段】素子の外周端部に、第1導電型の耐圧維持層および有限長さの前記第1導電型とは異なる第2導電型の領域からなる接合終端構造を備えたSiC半導体素子であって、前記接合終端構造の一部において、第1の方向である層方向に対して均一ではなく、前記接合終端領域の内側端であって前記素子の外周端から前記接合終端領域の外側端に向かって、前記第1導電型領域の不純物濃度が空間的に変調され、不純物濃度が徐々に減少する傾向を持って形成された接合終端構造を有することを特徴とするSiC半導体素子。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤボンディングの際にオーミック電極が破壊されない炭化珪素半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る炭化珪素半導体装置は、炭化珪素基板1と、炭化珪素基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に形成されたp型不純物領域3と、p型不純物領域上に形成されたp型オーミック電極4と、p型オーミック電極4を覆うようにn型炭化珪素層2上に形成されたショットキー電極5と、を備え、p型オーミック電極4はp型不純物領域3の表面に設けられた凹部3a内に形成されており、p型オーミック電極の上面はn型炭化珪素層の表面2aよりも低い位置にある、ことを特徴とする。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

複合半導体装置

【課題】SJ−MOSFETと、このSJ−MOSFETの内蔵ボディダイオードと並列接続するショットキーバリアダイオードとを備える構成を、安価に、低導通損失と低リカバリー損失特性を有しソフトスイッチング方式の回路技術に適する複合半導体装置にすること。

【解決手段】超接合構造を有するMOS型半導体装置31と、該MOS型半導体装置31とは逆並列に接続されるワイドバンドギャップダイオード32とを有する複合半導体装置において、前記MOS型半導体装置31の定格電流における前記ワイドバンドギャップショットキーバリアダイオード32の順方向電圧降下より前記MOS型半導体装置31の内蔵ボディダイオードの順方向電圧降下を高くする抵抗値を有する抵抗部10が前記MOS型半導体装置31に直列接続されている複合半導体装置とする。

(もっと読む)

ショットキーバリア型半導体装置

【課題】低バイアス領域からリーク電流IRの低減効果を得ることのできるショットキーバリア型半導体装置を提供する。

【解決手段】表面に第1導電型を有する第1の半導体層2を有する半導体基板と、第1の半導体層の表面から所定の深さに設けられ、第1導電型の半導体層よりも低濃度の第1導電型を有する第2の半導体層3と、第1の半導体層の表面から所定の深さに配設されたジャンクションバリアとして第2導電型を有する複数の第3の埋め込み半導体層5と、第1の半導体層の表面で第3の埋め込み層を囲むように環状に形成された、第2導電型を有するガードリング4と、第1の半導体層およびガードリングに接するように配置された金属層6を具備したショットキーバリア型半導体装置であって、第2の半導体層の比抵抗が第1の半導体層の比抵抗よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体整流装置

【課題】少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

ショットキーバリア型半導体装置

【課題】リーク電流IRの低減を維持しつつ耐圧の向上をはかることのできるショットキーバリア型半導体装置を提供する。

【解決手段】ショットキーバリア型半導体装置において、ガードリング4の外側で、第1の半導体層の表面から所定の深さに配設されたジャンクションバリア5としての埋め込み半導体層を具備する。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、パワー半導体素子を提供する。

【解決手段】半導体基材内に第1の伝導型のドリフト領域2と、半導体基材内にドリフト領域2に隣接して配置され半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3の間に配置された蓄積誘電体4と、基材領域8と、基材領域8から分離され蓄積誘電体4に隣接するドレイン領域5と、基材領域8によりドリフト領域2から分離されるソース領域9と、ゲート誘電体16により半導体基材から絶縁されソース領域9からドリフト領域2に到るまで基材領域8に隣接して伸びたゲート電極15と、ドレイン領域5と接したドレイン電極11と、ドレイン領域5と相補的にドープされた半導体領域27とを含み、半導体領域27はドレイン電極11とドリフト領域2の間に配置されドレイン電極11に隣接する。

(もっと読む)

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

炭化珪素ジャンクションバリアショットキーダイオードおよびその製造方法

【課題】炭化珪素ジャンクションバリアショットキーダイオードの製造において、ハードマスクを使用せずに、pウェル上に選択的にp+領域を形成し、また金属電極とp+領域とコンタクト抵抗を低減する。

【解決手段】n型のエピタキシャル層2の上部全体に高温イオン注入によってp+領域4aを形成し、当該p+領域4aを選択的にエッチングしてp+領域4a下のn型領域を部分的に露出させることにより、そのn型領域の上面より上方へ突出したp+半導体凸部4を形成する。アノード電極は、上記のn型領域の露出した部分およびp+半導体凸部4を覆うように形成される。

(もっと読む)

ショットキーバリア型半導体装置

【課題】低電流から大電流に渡り低順方向電流電圧特性を得るショットキーバリア型半導体装置を提供する。

【解決手段】プレーナ構造とJBS構造を1チップ内で並列接続することで、低電流領域での順方向電圧特性にはJBS構造、大電流域ではバリアハイトが0.70eVより高いショットキーメタルから構成されたガードリング構造(プレーナ構造)が作用する。

(もっと読む)

半導体装置、及びそれを用いた装置

【課題】信頼性を向上させることができる半導体装置,半導体装置を用いた回転電機または車両を提供する。

【解決手段】ショットキ接合と、pn接合を備える半導体装置であって、pn接合は高濃度P型拡散層5とN型拡散層4で形成され、低濃度P型拡散層6と金属電極7により、ショットキ接合が形成され整流領域のpn接合部の降伏電圧を、前記ショットキ接合及びガードリング部Z2のpn接合より低くすることを特徴とする。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

電力用半導体装置

【課題】JBSであってもサージ電流による温度上昇とその正帰還により素子破壊に至る場合があった。

【解決手段】n型のSiC基板と、SiC基板の第一主面に形成され、SiC基板よりも不純物濃度の低いn型SiCドリフト層と、ドリフト層に形成されたp型SiCの第一の半導体領域と、第一の半導体領域の表層側に形成され、第一の半導体領域よりも不純物濃度が高濃度であるp型SiCの第二の半導体領域と、ドリフト層の表面に形成され第一の半導体領域とショットキー接続し、第二の半導体領域とオーミック接続するショットキー電極と、ショットキー電極の表面に形成されたアノード電極と、アノード電極の表面で、第一の半導体領域の直上に形成され、上面から見て第一の半導体領域の領域を含むように第一の半導体領域よりも広い面積に形成されたファーストボンドと、SiC基板の第二主面に形成されたカソード電極とを備えている。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体装置の製造方法

【課題】炭化珪素の半導体層の表面に発生するステップバンチングを抑制する。

【解決手段】半導体装置の製造方法は、炭化珪素のエピタキシャル層14にドーパントを導入するドーパント導入工程と、エピタキシャル層14の表面にカーボン膜24を形成するカーボン膜形成工程と、カーボン膜24が残存した状態でエピタキシャル層14をアニール処理するアニール処理工程とを備える。カーボン膜形成工程では、シリコン、窒素及び酸素の群から選択される少なくとも1種類以上の原子が原料に含まれる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いゲート絶縁膜を備えたSiC半導体装置を提供する。

【解決手段】8度以下のオフ角度を有する炭化珪素基板(1)と、この基板上に形成された第1導電型の第1炭化珪素領域(2)と、この領域の表面に形成された第2導電型の第2炭化珪素領域(3)と、この領域の表面に形成され、不純物濃度が第2の炭化珪素領域と同程度に調整された第1導電型の第3炭化珪素領域(4)と、この領域の表面に選択的に形成された第1導電型の第4炭化珪素領域(5)と、第2炭化珪素領域の表面に形成された第2導電型の第5炭化珪素領域(6)と、第1炭化珪素領域から第3炭化珪素領域の少なくとも端部までを覆うように形成されたゲート絶縁膜(7)と、この上に形成されたゲート電極(8)とを具備し、第3炭化珪素領域の表面における、第3と第4炭化珪素領域の境界面は、オフ角度方向と90°以外の角度で交差するように形成されている。

(もっと読む)

41 - 60 / 230

[ Back to top ]